SRAM 单元的单粒子效应三维敏感区形状参数模拟仿真方法

王玉才,刘 艳,曹荣幸,李红霞,刘 洋,郑 澍,韩 丹,薛玉雄

(扬州大学 电气与能源动力工程学院,扬州 225127)

0 引言

静态随机存储器(SRAM)作为信息存储核心单元,在空间环境中容易发生单粒子翻转(SEU),可造成存储器状态改变、数据丢失等危害[1]。近些年,随着集成度提高,器件SEU 临界电荷降低,纳米器件的临界电荷已经小于1 fC,导致器件对单粒子效应(SEE)越来越敏感。

长期以来,对SEE 的研究主要集中在地面模拟试验,包括地面加速器试验和脉冲激光模拟试验。地面加速器试验主要是利用重离子加速器进行SEE试验,目前手段已经很成熟,但是重离子试验提供机时相对较少,并且试验费用高[2];脉冲激光模拟试验是利用现代激光与光电技术实现诱发星用器件类似的SEE,具有试验评估快速、成本低和周期短等优势[3]。

此外,模拟仿真也是评估器件SEE 的重要手段。解磊等[4]用计算机辅助设计(TCAD)仿真方法,研究了65 nm 体硅工艺下,商用6 管SRAM 和高密度设计的DICE 结构SRAM 的中子SEE。李振涛等[5]通过二维数值拟合得到了SEE 瞬态电流脉冲并将其代入电路模拟软件HSPICE 中进行SRAM 存储单元SEU 的电路模拟。姚思远等[6]基于 0.18 μm CMOS 工艺的SRAM 单元进行电路仿真,得到该单元的翻转阈值。目前,未见SRAM 单元的敏感区形状参数仿真研究报道,计算敏感区形状参数可以判断器件内部敏感位置分布。

计算敏感区形状参数可以判断器件内部敏感位置分布,但目前未见SRAM 单元的敏感区形状参数仿真研究报道。为此,本文提出一种SRAM 单元的SEE 三维敏感区形状参数模拟仿真研究方法,可以获得器件三维敏感区形状参数大小,为研究器件内部单粒子电荷收集机制提供思路。

1 模拟仿真方法

本文模拟仿真方法的总体思路为:根据SRAM单元核心器件MOSFET 的尺寸结构和工艺参数,通过TCAD 对器件进行三维结构建模。再使用模型网格划分工具对器件的三维结构模型进行网格划分,生成网格化的器件结构并开展器件电学特性仿真。通过调整器件沟道、材料组成以及掺杂浓度等实现器件电学模型的优化,然后对三维器件电学模型进行SEE 瞬态电流仿真。为了能够精确掌握SEE 规律以及整个器件单元的SEE 敏感区形状参数,仿真时设置辐射粒子从不同方向、不同位置入射器件单元,得到对应的单粒子瞬态电流。通过集成电路模拟程序(SPICE)网表文件构建6 管SRAM电路模型结构,再将不同粒子入射条件下的单粒子瞬态电流作为故障电流源注入SPICE 模拟电路仿真结构中,观察电路单元的输入输出,分析SRAM单元是否发生SEU,最终以SRAM 单元SEU 的最小电荷量作为临界电荷,并通过分析敏感入射点的位置参数得到SRAM 单元SEE 敏感区形状参数。

1.1 器件结构及仿真参数

本文构建了N 型和P 型MOS 晶体管的三维仿真结构,相比于二维仿真结构,能够更好地模拟器件三维敏感区形状参数。三维器件长度为0.25 μm,宽度为0.1 μm,高度为0.2 μm。漏源位于器件的两侧,长度均为0.05 μm,栅长为0.065 μm,栅宽为0.018 μm,栅氧化层的厚度为0.002 μm。N 型和P 型MOS 晶体管掺杂结构模型如图1 所示[7]。

图1 MOS 晶体管掺杂结构模型Fig.1 Doped structure model of MOS transistor

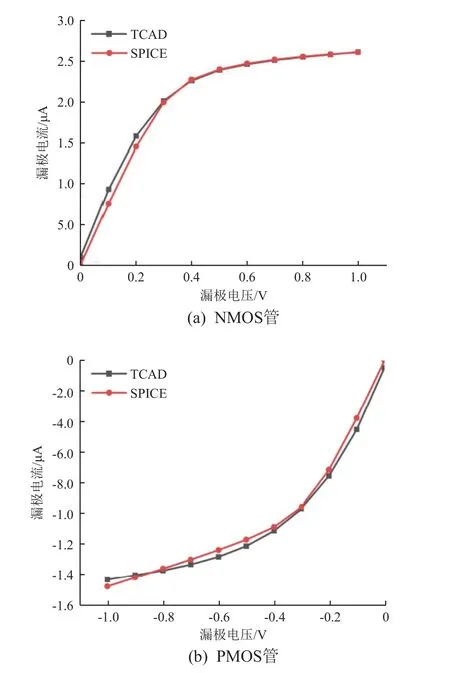

在构建好三维器件结构后,定义器件电学仿真的物理模型,选用的物理模型有SRH 复合模型、CVT 集成模型[8]、Auger 复合模型和碰撞离化模型[9]。接触材料定义为肖特基接触,仿真的数值计算方法使用Newton 迭代法。最后对N 型和P 型三维MOS 晶体管进行电学特性仿真,通过施加漏极电压0.05 V 和在0~1 V(PMOS 中为0~-1 V)间扫描栅极电压获得器件转移特性曲线,如图2 所示;通过施加不同的栅极电压(Vgs)0.5 V、1 V、1.5 V,以及在0~1 V(PMOS 中为0~-1 V)间扫描漏极电压获得输出特性曲线,如图3 所示。从转移特性曲线可以看出器件的阈值电压为0.3 V,与已报道的65 nm 工艺器件的试验测量结果相近[10],验证了所构建器件结构模型的有效性。

图2 MOS 晶体管转移特性仿真曲线Fig.2 Transfer characteristic simulation curves for MOS transistors

图3 MOS 晶体管输出特性仿真曲线Fig.3 Output characteristic simulation curves for MOS transistors

在器件电学模型基础上,通过TACD 定义器件内物理模型和入射粒子参数,构建器件重离子SEE 模型。模型构建是通过TCAD 中器件仿真器Atlas 实现,其中的指令“singleeventupset”可以定义重离子入射器件后因碰撞离化产生的电子-空穴对的空间和时间分布信息。

在仿真中,重离子的线性能量转移(LET)可用线性电荷沉积(LCD)描述,LCD 的单位为pC/μm。LET 值与LCD 值之间存在比例关系LCD=LET×ρ/EI,其中:ρ 为半导体材料密度,Si 材料为2.33 g/cm3;EI为产生1 个电子-空穴对所需要的能量,Si 材料为3.6 eV[11]。得到在Si 材料中LET=1 MeV·cm2/mg所对应的LCD=0.010 3 pC/μm。单粒子模块定义的信息:粒子LET 值1.5 MeV·cm2/mg,即LCD 为0.015 45 pC/μm,可 通 过 指 令“pcunits b.density=0.015 45”实现。此外还定义了入射粒子的径迹半径、入射深度、入射位置、电荷生成脉冲的特征时间等参数:粒子的径迹半径为0.01 μm,深度为贯穿器件,角度为垂直入射,偏置电压为1 V,生成电荷脉冲的峰值时间为4 ps,电荷脉冲的特征时间为2 ps。最终仿真得出NMOS 管和PMOS 管的漏极瞬态电流曲线[12]如图4 所示。

图4 MOS 晶体管漏极瞬态电流曲线Fig.4 Drain transient current curves for MOS transistors

1.2 电路级SRAM 单元仿真

基于TCAD 对器件进行三维建模的转移和输出特性仿真,利用SPICE 模型优化软件UTMOST提取MOS 管的BSIM4 模型参数,主要参数有阈值电压、迁移率退化系数以及通道长度的体电荷效应系数等[13],并利用TCAD 器件仿真结果对SPICE 模型进行校准优化。晶体管的TCAD 模型与SPICE 模型转移特性曲线和输出特性曲线对比分别如图5 和图6 所示,由图可见,SPICE 模型结果与TCAD 器件仿真结果符合较好。

图5 MOS 晶体管TCAD 模型与SPICE 模型转移特性曲线对比Fig.5 Comparison of transfer characteristic curves between TCAD model and SPICE model of MOS transistor

图6 MOS 晶体管TCAD 模型与SPICE 模型输出特性曲线对比Fig.6 Comparison of output characteristic curves between TCAD model and SPICE model of MOS transistor

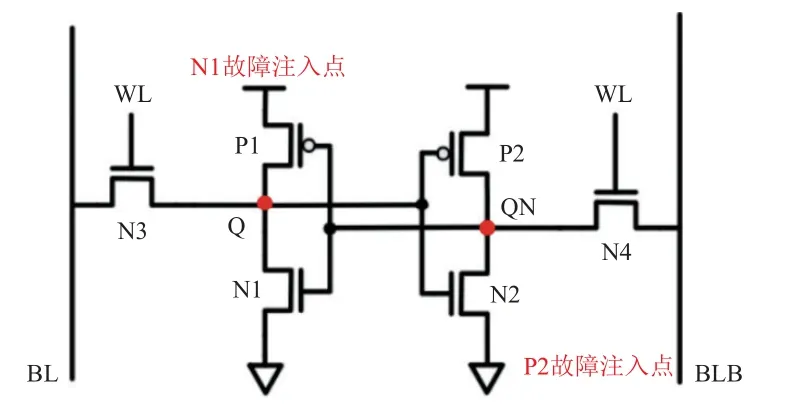

基于上述方法建立的MOS 管SPICE 模型和典型的6 管SRAM 电路模型(如图7 所示),进一步构建SRAM 器件电路级模型。SRAM 存储单元有两个敏感区域,分别处于截止状态的上拉 PMOS 管和下拉 NMOS 管的漏区,SRAM 存储单元的状态由 P1、P2、N1、N2 共同决定,N3、N4 管通过字线WL 控制 SRAM 单元的读写,在研究SEU 机理中一般不予考虑[14]。

图7 典型6 管SRAM 电路模型Fig.7 Typical 6-T SRAM circuit model

利用TCAD 对器件SEE 进行仿真获得瞬态脉冲结果,通过自定义电压源和电阻来模拟瞬态脉冲电流,注入到存储单元的敏感节点,即关断的MOS 管漏区,从而仿真SRAM 器件的SEU。当Q 点施加电压1 V,QN 点施加电压0 V 时,N1 与P2 关断,故障电流注入点为N1 和P2 的漏极,即Q 点和QN 点。当Q 点施加电压0 V,QN 点施加电压1 V 时,N2 与P1 关断,故障电流注入点为N2和P1 的漏极,即QN 点和Q 点[15]。

2 仿真结果与分析

2.1 器件级SEE 仿真

本文仿真对象为三维结构器件,粒子从3 个方向垂直入射MOS 管。粒子沿着x方向入射时,在yz面取10×12 个网格状入射点;粒子沿y方向入射时,在xz面取5×12 个网格状入射点;粒子沿z方向入射时,在xy面取5×10 个网格状入射点;一共230个入射点,间隔均为0.02 μm。入射粒子径迹半径均为0.01 μm;粒子LET 值的选取从0 MeV·cm2/mg开始,以0.3 MeV·cm2/mg 的步长增加,得到不同粒子入射条件下的器件单粒子瞬态电流,并导入SPICE电路模型中进行电路级仿真分析,观测SRAM 单元是否翻转。经过多次仿真发现,LET 值增大至1.5 MeV·cm2/mg 时,器件发生SEU。因此,本文以典型LET 值为1.5 MeV·cm2/mg 的重离子为例,在不同粒子入射位置下分别开展器件SEE 仿真,得到每个入射位置的单粒子瞬态电流曲线。

2.2 临界电荷和敏感区形状参数模拟

将器件级SEE 仿真获得的不同入射位置的单粒子瞬态电流数据注入敏感节点,通过SRAM 的翻转情况判定SEE 临界电荷和敏感区形状参数。

2.2.1 典型位置点分析

以NMOS 管为例,先选取x、y、z三个不同方向上导致SRAM 发生翻转的典型位置点进行分析,分别是——x方向:入射位置为(0.00, 0.02,0.06),出射位置为(0.10, 0.02, 0.06);y方向:入射位置为(0.02, 0.00, 0.06),出射位置为(0.02, 0.20, 0.06);z方向:入射位置为(0.02, 0.06, 0.00),出射位置为(0.02, 0.06, 0.25)。对仿真所得的瞬态电流曲线进行积分,得到的收集电荷量分别为1.3 fC、4.12 fC 和2.81 fC,电路级仿真结果如图8(a)、(b)、(c)所示。可以看到,单粒子瞬态造成了SRAM 逻辑状态的翻转,原本P2 管漏极的低电平变为高电平、N1 管处漏极的高电平变为低电平。说明这3 个入射位置的电荷收集量超过器件的临界电荷量,属于器件敏感位置。当入射位置为(0.10, 0.18, 0.00)、出射位置为(0.01, 0.18, 0.25)时,对瞬态电流曲线进行积分,得到的收集电荷为0.53 fC,电路级仿真结果如图8(d)所示,可以看到,单粒子瞬态只造成了存储数据的扰动但并未发生翻转,原本P2 管漏极和N1 管处漏极的电平未发生改变[16]。说明该入射位置的电荷收集量未超过器件的临界电荷量,属于器件不敏感位置。图8 中V(Q)、V(QN)分别代表图7中两故障电流注入点Q 点和QN 点的电压。

图8 SRAM 单元节点SEU 仿真结果Fig.8 Simulation results of SEU on SRAM unit node

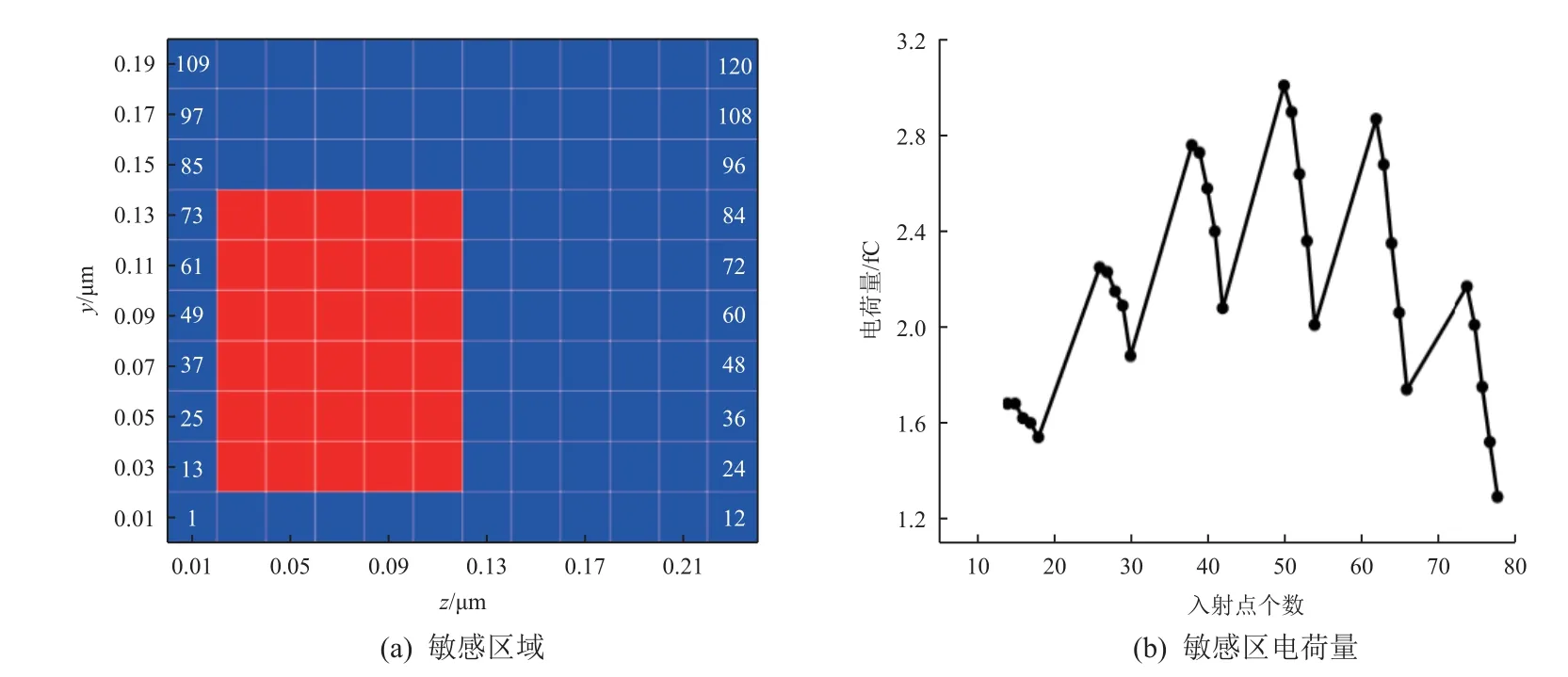

2.2.2 NMOS 管全向模拟

对NMOS 管(参见图1(a))的230 个入射位置网格点进行单粒子瞬态电流仿真,图9(a)、10(a)、11(a)中每个方格代表一个入射点。仿真中,通过重离子诱发单粒子得到瞬态电流,将不同粒子入射条件下的瞬态电流作为故障电流源注入SPICE 模拟电路仿真结构中,观察电路单元的输入输出,分析SRAM 单元是否发生SEU 现象;将瞬态电流曲线进行积分得到收集电荷量,如图9(b)、10(b)、11(b)所示。分析获得该NMOS 管的SEU 临界电荷为1.27 fC。根据有翻转现象的入射点坐标进一步分析出敏感区范围,如图9(a)、10(a)、11(a)所示:红色区域的电荷收集量超出临界电荷量,蓝色区域的电荷收集量未超出临界电荷量,即红色区域涵盖范围为敏感区域。最终得到x方向的敏感区域范围为0.01~0.09 μm,y方向的敏感区域范围为0.03~0.13 μm,z方向的敏感区域范围为0.03~0.11 μm。当瞬态电流的收集电荷量小于1.40 fC 时,单粒子瞬态只造成了存储数据的扰动但并未发生翻转;而电荷量大于1.40 fC 时,单粒子瞬态造成了存储数据的翻转。

图9 NMOS 管SEE 仿真(x 入射方向)Fig.9 Simulation of SEE for NMOS transistor (x direction of incidence)

图10 NMOS 管SEE 仿真(y 入射方向)Fig.10 Simulation of SEE for NMOS transistor (y direction of incidence)

图11 NMOS 管SEE 仿真(z 入射方向)Fig.11 Simulation of SEE for NMOS transistor (z direction of incidence)

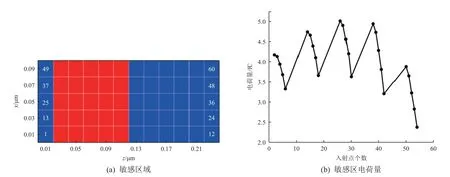

2.2.3 PMOS 管全向模拟

同理,对PMOS 管(参见图1(b))的230 个入射位置的单粒子瞬态电流曲线进行积分,得到不同入射位置的电荷收集量。分析获得该PMOS 管临界电荷量为1.40 fC。PMOS 管比NMOS 管临界电荷量大,其原因是PMOS 管的电子和空穴的迁移率不同,导致PMOS 管漏极产生的电流比NMOS 管的小;同时,当横向寄生三极管导通后,由于 NMOS 管收集到的电流比PMOS 管大得多,NMOS 管中的寄生NPN 晶体管比PMOS 管中的寄生PNP 晶体管产生的电流大,从而使电路对SEU 的敏感性增强,电荷翻转阈值更低[17-18]。

通过对SRAM 的SEU 仿真情况分析,得出器件中PMOS 管的敏感区形状参数:x方向的坐标范围为0.01~0.09 μm,y方向的坐标范围为0.03~0.09 μm,z方向的坐标范围为0.03~0.07 μm,其敏感区也在靠近漏极的位置。

3 结束语

本文利用TCAD 器件级仿真和SPICE 电路级仿真相结合的方式,对SRAM 单元的三维敏感区形状参数开展了模拟仿真研究。对构建的65 nm SRAM 器件单元进行了单粒子敏感区形状参数的模拟仿真。通过不同方向、不同位置的单粒子瞬态电荷收集量,判断电路仿真是否发生逻辑状态翻转,获得器件SEU 临界电荷量,进而得到SEE 三维敏感区形状参数。此研究可为SRAM 器件的空间应用提供数据支撑,以及为其辐射防护设计提供理论依据。

为了更精确地获得器件三维敏感区形状参数,后续计划开展以下研究:

1)针对SRAM 单元器件进行3 个方向的脉冲激光试验和重离子微束试验,对器件的不同区域进行SEE 敏感区的测试,进而获得敏感区的分布,分析器件的三维敏感区形状参数;

2)通过试验结果与仿真结果对比,验证本文提出的SEE 三维敏感区形状参数仿真方法的准确性。

——以赣州市龙南县为例