一种U波段功率放大器的研制

摘 要:本文设计并分析了一种基于波导空间功率合成技术的U波段(40—60 GHz)功率放大器,采用E面T型结功率分配/合成结构和波导-微带转换实现宽带、低损耗的四路功率合成网络,建模仿真优化后加工制造实物,在全频段内测得无源背靠背损耗小于1.3 dB,与仿真结果吻合较好。装配4片某国产放大芯片后实测得在40—60 GHz内饱和输出功率大于37.8 dBm(6.03 W),其中在40—54 GHz内输出功率优于40 dBm(10 W),与输入功率相比,增益为7 dB左右,合成效率超过了80%。

关键词:固态功率放大器;U频段;宽频带;低损耗;E面T型结

中图分类号:TN73"" 文献标志码:A""" 文章编号:1673-5072(2024)05-0546-07

更高频率和更高功率成为当前微波技术发展的重要研究方向,但受到器件工艺技术、阻抗匹配以及散热等方面的限制,单片固态功率器件在高频下输出功率不足。毫米波功率放大器最大输出不过数瓦,尤其是超宽带放大器的可选择性更少,性能稳定性不佳,难以满足更高频率和功率的应用需求。宽带高功率等性能指标在短期内很难得到提升,因此功率合成技术是目前实现单体高功率输出的有效手段。

通过对现有合成技术进行总结发现平面传输线的损耗随着频率升高而增加,波导内功率合成技术的损耗更低,而且功率容量更大。受高频影响,同轴波导合成容易激发高次模,降低效率。径向波导合成效率高,理论上可实现百路以上合成,但结构复杂,维修性较差[1]。魔T结构端口驻波较好,隔离度高,但是路数越多结构越复杂[2-3]。矩形波导E-T二进制合成结构简单,功率容量高,适合2~64路合成[4-7]。

功率合成技术的效率越高,输出功率越大。合成级数对效率影响很大,级数越多效率越低,因此选用单片功率更高的芯片更有利于合成效率。合成结构的设计加工同样影响着效率,对每一步的结构设计兼顾回波损耗和插入损耗2个指标。回波损耗越大,从放大器芯片传递过来的信号被反射回去的越少。插入损耗越小,合成过程中能量损耗就越小,转化的热能也越少。

现有的U波段功率分配/合成器结构复杂、工作带宽较窄,影响了功率放大器的输出效果,并且相对带宽越宽,功分/合成器的设计和加工难度就越大。本文研制了一种基于矩形波导E-T功率分配/合成结构的四路U波段功率放大器,芯片与波导采用波导-微带转换实现低插损互联,芯片选用4片某国产GaN宽带放大器,并进行了无源合成结构测试及有源功率测试。

1 功率合成网络

1.1 四路功率分配/合成结构

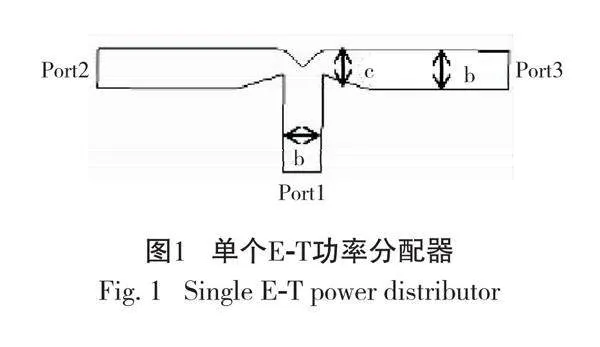

E面T型(E-T)结为有耗三端口网络,可以将多个该结构进行N级级联实现2N路功率分配与合成,在高频功率合成放大器中使用较为广泛。如图1所示的单个E-T结左右对称,信号从端口Port1输入,经E-T结构分配为两路等幅反相信号输出。同理,两路等幅反相信号从端口Port2和Port3输入,经E-T结构矢量合成为一路信号输出,背靠背连接功率分配器和合成器构成合成网络。T型接头由全高波导和减高波导构成,由于信号传输方向改变引入寄生高次模式,通常需要在连接处加入匹配结构,例如膜片、椎体等[7-8],但其装配精度要求高,采用简单的切角处理也能消除E-T接头处和传输方向转变的不连续性。输出端阻抗变换将减高波导转换到标准的全高波导,利于连接其他波导器件。

本设计工作频段为U频段(40—60 GHz),相对带宽为40%,选用标准WR19矩形波导(宽边长度a=4.775 mm,窄边长度b=2.388 mm,截止频率为31 GHz,通用波段为39.2—59.6 GHz)。四路功率分配器结构如图2所示,由两级3个E-T结构成,输入端口Port1为标准WR19矩形波导,输出端口Port2—Port5为WR19减半波导。为了便于波导腔体的铣削加工,对输出端口Port2—Port5进行半径为0.5 mm的倒圆角处理。由于频率越高,矩形波导口径越小,多级阶梯阻抗变换段的加工精度要求就更高,接头处切割成矩形产生的误差也偏高,因此,本文采用斜切面渐变将减高波导转换到标准波导,接头处切割成三角形。

使用三维电磁仿真软件对该结构进行仿真优化,首先对单个功分器的几何参数进行扫参分析,发现三角形切角和斜切面渐变的大小对反射系数、谐振点有较大影响,再对影响较大的参数进行优化,使得4个端口S21、S31、S41、S51在3 dB附近,回波损耗大于20 dB。将3个功分器级联起来构成四路功分器,优化该结构,优化后结果如图3所示。在40—60 GHz工作频段内,四路功率分配器的回波损耗大于20 dB,说明输入端口Port1的匹配性较好;S21、S31、S41、S51的幅度值均在理论值(6.02 dB)附近,幅度差异在0.1 dB以内;S21与S41相位值几乎一致,S31与S51相位值几乎一致,因此图3(c)中出现曲线重合,S21与S31、S41与S51的相位差均在理论值(180°)左右,相位差异在0.1°以内,说明输出端口Port2—Port5的幅度、相位一致性较好,利于矢量合成效率最大化。

1.2 波导-微带转换结构

通常功放芯片的输入输出端口均连接微带线,因此需要对波导与微带2种传输媒介进行转换设计。矩形波导-对脊鳍线-微带转换[9]具有结构紧凑、易于批量生产等优点,但易产生谐振模式影响功放性能;矩形波导-脊波导-微带转换[10-11]适用于超宽频带,但脊波导与波导传输方向平行,体积增大,且脊波导与微带接触点加工复杂,很小的差距就会造成很大的损耗;矩形波导-微带探针转换[4-6]插入损耗小、体积小、机械结构简单,具有良好的重复性。通过对比分析3种转换结构,本文选用矩形波导-微带探针转换,能同时兼顾性能和机械制造。

根据探针插入方向,波导-微带探针转换结构分为E面探针和H面探针,本文采用结构更紧凑的E面探针转换,如图4所示。波导宽边中心处开一个矩形窗,梯形微带探针从窗口插至矩形波导内电场最强处,探针激励的电流越多,耦合到50 Ω微带线上的信号越多,此时探针中心距离波导短路面为四分之一波长左右,并垂直于波导传输方向。在上一节中输出端口为标准波导减半,阻抗降低,仍高于微带线阻抗。信号从波导模式转换为微带模式,直接转换的不连续性会造成结构失配,大量能量被反射回去,因此需要对波导和微带进行匹配设计,即阻抗变换。普遍的做法是在微带探针和50 Ω微带线之间连接两段甚至多段匹配枝节,类似于阶梯阻抗变换,但是匹配枝节的宽度通常较小,增加了机械加工难度。本文在矩形窗下方开一个小矩形窗,与基板上面的一小段50 Ω微带线构成阻抗变换器,使微带探针阻抗变换至标准微带阻抗。匹配设计采用波导处理方式,与微带枝节设计相比,降低了加工可能出现的误差,且增加了功率容量。

介质基板的材料特性对电磁波信号传输影响很大,且趋肤效应在高频中更为明显,选材的不适会额外增加传输损耗。综合性能和价格因素,本文介质基板选用Rogers 5880(介电常数2.2),散热效果佳,损耗小,价格便宜且易加工。介质基板厚度为0.254 mm,微带厚度为35 μm。

矩形窗的尺寸不能过大或过小,宽度略大于介质基板宽度,高度过高,电路中出现谐振导致能量反射,高度过低,不能完全阻止高次模式的传输。最理想的状态是仅通过微带工作模式(准TEM模)。

扫描分析波导-微带转换结构的参数,微带探针尺寸、小矩形窗尺寸、探针到短路面距离对转换结构的工作带宽、回波损耗影响最大,对此进行相应的优化,优化后的参数如表1所示,结果如图5所示。从结果曲线可知,40—60 GHz频段内输入端口Port1的反射系数S11在-19 dB以下,表明更多信号被传输至微带线上,与未加转换结构相比,添加波导-微带转换结构后回波损耗恶化1 dB,4个输出端口Port2—Port5的幅度、相位趋势较为一致,其中幅度差异在0.1 dB以内,对合成效率的影响较小。

1.3 合成网络

芯片尺寸为3.80 mm×2.38 mm×0.05 mm,根据芯片尺寸设计谐振腔大小,保证放置芯片和载板后仍有一定余量。谐振腔分为上下腔,下腔的深度为介质基板厚度,便于更好地固定介质基板,上腔可用于芯片散热。功率分配和合成器背靠背连接谐振腔两端,如图6所示。输入端输入一路信号,经过两级E-T结构成的四路功分器均分为四路信号,波导-微带探针转换结构将四路波导输出的信号转换到微带线传输,经谐振腔内的功率放大器(MMIC)放大,最后通过两级E-T结构成的四路合成器合为一路信号输出。

为保证测试结果的准确性,在谐振腔上腔表面添加辐射边界模拟实际开放环境,对整个合成网络进行仿真优化。S21损耗越小越好,但受宽带影响S21不会降到很低,本文最大优化到1 dB以下。指标合格后加工制造实物,用矢量网络分析仪进行无源结构测试,测试和仿真曲线如图7所示。

在工作频段内,背靠背结构仿真的回波损耗大于13 dB,插入损耗小于1 dB,单边损耗小于0.5 dB。实际测试回波损耗在全频段内大于9.2 dB,插入损耗在大部分频段处于0.5~1 dB,单边损耗为0.25~0.5 dB,插入损耗最大为1.9 dB,位于56.4 GHz。根据插入损耗计算合成网络的合成效率在79.4%~89.1%,单边合成效率在89.1%~94.4%。对比仿真结果,实测损耗偏高,部分频率点出现谐振,其原因可能是加工尺寸误差、组装误差和测试时端口连接处能量泄漏导致损耗偏高,高频导致谐振增多,但在可接受范围内。

2 功率合成放大器

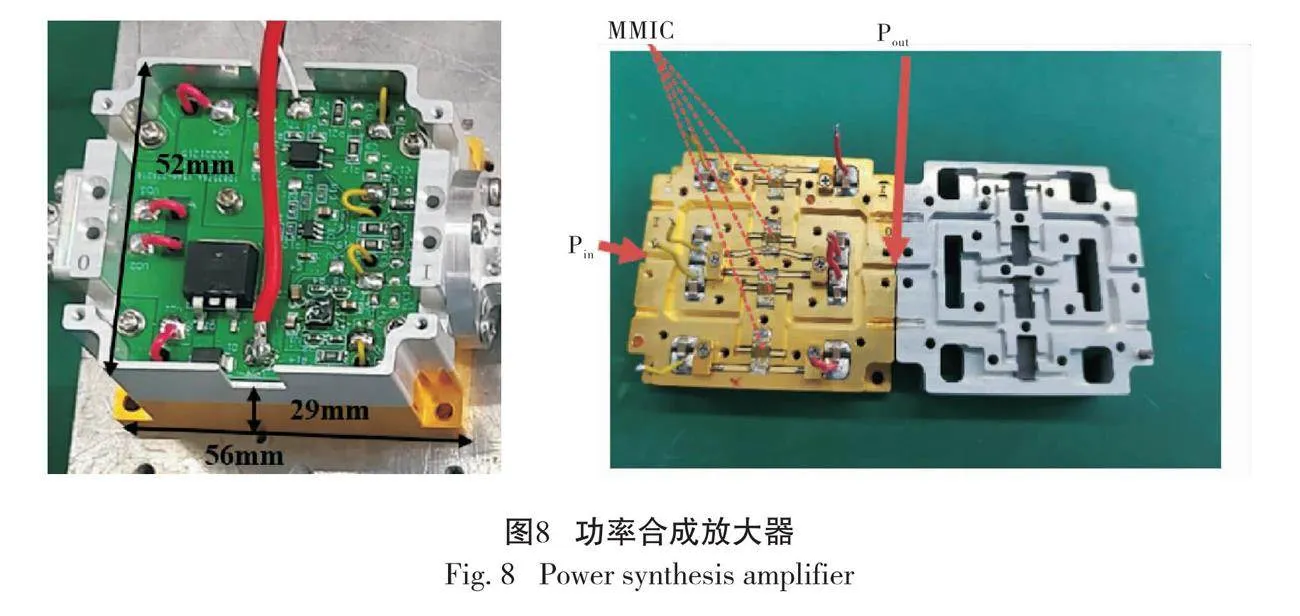

2.1 功率合成放大器的制作

合成网络的无源测试合格后,夹断谐振腔内的微带线,据芯片手册对芯片进行装配。该放大器采用某国产GaN芯片,其工作频段为40—60 GHz,饱和输出功率典型值为36 dBm,小信号增益典型值为20 dB,漏压为+15 V,栅压为-5 V。芯片电容间、芯片电容与芯片焊盘之间和射频输入输出端均通过金丝连接,金丝直径为25 μm。为了简化电路,用两根金丝将一块芯片两端的漏极和栅极分别引出来;为了减少信号反射,适当降低金丝拱高,缩短金丝的长度和键合线。

装配芯片后的U频段功率合成放大器如图8所示, 下腔材料为表面镀金的铜,利于高功率芯片散热,上腔材料为表面镀镍的铝合金,减轻模块重量。GaN功率芯片的热流密度较高,腔体内的热量不能及时传导出去,将严重影响芯片的使用性能甚至损坏芯片。为保证腔体内的良好散热,芯片位于下腔,先与载板在180 ℃下共晶焊接,将热量通过载板传导至金属腔体,再用导电胶将装有载板的芯片粘贴在腔体上。载板尺寸为3.82 mm×6.5 mm×0.5 mm,材料选用钨铜合金,匹配GaN芯片热膨胀系数。吸波材料粘贴在上腔,降低腔体内反射的电磁波能量,避免串扰自激。稳压源电路置于上腔体背面,导线穿孔连接芯片供电,保证放大器正常工作。

2.2 功率合成放大器的测试

完成功率放大器装配后,检查漏极栅极阻抗,栅极阻抗为兆欧或千欧级别,漏极阻抗通常只有零点几欧。由于芯片装配误差使得静态点与芯片手册数据偏离,芯片性能受到影响,使用滑动变阻器对栅压进行反复调试直至逼近芯片手册数据,焊接相应电阻值的电阻,最终静态工作点为栅压-1.5 V,漏极电流 0.82 A。

测试框图如图9所示,信号发生器提供最大输出功率有限,不能将功放模块推至饱和状态,故需要驱动放大器进行驱动。根据手册可知芯片承受最大的输入功率为32 dBm (1.58 W),考虑到功分器6.5 dB损耗,故待测模块输入功率上限为38.5 dBm (7.08 W)。功率探头可测试最大功率为20 dBm (0.1 W),本文功率合成放大器的输出功率大于20 dBm (0.1 W),直接测试会烧毁功率探头。待测模块后面连接耦合器,输出功率小部分进入功率计进行测试,大部分进入负载被吸收。

按照测试框图连接各设备,待测模块下方涂上一层导热脂,再用螺钉固定在散热器上,采用直流稳压源对散热器、驱动、待测模块供电。加电后调节输入功率使其进入饱和状态,即增加输入功率,待测模块的输出功率不再增加,最后测试不同频率下的输出功率。测试结果如图10所示,在40—54 GHz频段内输出功率大于40 dBm(10 W),54—60 GHz输出功率大于37.8 dBm(6.03 W),与待测模块输入功率对比,其功率增益在7 dB左右。

观察图10(a),输入输出功率随频率升高呈下降趋势,在高频段下降趋势更明显。观察图10(b),功率增益为输入输出功率之差,曲线在一定范围出现波动,在高频段不足7 dB。曲线出现小范围波动属于正常现象,对部分频点凸起或者凹陷进行原因分析如下:

第一为功放芯片性能不佳。芯片手册的增益曲线随着温度升高和频率增加,增益出现下降趋势,下降幅度约达到6 dB,导致单片芯片的饱和输出功率在53—58 GHz不断下降。该芯片为超宽带芯片,超宽带限制了输出功率和增益,且芯片实际工作情况和数据手册存在差异,可能出现性能恶化。四路芯片的差异使得工作情况不能完全一致,输出相位幅度出现偏差,可能导致部分频点输出功率偏高或偏低。因此,芯片工作性能可能是导致输出不稳定的主要原因。

第二为装配误差导致。芯片及芯片电容与微带连接易产生缝隙,即不可能完全匹配,且用于连接的金丝数量、长度、拱高、焊点位置等影响电路传输,在高频段键合金丝的寄生电感效应较为明显,容易引起电路失配。Rogers 5880介质基板为软质基板,容易起翘变形,可能在装配中出现玻珠偏离波导中心,造成探针耦合能量减少,可以考虑选用表面光洁度更高的陶瓷基片,在高频的损耗相对较小。

第三为机械加工误差导致。频率越高电路尺寸越小,精度越难以保证,腔体结构的加工误差导致凹槽、倒角处不平坦,增大部分频点的损耗,且基板上的微带线采用丝网印刷技术,加工可靠性较低。

第四为测试误差导致。驱动模块、待测模块和耦合器连接处波导端面不平稳,部分能量发生泄露,且模块间可能产生自激引起阻抗失配,可以考虑在两模块间加一个隔离器。芯片容易受环境温度影响,测试处于常温状态,且设置散热器散热。已严格检查操作流程,结果变化不大,故测试误差影响较小。

3 结 论

本文采用一种简单的波导功分/合成结构实现了40—60 GHz高频超宽带功率合成放大器。在工作带宽内,合成网络的损耗低于1.3 dB,添加功率放大芯片后,40—54 GHz频带内输出功率大于40 dBm(10 W),合成效率超过了80%;在54—60 GHz频段,由于芯片输出功率下降及加工、装配精度的影响,合成效率受到的影响较大,后续考虑将基片改成陶瓷等板材,提高精度,争取将全频段合成效率提高到80%以上。

参考文献:

[1] 张京安.V波段全频段径向功率合成网络的研究[D].南京:南京理工大学,2019.

[2] 唐洪.Q波段固态功放研究[D].成都:电子科技大学,2017.

[3] GIOFR R,LIMITI E,MASSARIA,et al.20W linearized Q-band solid state power amplifier for satellite communication application[C]//2020 50th European Microwave Conference (EuMC),Utrecht:IEEE,2021:776-779.

[4] YIN K,XU J P.A broadband power-combined amplifier based on multi-stage probe-pair traveling-wave power divider/combiner at Ka-band[J].Journal of Electromagnetic Waves and Applications,2014,28(9):1056-1067.

[5] 王斌,刘立浩,谢小强,等.一种新型Ka频段功率合成放大器的设计[J].电波科学学报,2017,32(1):39-43.

[6] WANG T,NING Y,ZHU W.Design of an E-band power amplifier based on waveguide power-combining technique[C]//2018 International Conference on Microwave and Millimeter Wave Technology (ICMMT).Chengdu:IEEE,2018:1-3.

[7] 马升旺.22—32GHz全带宽一分七路波导功分器研究[D].西安:西安电子科技大学,2021.

[8] XIE X,YANG G,ZHANG Y,et al.Full band millimeter-wave power-combining amplifier using a lossy power-combining network[J].Journal of Infrared,Millimeter,and Terahertz Waves,2016,37:318-327.

[9] LI J,HUANG Y,LI Y,et al.Wideband transition between rectangular waveguide and microstrip using asymmetric fin line probe[J].Electronics Letters,2017,53(7):490-492.

[10]LI J,LI L,QIAO Y,et al.Full Ka band waveguide-to-microstrip inline transition design[J].Journal of Infrared,Millimeter,and Terahertz Waves,2018,39:714-722.

[11]REBOLLO A,GONZALO R,EDERRAI.An inline microstrip-to-waveguide transition operating in the full W-band[J].Journal of Infrared,Millimeter,and Terahertz Waves,2015,36:734-744.

Design of A U-band Power Amplifier

LI Ying-ying,ZHOU Yong-hong

(School of Electronic Information Engineering,China West Normal University,Nanchong Sichuan 637009,China)

Abstract:In this paper,a U-band (40—60 GHz) power amplifier based on waveguide spatial power synthesis technology is designed.The four-channel power synthesis network with broadband and low loss is realized by employing E-plane T-junction power distribution/synthesis structure and waveguide-microstrip conversion.After modeling,simulation and optimization,the physical product is processed and manufactured.The measured back-to-back insertion loss in the full frequency band is less than 1.3 dB,which is in good agreement with the simulation results.After assembling four domestic amplification chips,it is measured that the saturated output power is more than 37.8 dBm(6.03 W)in 40—60 GHz,and the output power is better than 40 dBm(10 W) in 40—54 GHz.Compared with the input power,the power gain is about 7 dB,and the synthesis efficiency is more than 80%.

Keywords:solid-state power amplifier;U-band;broadband;low loss;E-plane T-junction