支持高速DMA 传输技术的SSD 控制器设计与实现

沈庆,杨楚玮,侯庆庆

(中国电子科技集团公司第五十八研究所,江苏无锡 214035)

1 引言

在信息电子通信系统所涉及的大多数场景下,数据存储及传输都不可或缺。在存储硬盘领域,固态硬盘(SSD)作为目前的主流存储设备满足了多种场景下的使用需求,同时还具有便携、功耗低及易扩展等特点[1-3]。串行ATA(SATA)协议凭借接口适应性强、速度快、抗干扰等特点得以广泛应用。在存储架构方面,文献[4-5]提出采用磁盘阵列的方式进行存储,并且定制了高速存储系统的接口模块,提高了存储速度,但采用的SATA2 协议传输速率有限且存储方式不具备纠错能力;文献[6]提出采用SATA 芯片实现数据的高带宽数据传输,但未采用通用处理器架构,因此不易于扩展与移植;文献[7]提出采用多控制器来操作多片NAND Flash 的架构,其问题在于控制器之间同步性较差。在直接存储器访问(DMA)传输设计方面,文献[8]提出采用基于SATA 的直接存储系统设计,DMA 的设计主要集中在SATA 端,设备端缺少对DMA 传输的处理,采用ARM+FPGA 的结构和AXI 总线处理DMA 传输请求,功耗较高且传输性能不理想。本文利用多通道并行策略和Flash 阵列管理技术设计了一种SSD 控制器,在SATA 接口及控制器中采用高速DMA 传输策略,提高了数据传输速度。

2 SSD 控制器体系结构

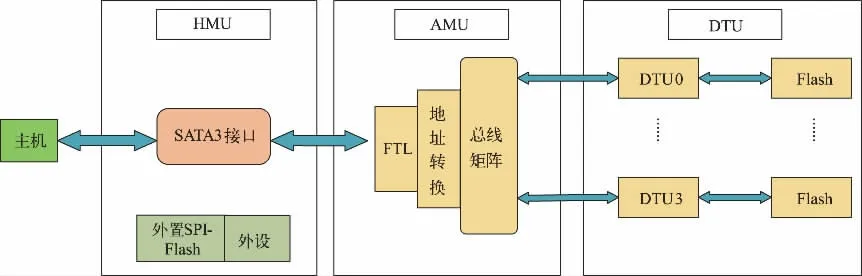

控制器采用的双CPU 核结构均为Cortex-M3 内核(32 位)架构。主机处理单元(HMU)模块负责SSD与系统主机之间的通信及板级外设控制功能;算法管理单元(AMU)模块负责闪存转换层(FTL)算法管理,主要包含FTL 算法的实现,并且对Flash 存储阵列进行管理与地址转换;数据传输单元(DTU)模块负责与Flash 进行数据传输。HMU 与AMU 固件代码的硬件载体为NAND Flash,SPI Flash 作为代码备份区域。SSD 控制器整体架构如图1 所示。

图1 SSD 控制器整体架构

3 Flash 阵列管理技术

Flash 阵列管理的目的是通过优化Flash 数据阵列结构来提高数据并行性,从而提高SSD 的读写性能[9-10]。Flash 多通道并行阵列存储结构如图2 所示,Flash 阵列采用并行总线方式,闪存阵列共用控制信号Control与片选信号CS。由CS 来拉低同一行所有Flash;剩余信号线分别控制各个所属Flash,包括读写使能信号、命令/地址锁存信号等,在图中统一用Control 线表示。每次CS 有效,将选中所有Flash 进行操作,每次传输的数据都能被均分到Flash 阵列的每一个Flash 中,实现大数据量的读写操作。

图2 Flash 多通道并行阵列存储结构

如图1 所示,DTU 被划分为4 个通道,分别与Flash 阵列进行数据交互。每个通道最多可容纳8 片Flash,因此容量最多可扩展到32 片Flash,由于通道间相互独立且只有一个CPU 控制,大量的数据传输或读写操作会严重消耗CPU 资源,影响通道间的读写性能。本文添加了DMA 的设计,DMA 配合控制器完成数据的读写,CPU 仅负责数据的地址与命令的读写,这大大减少了CPU 的资源占用,所以从整体上看,通道间是并行操作的。同时,所提供的Flash 阵列管理可以灵活调整存储颗粒数量以及更改存储颗粒类型,具有一定的易扩展性和易升级性。

4 高速DMA 传输设计

本文设计的高速DMA 模块存在于SATA 接口、HMU、AMU、DTU 等模块,用于对主机和设备端的数据请求与数据传输工作。DMA 的应用不仅大幅提高了数据传输的速度,而且减少了对CPU 资源的占用,提升了交互命令的处理速度。

4.1 SATA 接口DMA 模块

SATA 接口结构原理如图3 所示。Port DMA 的作用包括:处理软件分发的命令,传输相应的帧信息结构(FIS)到传输层;接收从传输层接收到的FIS,并将FIS 发送给CPU;在传输层FIFO 和系统内存之间传输数据;支持收发时钟的电源管理。SATA 接口协议中,跟DMA 传输紧密相关的层级包括命令层、传输层、链路层。

图3 SATA 接口结构原理

4.2 控制器DMA 模块

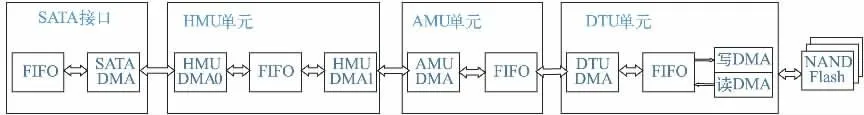

SATA SSD 控制器中DMA 设计包括SATA DMA、HMU DMA0/1、AMU DMA、DTU DMA、DTU读/写DMA 共7 个DMA 加速引擎,如图4 所示。

图4 SATA SSD 控制器内部DMA 分布

4.2.1 HMU DMA 模块

HMU 单元中包含HMU DMA0/1,其中HMU DMA0 用于和SATA DMA 模块进行交互,HMU DMA1 用于和AMU DMA 进行交互,如图5 所示。

图5 HMU DMA 连接关系

HMU 单元与SATA DMA 的传输指SATA 接口的FIFO 和HMU 单元的FIFO 之间经过SATA DMA和HMU DMA0 的传输。主机读数据操作:数据从HMU 的FIFO 先经过HMU DMA0,然后经过SATA DMA,最终到达SATA Rx FIFO。主机写数据操作:数据从SATA Tx FIFO 先经过SATA DMA,然后经过HMU DMA0,最终到达HMU 的FIFO。其中HMU 包括两种类型的FIFO:一种是单端口FIFO,由4 个单端口FIFO 组成,在同一时刻只能进行读操作或写操作;另一种是双端口FIFO,在同一时刻可以同时读写。

4.2.2 AMU DMA 模块

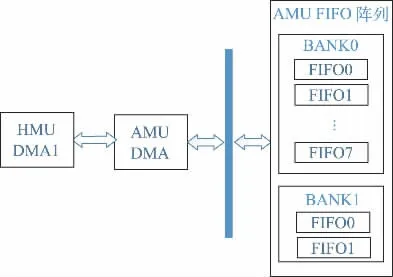

AMU 单元与HMU 单元的DMA 传输指AMU DMA 将HMU DMA1 的数据送至AMU FIFO 阵列管理模块,AMU 与HMU 的连接关系如图6 所示。

图6 AMU 与HMU 的连接关系

AMU 单元与DTU 单元的DMA 传输指AMU 接收到HMU 或者SATA 传输数据指令时,通过控制总线发送传输指令到DTU,DTU 根据指令配置DTU DMA,AMU FIFO 和DTU FIFO 进行数据交互。AMU单元本身无DMA 和DTU 交互。

4.2.3 DTU DMA 模块

当AMU 与DTU 进行数据交互时,通过控制总线发送传输指令到DTU,DTU 根据具体指令被动配置DTU DMA,AMU FIFO 和DTU FIFO 进行数据交互。DTU 与AMU 的数据传输采用Local FIFO,Local FIFO 由4 个FIFO segment 组成,每个segment 可以实现以下操作:①和AMU FIFO 传输数据;②和Flash 的DMA 模块传输数据;③和其他3 个FIFO segment 传输数据;④被CPU 访问。在同一时刻,一个FIFO segment 实现上面其中一种操作,与此同时,其他FIFO segment 可以实现其他操作。DTU 与AMU 的连接关系如图7 所示。

图7 DTU 与AMU 的连接关系

5 测试与结果分析

采用本文提出的SSD 控制器设计方案,选择长江存储某NAND Flash 颗粒,为方便控制器的嵌入式应用与性能测试,控制器与若干颗粒组成的存储阵列进行通信,完成一系列读写测试。

5.1 DMA 读写功能测试

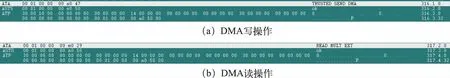

DMA 读写功能测试结果如图8 所示,采用Bus Hound 向SSD 发出DMA 读写命令,将数据写入存储阵列,随后将数据读出并进行校验,多次测试均未发现数据校验错误,表明阵列控制器可以稳定地完成读写操作。

图8 DMA 读写功能测试结果

5.2 不同通道间的读写测试

四通道读写测试:DTU 通道数量设置为4,使用ATTO Disk Benchmark 软件,传输的文件大小为16~8 192 kB,总长度为512 MB,直接I/O 访问读写测试结果如图9(a)所示。两通道读写测试:DTU 通道数量设 置为2,使用相同的软件设置,其测试结果如图9(b)所示。

图9 不同通道读写速率测试结果

由图9 可以看出,当传输文件从4 kB 一直到8 192 kB 变化时,对于不同大小的文件,读写性能均很稳定。两通道读取速率达119 MB/s,写入速率达78MB/s;四通道读取速率达238 MB/s,写入速率达152 MB/s。四通道的读写性能约为两通道的两倍,符合设计预期,同时也说明DMA 在传输数据时,适应了不同通道间的速率差异,符合硬盘在不同通道间的读写性能表现。

5.3 单字节访问下的读写测试

为验证本文设计的DMA 数据传输性能优化效果,在同一硬件环境下,将SSD 控制器中DMA 模块失能,切换为字节访问模式,其测试结果如图10 所示。

图10 单字节访问读写速率测试结果

由图10 可以看出,单字节访问模式下,两通道读取和写入速率可达20 MB/s 和14 MB/s;四通道读取和写入速率可达50 MB/s 和28 MB/s。经实验测试,DMA 模式与单字节访问相比,读写速率均有较大的提升。本文提出的高速DMA 传输设计技术有效地提高了SSD 数据传输效率,大幅提高了SSD 的读写速率。

5.4 高低温实验测试

为了测试控制器的环境适应能力,对其进行高低温实验测试,验证其在-55~125 ℃环境中的工作性能。将测试电路(四通道模式下)放入温箱,SSD 读写性能如图11 所示。

图11 -55~125 ℃下SSD 读写性能

使用burn in test 工具在高低温环境下对其进行长时间(72 h)读写对比测试,多次测试结果均未出现误码,由此可知,本控制器可以适应较复杂的工业温度环境,且读写速率较稳定。

6 结论

本文阐述了一种支持高速DMA 传输技术的SSD控制器设计与实现方法,多次功能及性能测试结果表明,所设计的SSD 控制器可以满足不同环境温度下大容量、高速率的数据传输及存储需求,同时,所提供的Flash 阵列管理使存储颗粒具有一定的扩展性和升级性。

本设计在SATA 控制器中存在多个DMA 控制模块,增加了固件配置和调度DMA 模块的成本,未来计划结合硬件模块设计和固件设计等多方需求,整合DMA 资源,降低固件对DMA 的配置和调度成本,从而更加高效地使用高速DMA 技术,实现SDD 读写速度和使用寿命的进一步提高。