基于FPGA 的图像处理实验平台设计*

林科业,黄仕凰

(韩山师范学院物理与电子工程学院,广东 潮州 521041)

1 引 言

数字图像处理技术已经广泛应用到日常生活和工业生产中。传统的数字图像处理技术主要是基于PC 软件平台的处理方式[1-2]。但PC 软件平台由于体积较大、较为笨重等缺陷,带来了应用上的不便利,移植到到嵌入式开发平台上是一个不错的解决办法。随着图像采集设备的更新换代,以及视频处理技术的发展,采集到的图像的分辨率、存储大小以及图像的处理速度都越来越高[3],这也要求嵌入式平台图像处理系统有更可能小的硬件体积和尽可能高的实时性。在众多的嵌入式平台中,FPGA 平台因其处理速度快、处理能力强等特点[4]能够很好地满足要求。本研究即采用FPGA 平台,以模块化的方式设计图像处理实验,让程序设计更简便,移植性更好,有助于更快地进行二次开发。

2 FPGA 实验平台系统架构

在实验设计中,FPGA 实验平台的外设主要有OV5640 摄像头、SDRAM 存储器、按键以及VGA 显示器。OV5640 摄像头主要用来采集图像,其感光阵列为:2592×1944pixel(即500 万像素)[5]。在实验设计中,采集的图像像素大小为640×480pixel,帧率能够达到90f/s。这样的采样帧率能够满足工业化生产领域图像快速采集的需求。设计中使用的按键,是用来实现图像处理功能的切换控制。按键经过消除抖动后,计算按键的有效按下次数,来切换VGA 显示器显示的内容。在设计中,考虑到采集设备和显示设备的频率不同,需要将经过图像处理后的图像存储到SDRAM 芯片中,再从SDRAM 读取到VGA 进行显示。

在FPGA 程序设计中,以模块化的方式,将程序设计成不同功能的模块,其系统架构如图1 所示。在每个不同功能的模块中都有一个主文件,用于将模块中的各个程序整合起来;引出较少的端口将更加便于不同模块之间的信号通信。最后工程的顶层文件再将各个模块的主文件进行整合调用。模块化设计思路使整个程序架构层次分明,不同模块之间的调用更加简单。

图1 FPGA 实验平台的系统架构图

由于各外设的时钟频率不同,在程序设计中,须用PLL 锁相环提供时钟频率并确保精度。实验采用的FPGA 开发平台的工作时钟频率是50 MHz。SDRAM 需要用到100 MHz 和相位偏移了180°的100MHz 频率,皆可通过PLL 锁相环进行倍频获得。OV5640 和VGA 显示640×480 分辨率的时候,所需工作频率是25MHz,需要PLL 锁相环进行分频。

图1 中的OV5640 模块封装了OV5640 摄像头工作的驱动程序,以及图像获取程序。调用OV5640的主程序就能获得摄像头采集到的图像。OV5640摄像头的驱动程序的各个寄存器配置和驱动通过I2C 总线来实现。OV5640 摄像头获取到的图像以16位的数据输出。

采集到的图像通过图1 中的图像模块进行数字图处理。在设计中,不同的数字图像的处理程序,都在这部分模块中实现。按键按下的次数控制数字图像处理后的结果输出。各个图像处理算法又可以封装成独立的单元模块,使用时只需要在主文件调用各个独立模块即可。

图1 中的SDRAM 模块主要负责SDRAM 芯片的驱动。程序设计中需要对SDRAM 芯片进行初始化、周期性的刷新,以及读写控制。将经过图像处理后的数据存储到SDRAM 芯片中。需要显示时,再从SDRAM 中读取数据到VGA 显示器进行显示。

图1 中的VGA 模块实现对VGA 显示驱动。该模块需要根据显示的分辨率进行显示参数的设置。在设计中,VGA 显示器采用640×480 的分辨率,工作频率为25MHz。

3 图像处理模块设计

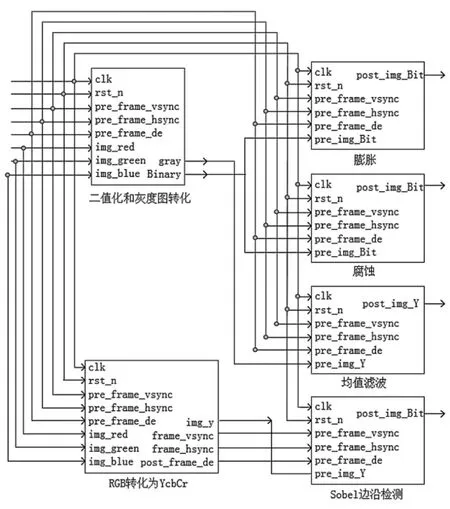

实验设计了6 个图像处理模块,分别用来实现图像的灰度处理、二值化、RGB 到YCbCr 色彩空间的转化、均值滤波、形态学中的腐蚀和膨胀,以及Sobel 边沿检测,总体结构如图2 所示。每个模块除了图像数据的输入端口有所差异,其他信号的输入端口都是一致的。每个模块都是独立的处理单元,这便于调试,也让电路设计更为直观。每个模块在设计的过程中,需要注意输入信号和输出信号的同步,以免造成信号的不同步,导致VGA 显示上的错乱。

图2 图像处理模块示意图

摄像头OV5640 采集到的图像是16 位的彩色图像,红色、绿色和蓝色各占5 位、6 位和5 位[6];根据公式Gray=0.299R+0.587G+0.114B,可将彩色图像转换为灰度图像。在FPGA 实现中,先把RGB 三个分量扩充为8 位的数据,再用一个24 位的中间变量Gray_m 来存储灰度转换后的结果[7-8]。由于FPGA对浮点运算需要消耗很多资源,在设计中要对系数进行倍数放大,将除法运算转换成乘法运算:

RGB 到YCbCr 色彩空间的转化,则可以根据以下公式:

摄像头采集的图像经过灰度转换后,在灰度值的基础上设置一个阈值,将灰度图像转换成二值图像。转换后的二值图像就可以进行图像形态学操作。图像膨胀或图像腐蚀实验都是在二值图像的基础上进行的图像处理。

在实验过程中,图像的膨胀、腐蚀、均值滤波,以及Sobel 运算,都需要使用RAM 对图像数据进行缓存,再将图像与卷积核进行卷积。所以实验设计采用双端口RAM。RAM 的存储深度根据显示分辨率进行设置。由于VGA 的显示频率是640×480,在设置RAM 的存储深度时设置为640,位宽为8bit。在程序例化时,RAM 寄存器需要例化两个单位,用于存储图像的上一行和前一行数据。RAM 存储和卷积运算原理如图3 所示。通过移位的方式,每次将每行的前三个数据取出,再和卷积核进行卷积运算。根据卷积核不同,可进行不同的图像处理。

图3 RAM 存储和卷积运算示意图

4 实验结果

实验设计为使用一个按键实现图像处理功能的切换。按键通过消抖动后,根据按键被按下的有效次数,能够很好的控制图像的不同处理功能的切换。具体切换效果如图4 所示。

图4 图像处理实验效果

当按键按一下时,对图像进行均值滤波处理,如图4(a)所示为图像经过3×3 卷积核均值滤波处理后的结果。实验的均值滤波是在灰度图像上进行的,均值滤波后图像相较原图像边沿会更平滑些。

当按键按两下时,对图像进行Sobel 算法运算,图4(b)即为Sobel 运算后的效果。原灰度图像经过Sobel 运算能够很好地提取图像的边沿轮廓。

当按键按三下时,对图像进行RGB 到灰度转化,如图4(c)所示。灰度转化后,原图像由原来的16位RGB 彩色图像变成了8 位的灰度图像。

当按键按四下时,对图像进行二值化处理,效果如图4(d)所示。图像的二值化处理是将原灰度图像的每个像素点和预定设置的阀值进行比较,得到每个像素点为0 和1 的二值图像。

当按键按五下时,对图像进行图像形态学膨胀处理,如图4(e)。实验中的膨胀处理需要先对原灰度图像进行二值化处理;再对每个像素点周围的8 个像素点进行或运算。

当按键按六下时,对图像进行图像形态学腐蚀处理,如图4(f)。实验中的腐蚀处理也需要先对原灰度图像进行二值化处理;再对每个像素点周围的8个像素点进行与运算。

实验结果表明,FPGA 平台上能够很好的实现数字图像处理的基本功能。所设计的图像预处理模块,体现出了较高的灵活性和较快的处理速度。

5 结束语

本研究基于FPGA 平台,以模块化思路加以设计。图像处理实验图像预处理模块具有较强的可移植性,能够为具体的工程项目开发提供帮助,具有非常好的应用和研究价值。在对数字图像处理算法的后续研究中,可以在现有的工程架构上进行进一步完善,添加相应的模块,实现更高阶的用法和功能。