基于FPGA 的高精度模数转换器测试系统及方法研究*

伍江雄,温显超,魏亚峰,陈 超,张 超,俞 宙,王健安

(1.重庆吉芯科技有限公司,重庆 400060;2.中国电子科技集团公司第二十四研究所,重庆 400060)

1 引 言

模拟转换器的测试作为当前集成电路测试领域一个重要分支,其测试需求随着集成电路迅猛发展达到了新的高度。SAR 结构模数转换器分辨率可达24 位;Σ-Δ 结构模数转换器分辨率可达32 位[1]。使用传统方法实现如此超高精度模数转换器的测试不仅需要连接高精度信号源仪器以及精密测试仪器,测试需要采样的数据量也非常之大,使得测试成本昂贵,测试效率低下。降低传统模数转换器测试仪器成本、提高测试效率势在必行[2]。

2 高精度模数转换器测试系统搭建

2.1 框架设计

传统模数转换器分离仪器测试平台包括“高精度信号源仪器+被测模拟转换器”和“被测模拟转换器+精密测试仪器”两种结构,前者的结构方式是采用高精度信号源仪器输出连续的模拟信号,模拟转换器采样后的数据传回PC 机直接运算,可达到模拟转换器最真实的线性度指标和信噪比等指标[3]。

传统的分离式测试平台所使用的高精度仪器信号源或精密测试仪器往往比较昂贵,鉴于此设计一种低成本的高精度模数转换器测试系统,如图1所示为其框架结构图。它由高精度ADC 板卡、FPGA数据采集板卡、高精度数模信号源和数据采集分析软件组成。其中高精度ADC 板卡为被测对象。

FPGA 数据采集系统的整个工作流程为:FPGA数据采集板卡接收到上位机的控制指令,进行模数转换器数据采集;采集到的数据暂存在DDR3 中的相应的数据量之后;FPGA 的控制时序从DDR3 中读取数据并通过USB2.0 接口传输到上位机;数据采集分析软件对数据进行计算分析,并将计算的结果通过图表的形式显示在软件上。

2.2 FPGA 数据采集板卡设计

如图2 所示为FPGA 数据采集板卡构架,包含FPGA 逻辑处理芯片、USB2.0 数据传输接口、DDR3数据存储颗粒、MCU 命令控制芯片和IO 接口。

图2 FPGA 数据采集板卡构架

数据采集板所能支持的接口速率包括SDR 接口最高速度400Mb/s 和DDR 接口最高速度800Mb/s;USB2.0 接口的数据传输速度最高可达480 Mb/s;DDR3 的数据存储容量为2Gb;MCU 通过串口与上位机通信,进行简单的继电器和低速IO 控制;IO 接口用于连接高精度数模信号源板卡和被测模数转换器板卡。FPGA 与DDR3 之间的布线完全遵照Xilinx 的DDR3 设计规范,严格保证数据线、地址线等长和阻抗控制[4]。FPGA 与USB 芯片和MCU 之间的走线控制50 Ω 阻抗,USB 芯片到USB 接口之间的数据走线控制90Ω 差分阻抗。PCB 上端的对外接口与FPGA 之间使用等长差分对进行布线,差分阻抗控制在100Ω,可支持CMOS 电平、LVDS 电平的器件数据采集。数据采集板卡的各个部分由低抖动的线性LDO 供电,可保证板卡正常工作。

相比于逻辑分析仪,FPGA 数据采集板卡具备体积小、可编程性好、成本低的特点,可对各类高精度低速模数转换器进行编程控制,具备一定的通用性。

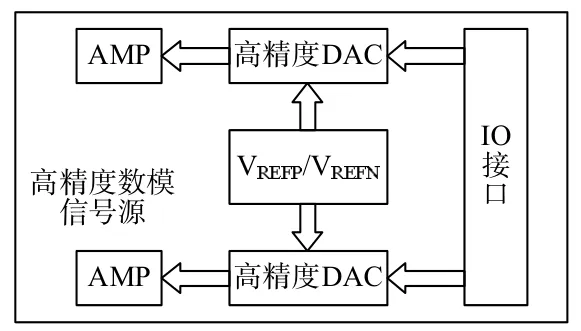

2.3 高精度数模信号源设计

如图3 所示为高精度数模信号源构架,它包含2 个20 位的高精度DAC(数字模拟转换器)、输出端运算放大器、高精度基准源和SPI 控制接口。其中20 位的高精度DAC 的噪声谱密度为输出电压噪声典型值为1.1μVP-P,性能满足线性度误差的测试要求。运算放大器的工作带宽为10MHz,低噪声高精度基准源的输出噪声可达1.0 μVP-P,两者配合高精度DAC 使用,可发挥最优性能。IO 接口用于连接FPGA 数据采集板卡,接受控制指令以产生正弦波、方波或斜坡波[5]。

图3 高精度数模信号源构架

高精度DAC 的理想传递函数为:

其中,VREFN是DAC 输入引脚上的负基准电压;VREFP是DAC 输入引脚上的正基准电压;D 为DAC 的20位代码。对于不同的高精度ADC(模拟数字转换器),可根据ADC 模拟输入要求的不同进行编程,产生相应的波形。波形可覆盖到真差分、伪差分、单端双极性和单端单极性输出方式。

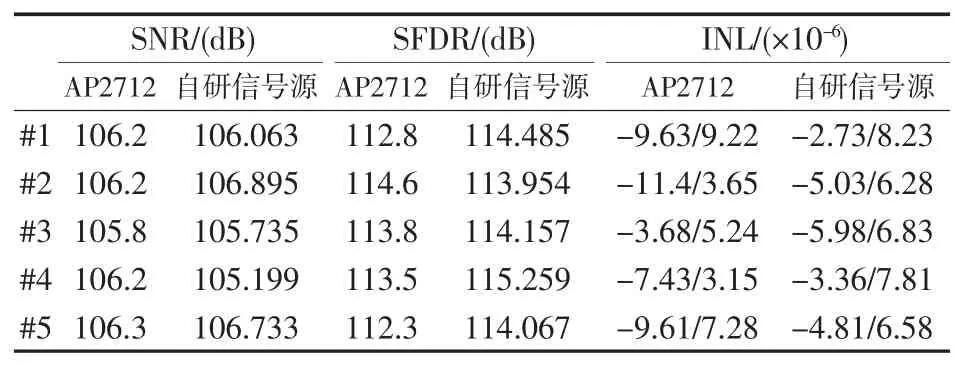

如表1 所示为AP2712 和自研的高精度信号源板卡的对比测试结果。两个信号源分别对某24 位ADC 进行批量性测试,来判断自研信号源的测试能力。表1 中只列出了5 只电路的测试结果。可见自研的高精度数模信号源与音频信号源AP2712 测试性能相当,而自研高精度信号源具备体积小、成本低、可灵活编程的特点,特别是在进行线性度测试时,需要配合ADC 的时序进行编程,而高精度模拟信号源仪器不具备这一特点。

表1 信号源对比测试结果

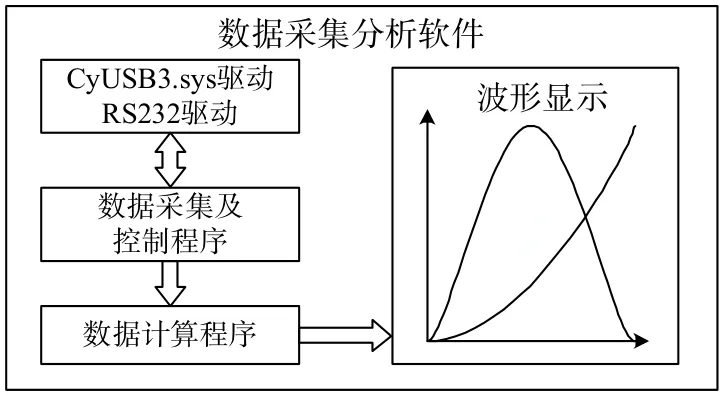

2.4 数据采集分析软件设计

如图4 所示为数据采集分析软件架构,包含数据采集和命令控制、数据计算、波形显示三个部分。数据采集分析软件以CyUSB3.sys 驱动[6]和RS232 驱动为桥梁,与FPGA 数据采集板卡之间进行数据传输和命令控制。软件基于VB.NET 平台进行开发,对熟悉VB6.0 平台的开发人员十分友好。

图4 数据采集分析软件架构

数据采集分析软件的命令控制指令通过RS232串口发送给数据采集板卡,相关的函数声明为:

以上函数的功能为打开串口、处理接收到的数据、处理要发送的数据、选择ADC 通道、读写SPI 寄存器、产生正弦波和斜坡波。

数据采集分析软件的数据采集过程通过USB2.0实现[7],相关的函数声明为:

以上函数的功能为刷新USB 设备、发送采集命令到USB 设备、采集数据。

数据采集分析软件的计算分析函数声明为:

以上函数的功能为计算动态性能和计算线性度性能。

数据采集分析软件的波形显示采用Chart 控件,可快捷地将计算结果显示在界面上。相关的函数声明为:

上述两个函数分别用来初始化Chart 控件和绘制计算结果。

3 线性度测试方法研究

不论是高速低分辨率ADC 还是低速高分辨率ADC,在性能测试过程中都需要评估线性度性能,特别是测试高分辨率ADC 时,线性度指标尤为重要。

线性度指标包含微分非线性DNL(Differential Nonlinearities)和积分非线性INL(Integral Nonlinearities)[8]。在使用传统的正弦波柱状图方法测试线性度指标时,需要采集ADC 的全码。在测试高速ADC时,采集数据的时间可以忽略,但在进行低速高精度ADC 测试时,采集数据的时间会大大增加整个测试过程的时间。例如,某8 通道24 位高精度ADC 的采样率为16kS/s,采集32×224个码值,理论上的采集时间为32768 s,极大增加了测试时间,因此传统的全码测试方法并不适用于低速高精度ADC,故此针对低速高精度的线性度测试给出一种测试新方法。

由于采用正弦波柱状图方法采集数据需要采集比全码本身更多的数据量才能保证完全采集到全码,而使用斜坡波结合ADC 的采样率则可以减少采集的数据量。在此给出的线性度误差计算方法正是使用斜坡波来进行线性度的估算。

假设某低速高精度ADC 的位数为n,则需要采集的码值台阶数为n,每个台阶对应的码值采集次数为m,每个码值采集的时间为t,则需要采集的总码值数所需要的时间为:

其中n 和m 的值往往是越大越好,但是考虑到采集时间的影响,需要在实际的测试过程中确定一个适中的值。采集得到的每个台阶码值平均值为:

其中,k 为台阶数,有0≤k≤n 。再对计算得到的码值进行最小二乘拟合,得到拟合曲线为:

线性度的计算公式则为:

其中ResLSB 为归一化的最小码值,其计算公式为:

找到INL(k)中的最大、最小值,即为器件所对应的线性度误差。该计算方法与传统的全码计算方法相比,增大了等效最小码值,在准确反映器件实际性能的情况下,节约了测试时间。

4 测试验证和分析

用FPGA 数据采集板卡驱动高精度数模信号源板卡,使其连续等间隔输出65536 个数据点。数据点越多,测试越精确,多次实验证明大于65536 个数据点后,线性度指标变化甚微,故此选取此数字,以在测试时间与数据量之间取得平衡。选择高精度数模信号源板卡输出65536 个数据点,电压输出范围为-2.49~2.49V,囊括被测模数转换器的99.6%的输入电压区间范围。

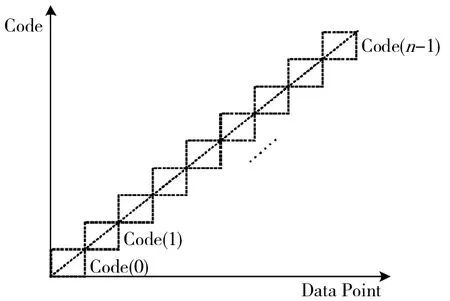

用FPGA 数据采集板卡驱动被测ADC 板卡,采集65536 个数据点,得到65536 个数字码;对这些数字码进行分并处理,如图5 所示,得到N 个Code。经过多次实验,证明一个Code 数据点至少为8,线性度指标稳定,因此本测试选择8192 个Code。对这8192 个Code 的模拟电压均值进行线性拟合,得到拟合曲线F(k)=ak+b,由此计算得到8192 个Code的模拟电压均值拟合值F(0)、F(1)、…、F(n-1);对8192个Code 的模拟电压均值与拟合值相减,得到线性度INL 曲线,即INL(0,1,...,8191)=AvgCode(0,1,...,8191)-F(0,1,...,8191),取得INL(k)中最大值INLmax、最小值INLmin,即为线性度误差。

图5 分并处理示意图

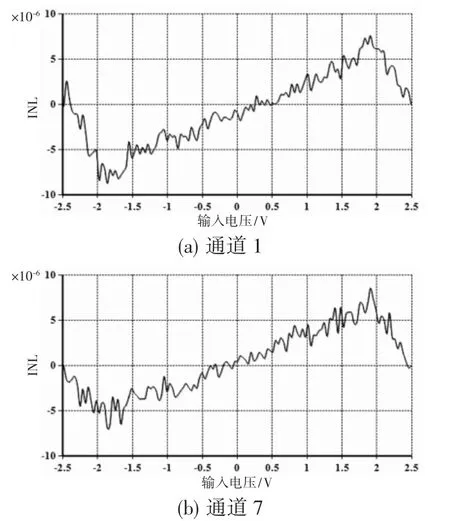

如图6 所示为24 位ADC 的通道1 和通道7 的积分非线性测试结果。从图中可以看出INL 指标在-10×10-6~10×10-6之间。

图6 通道1 和通道7 的积分非线性

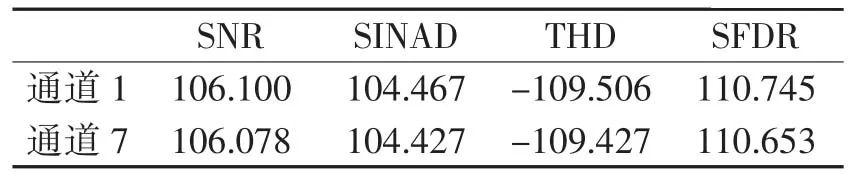

如图7 所示为24 位ADC 的通道1 和通道7 的动态性能[9]测试结果。SNR、SINAD、THD、SFDR 四项参数的结果对比情况如表2 所示。可见各参数指标均处于设计预期范围内。

表2 通道1 和通道7 部分参数对比 单位:(dB)

图7 通道1 和通道7 的动态性能

在测试过程中,ADC 的INL 测试时间小于5 s,而使用“高精度信号源仪器+被测模拟转换器”的结构测试时间约为该线性度测试方法的8192 倍,可见本测试方法节省时间的程度。另外使用本方法测试模数转换器8 个通道的动态性能和线性度的总测试时间大约在60s 左右,测试时间也有大幅缩短。

5 结束语

所提出的基于FPGA 的高精度模数转换器测试系统,结合有效的测试方法,能够准确、高效的实现高精度模数转换器线性度测试指标。本研究对于24位以上的高精度低速SAR 结构、Σ-Δ 结构模数转换器的测试也具有一定的参考价值。