基于E1音频传输的分析与研究

黄亦群 尹 亮

(作者单位:紫金电视调频转播台)

数字音频信号的传输方式多样,各有所长。远距离传输采用光纤,铺设难度大,费用高。基于公共互联网进行传输,偶发的速率波动会造成丢包卡顿,安全性和私密性很差。

基于E1信道的音频传输,采用同步时分复用技术将多个语音信道和控制信道复合在一条速率为2 048 Mbps的高速信道上。并且运行在同步数字体系(Synchronous Digital Hierarchy, SDH)上,中间环节通过电信运营商运营的干线网,自动化、智能化程度高,拥有很强的网络自愈、重组能力,并且做到专线专用,不易受到攻击和干扰。E1专线作为SDH的一种使用形式,提供了一种性价比极高的信道传输方案,在广播电台得到广泛使用。

1 系统方案

1.1 E1传输帧格式

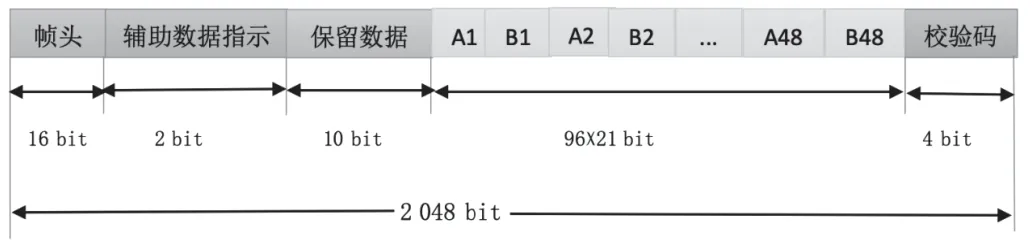

利用E1线路传输非压缩的数字音频信号时,采样频率为48 kHz。在数据位宽为20位数据格式下,每一个帧包含帧头、辅助数据指示、保留数据,48对A、B通道的子帧(见图1)。帧头供给帧同步使用,定义为16 bit二进制数,“111010111001000”,记为X;“0001010001101111”,记为Y。两种帧头交替使用,即相邻两帧分别使用帧头X和帧头Y。A1到B48子帧对,共96个子帧,每个子帧21 bit,其中20 bit为音频取样值,最后一位为保留位。总帧长度为2 048 bit,帧周期为1ms,每秒钟传输的数据量为2.048 Mbps。

图1 传输帧格式图

1.2 系统总体方案

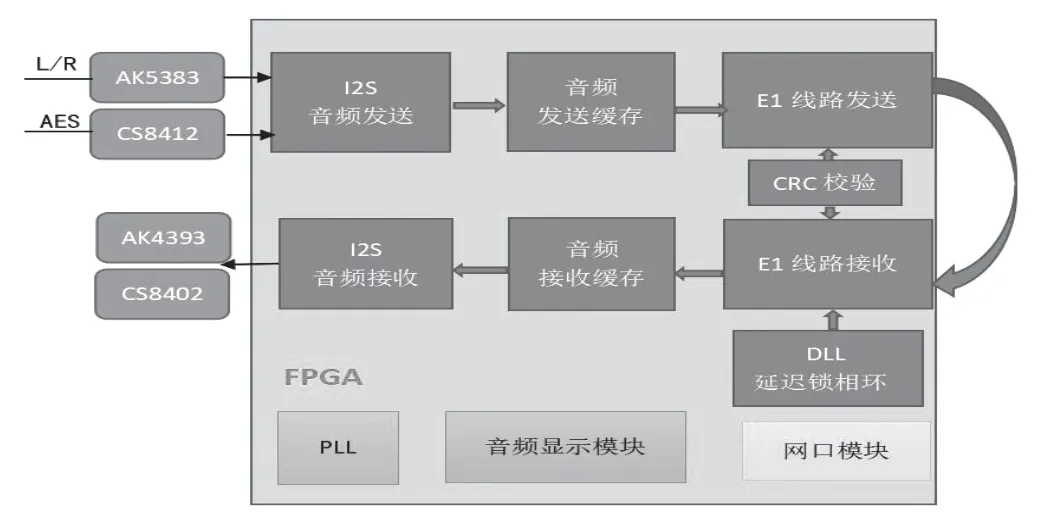

E1音频编码器是将输入的立体声音频信号或AES/EBU数字音频信号,经A/D数字编码变换或数据格式转换后,重新成帧,形成串行数据流,由E1接口输出。音频解码器是将接收E1线路传输的串行数据,经时钟恢复、经拆帧后,恢复出音频信号,输出立体声音频和AES数字音频[1]。音频显示部分用作设备外部显示使用,便于实时监看节目播出状态。网口模块用于和外部服务器交换控制数据。

2 系统模块

2.1 数字音频I2S发送和接收

如图2所示,外部输入的模拟左右立体声信号(L/R)经过AK5383音频编码器,转换为I2S格式的串行数字格式。AK5383是一个24位、128倍过采样的双通道A/D转换器,采用增强型双比特架构,能够达到110 dB的宽动态范围。CS8412用于将输入的AES/EBU数字音频信号转换为I2S格式的串行数字格式。

图2 系统框图

通过判断AES数字音频信号是否存在,程序自动切换分别来自模拟和数字通道的I2S信号。当数字和模拟通道都存在信号时,数字通道优先通过E1线路发送。

从E1线路最终恢复出来的I2S信号,会被同时送到数字音频编码芯片CS8402和模拟DA转换芯片AK4393,转换出音频信号。模拟和数字输出通道的音频信号将同时输出[2]。

音频接口采用了标准的I2S音频总线接口传输音频数据。I2S主要用在音频编码、解码的数据传输部分。早期的音频编解码转换数据传输采用16位并行数据总线。随着音频采样技术的发展,量化精度进一步提高,目前的数字音频采用的是24 bit量化标准。这就意味着并行传输需要24位并行数据总线,很不方便。为了简化音频设备之间互相传输数据的流程,设计了串行输出的数据格式I2S。

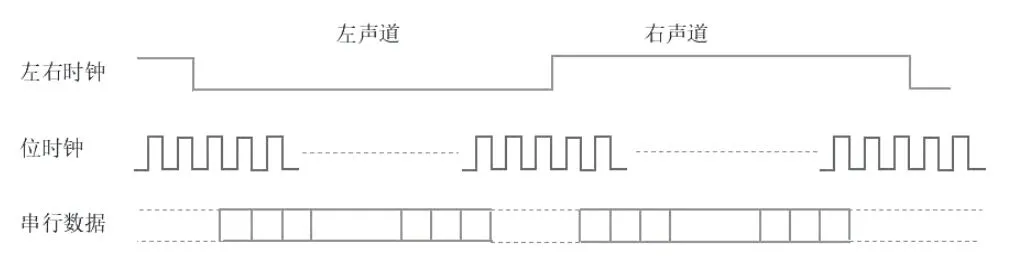

音频信号数字采样后,I2S格式采用3线的方式传输,也就是提供了2个时钟线和1个数据线(见图3)。其中一个时钟是左右声道时钟(LRC),为“0”时表示左声道,为“1”时表示右声道;另外一个时钟是数据位时钟(BCLK),在时钟上升沿采样每一比特位音频样点数据;串行数据在每一个通道传输32 bit,I2S用其中的24 bit,数据最高位在LRC时钟上升/下降沿延迟一个位时钟后顺序发送[3]。

图3 I2S格式波形时序图

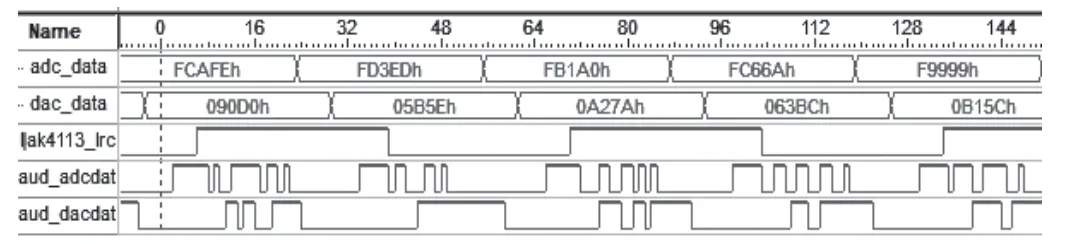

数字音频I2S发送模块是将I2S数据格式的信号转成20位并行的音频数据,接收模块是相反的过程,将并行数据串化为I2S格式。采用verilog语言进行时序编写,收发环路测试时,从SignalTapII上抓取到的波形图来看(见图4),收发的时序满足使用要求。

图4 波形图

2.2 系统时钟模块

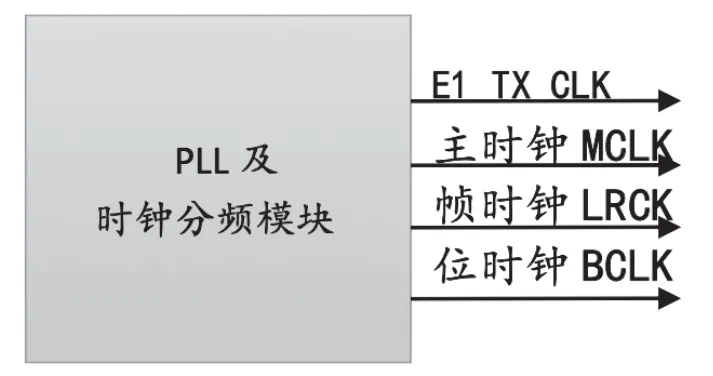

锁相环(Phase Locked Loops, PLL)时钟模块(见图5)通过调用FPGA内部的PLLIP核来实现,输出1个频率为12.288 MHz的时钟,作为音频编解码的主时钟MCLK。

图5 PLL锁相环及时钟分频

对主时钟进行六分频,得到2.048 MHz的时钟,用于E1接口的数据收发同步时钟。

对主时钟进行256分频,用作I2S的帧时钟;进行64分频,产生数字音频位时钟。

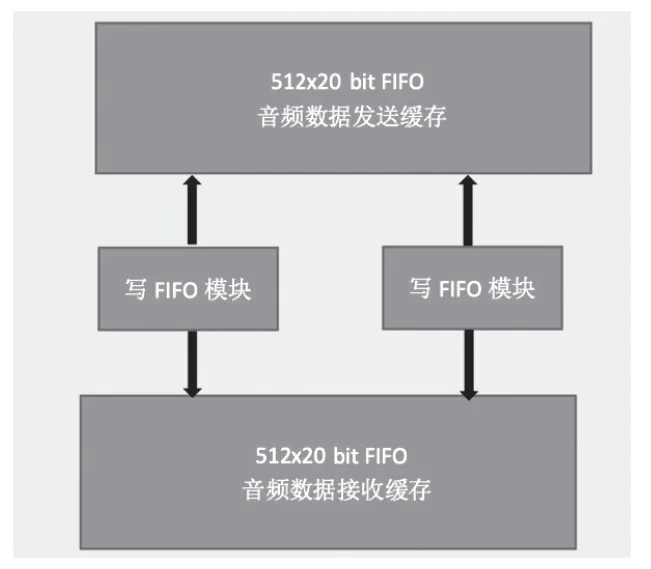

2.3 音频缓存发送/接收模块

音频数据缓存结构(见图6)用于缓存20位的音频样点数据,当缓存的数据量达到预设值之后,控制发送/接收模块开始发送/接收音频数据。

图6 音频数据缓存结构

缓存部分没有采用外置的随机存取存储器(Random Access Memory, RAM)或者只读存储器(Read Only Memory, ROM),而是使用FPGA内部逻辑单元构成的先进先出队列(First Input First Output,FIFO)。FPGA使用的FIFO一般指的是对数据的存储具有先进先出特性的一个缓存器,常被用于数据的缓存或者高速异步数据的交互,即所谓的跨时钟域信号传递[4]。采取顺序写入数据,顺序读出数据的方式,使用起来简单方便。

收到I2S模块转换过来的20 bit音频信号数据后,控制写FIFO模块写入512个字节的FIFO中。同时判断FIFO缓存的个数,超过预设值,控制E1发送模块开始发送数据。

从E1线路恢复出来的20 bit音频数据被连续写入音频接收缓存,接收完单包数据后再开始读FIFO,防止FIFO为空时被读取。接收完单包数据后给出完成标志,指示I2S接收模块转换音频数据。

2.4 E1线路发送模块

2.4.1 发送模块状态机

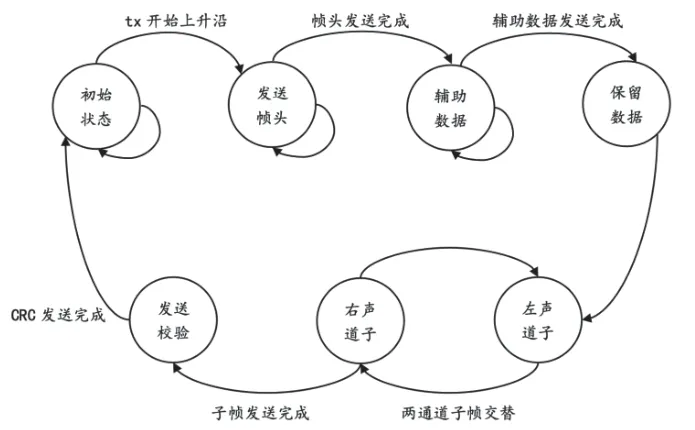

E1线路发送模块收到来自缓存模块的开始发送指示后,开始逐帧发送数据。发送数据的过程采用状态机来进行描述(见图7),将整个过程分为7个状态。每一个状态完成后,将跳转到下一个状态。

图7 E1数据发送模块状态转化图

发送时没有接收到发送指示,状态机将一直处于初始状态。在收到发送指示信号上升沿,跳变到帧头发送状态,依次发送XY帧头、辅助数据和保留数据。发送模块的代码中定义了数组来存储E1的帧头、辅助数据及保留数据,在系统复位时将初始化数组的值。辅助数据标识用于说明子帧数据格式中的4 bit辅助数据用途,定义为2位二进制数。“00”表示音频模式;“01”表示语音模式;“10”表示加强纠错模式;“11”为未来预留。保留数据共10 bit,默认值为全零。

发送通道音频子帧时,会分别发送左右声道对应的21 bit子帧。采用乒乓方式交替发送,直到96个子帧发送完成,进入校验码发送状态。每发送完一帧数据后,两种帧头X和Y将会交替使用[5]。

2.4.2 HBD3编码

数据流在2.048 MHz参考时钟串行发送后,为了满足信道的传输,还需要对数据流HBD3编码。在E1线路传输时,发送的数据帧不能直接在线路传输,会引起很大的误码,影响接收端还原数据。在数据流出现长串“0”时,接收端长时间收到低电平,没有时钟跳变,就不能恢复时钟。HDB3编码解决了这些缺点,当原信码出现长连“0”串时,进行数据双极性高密度编码,比其他码型更适合E1线路传输。

2.4.3 CRC32校验模块

循环冗余校验码(Cyclic Redundancy Check,CRC)一共4 bit,添加在数据帧的末尾。采用校验和算法,用于检测消息是否被修改以及进行数据纠错。校验码生成多项式为X4+x+1产生。E1编码发送端校验编码器的输入是一帧中的全部音频数据,即96个音频字,1 920 bit产生一个4 bit校验字。

当E1接收解码端检测到校验码发生错误时,将主动重复前一帧的音频数据,防止数据流出现中断,引起音频信号断续播放。

2.5 E1线路接收模块

2.5.1 接收模块状态机

E1线路接收模块收到数据后,进行时钟数据恢复。然后对数据进行双极性解码,恢复出整个数字音频数据帧。

在进行音频数据接收时,仍然用verilog语言编写状态机。接收的过程和E1数据发送模块状态转化正好完全相反(见图7)。

接收空闲时处于idle状态,直到数据输入指示后跳入帧头接收状态。这一步是恢复数据的关键,出错后将会导致后面的音频数据乱序,出现爆破音。连续不停地进行数据接收判断,看X帧数据“111010111001000”和Y帧数据“0001010001101111”是否出现。出现后依次跳转至辅助数据接收状态和保留数据状态,完成后就开始进行AB音频数据子帧的恢复。这里左右声道的数据帧按照乒乓的方式进行接收,分别将数据存到对应的缓存区。完成所有数据帧接收后,进行整个数据帧的校验和计算。如果计算结果和接收帧末尾的校验码不吻合,判断这一帧数据错误,主动重复前一帧的音频数据;如果结果吻合,就进入下一个E1数据帧的接收。

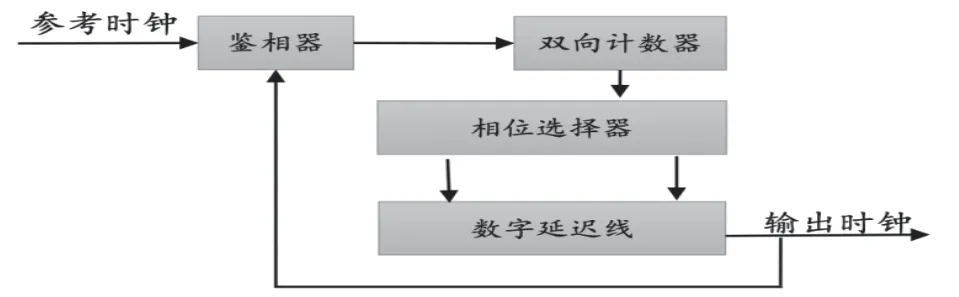

2.5.2 延迟锁相环

在接收来自发送端的数据时,经过长距离的传输,必须解决接收端和发送端时钟一致性的问题。这时两边的参考时钟频率是有差异的,必须采用数字延迟锁相环进行锁相(见图8),使收端和发端的时钟频率保持一致。

图8 数字延迟锁相环

鉴相器将E1线路的输入时钟和设备参考时钟进行比较,产生相位差控制接收端输出时钟变化。当二者的频率完全相等时,相位差将保持恒定,收发时钟完全同步。准确产生恢复时钟后,就可以在适当的间隔对输入信号进行采样以恢复音频数据。

3 传输测试结果

为了直观地反映音频信号经过一系列的编解码处理以及E1线路传输之后引起的变化,对整个传输链路进行了测试。

(1)将音乐节目送入音频输入端,从E1信道传输后,用耳机监听接收端还原出来的音频节目,声音无断点、无底噪、音质无损,满足节目传输需求。

(2)将标准测试信号送入音频输入端,从E1信道传输后,将接收端还原出来的音频信号送入标准音频分析仪进行指标分析,测试结果如表1所示,完全满足国家广播甲级标准。

表1 音频指标测试结果

4 结语

基于E1信道传输的音频编解码器,采用了数字处理芯片及大规模FPGA,集成度和稳定性很高,能够低失真地播出节目。利用SDH、PDH、微波的2M通道,可以实现点对点传输音频节目。配合E1接口分配器,还可以实现一发多收的广播式传输音频节目。可以在省、市、县、乡级地区组网,实现超长距离传输音频。通过E1信道的时分复用特性,还可以任意在指定的区间添加其他节目和控制指令,为以后设计升级提供思路。