基于AD9361的数据采集与回放系统

罗义军,许 强

(武汉大学电子信息学院,湖北武汉 430072)

0 引言

随着电子信息产业的高速发展,电子行业对数据采集回放系统提出了更高的要求,数据采集回放系统广泛应用于通信、雷达等科研领域,目前正朝着高速、高精度和高集成度的方向发展[1]。数字通信环境每时每刻都需要对信号进行采集回放处理,通过该系统可将无法实时处理的信号存储后再处理以及将采集的信号在其他地点重现[2]。随着5G建设进程的不断加快,在各种通信测试中,需要产生特殊多变且更高频的信号用以检测产品以及设备的性能指标。因此,设计一种可以根据用户的需求,产生测试射频信号的信号采集与回放系统,具有较高的实用价值与应用前景。

文献[3]介绍了一种DSP+ADC的数据采集系统,通过以太网通信将数据传送给上位机。文献[4]介绍了一种以Flash作为存储介质的数据采集系统。这两种方案均缺少回放功能,并且DSP处理能力受限,Flash的存储速度与容量也远不如PCIe总线。文献[5]加入了回放功能,使用PXIe总线传输,速度大幅提升,但系统缺乏射频端的设计,无法覆盖更高的频段。文献[6]采用国产化器件,但功能还不够全面,系统的整体性能也不如采用当下主流器件的系统性能好。

基于以上背景,采取FPGA+AD9361的方案设计采集回放系统,两板之间通过FMC接口(FPGA mezzanine card)进行数据和控制信号的交互[7]。选择这种设计的好处在于:射频信号的收发能够和FPGA的基带处理分开,便于验证采集回放子板芯片的功能。同时,可根据不同的项目需求选择相应的载板,具有良好的可扩展性,在设计上能够节约时间成本。

使用MicroBlaze软核可通过动态软件编程配置硬件设备,在不改变硬件系统的前提下,利用软件开发实现其平台不同的功能。充分利用AD9361的两发两收通道的特性,可实现快速频点切换且响应迅速的矢量信号源功能。

数据传输部分采用PCIe总线配合上位机,AD/DA端的低速数据通过DDR3缓存模块整合成高速数据后与PCle总线交互,实现大吞吐量的数据传输功能。DDR3封装为SODIMM,容量为8 GB。PCIe接口采用PCIe2.0x4接口,可提供的带宽最高可达2 GB/s。

1 系统整体设计

1.1 系统整体结构

整个系统的结构框架如图1所示。图1左侧为射频信号收发模块,负责完成射频信号的放大、变频、采集回放、滤波等工作,是射频信号和基带信号相互转换的桥梁。接收部分采用零中频的架构。图1右侧为FPGA模块,该模块带有FMC接口,与采集回放子板相连,负责接收和发射基带数据,同时缓存上位机编译后的指令,让CPU进行取指操作完成芯片初始化。

图1 系统结构框架图

PC上位机配合Uart模块,负责打印配置信息。PC上位机产生基带信号源经PCIe下发到射频捷变收发器的发射端,以产生适应性强的矢量信号源。采集数据流通过DDR3缓存后经 PCIe上行通道传输到PC上位机存储,再通过 PCIe下行通道经DDR3缓存后发送到 AD9361的发射端进行回放,实现信号的采集存储回放。

1.2 器件选型

高速信号采集子板是采集回放系统的重要组成部分,影响着系统的整体性能。本系统要求对频率范围70 MHz~6 GHz的射频信号进行接收处理和发送。根据奈奎斯特采样定理,为了抑制频谱混叠,直接采样要求采样率高达GHz,因此需要将射频信号下变频到零中频信号,再经过高速ADC芯片转换到数字域中处理[8]。

在AD936x同系列的芯片中,AD9363支持的工作频段较窄,AD9364仅有一条发射通道和一条接收通道。AD9361具有两发两收通道,有效位数12位,最高采样率达61.44 MSPS。综合考虑面积、通道个数、接口协议以及价格等方面,AD9361这款芯片最具性价比。

实现PC上位机与采集子板之间的高速数据交互与命令控制,可采用USB3.1、万兆网口、PCIe接口等方式。普通的PC机无法满足USB3.1和万兆网口的硬件需求。综合考虑传输速率、通用性、性价比,最终选取PCIe接口的传输方式。

本系统子板采用的芯片为AD9361射频捷变收发芯片,载板采用XC7K325TFFG900,外挂一片8 GB的DDR3内存条。PCIe 接口使用金手指插槽。载板与子板实物图及测试环境如图2、图3所示。

图2 载板与子板实物图

图3 测试环境

2 系统硬件设计

2.1 整体逻辑设计

本次开发采用K7系列FPGA内嵌的MicroBlaze软核处理器实现AD9361寄存器的配置。AXI-interconnect是CPU与各外设互联的AXI总线互联模块,接下来介绍的所有外设IP都需要挂在该总线桥上才能和MicroBlaze之间进行指令与数据传输。将AD9361的初始化配置参数用软件编译,编译指令缓存至内存空间BRAM,CPU访问内存获取指令驱动SPI、GPIO外设来配置AD9361。AD9361与基带数据处理底板之间的数据接口配置为LVDS,数据速率选择DDR(双倍数据速率)模式并使其工作在FDD模式[9]。据此设计了AD9361 RX/TX数据接口模块,AXI_Lite IP核来精准调整数据时延。UART模块结合APB Bridge完成PC端与FPGA的低速数据交互。DDR3作为PCIe总线高速传输数据的缓存。系统的逻辑设计顶层结构图如图4所示。

图4 系统逻辑设计顶层结构图

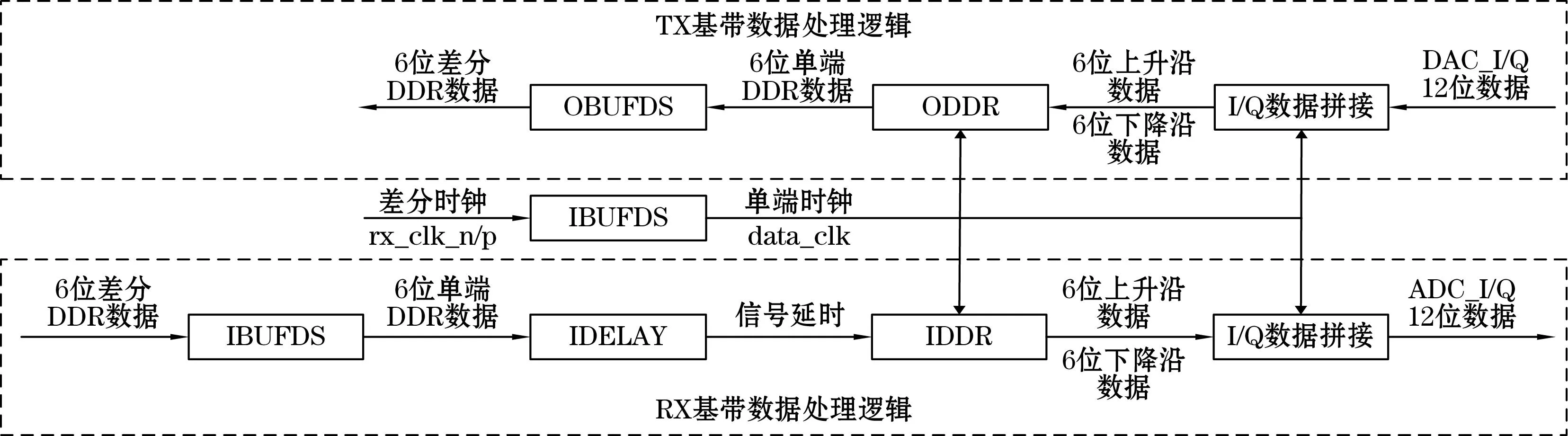

2.2 AD9361数字接口模块设计

在AD9361解除休眠状态后,会送给FPGA一个差分时钟DATA_CLK_P,该时钟的上升沿采样I路数据,下降沿采样Q路数据。DDR差分信号进入FPGA后要先经过IBUFDS原语将差分信号转为单端信号,数据转为单端后需要使用IDELAY原语将接收数据动态调整至随路时钟(data_clk)上升沿能够采到的位置,IDELAY原语需要配合IDELAYCTRL使用,IDELAYCTRL需要一个200 MHz的参考时钟,由FPGA底板上的50 MHz晶振经过锁相环产生,具体延时通过软件侧下发指令给AXI_Lite IP核来精准调整数据时延。经过测试,每延迟一个tap延时78 ns,本实验将tap值设为8。数据经过延时调整后要经过IDDR原语,原语使用SAME_EDGE_PIPLINE的模式。

以上为数字接口的RX接收部分设计原理,TX发射部分同理。AD9631的I/Q数据处理数字接口框图如图5所示。

图5 AD9361 I/Q数据处理数字接口框图

2.3 MicroBlaze及AXI总线互联模块设计

MicroBlaze是一款采用RISC指令集、哈佛体系结构嵌入式软核处理器[10]。MicroBlaze相当于在FPGA内部利用LUT等逻辑资源综合出一个CPU,在这个CPU上执行C语言配置AD9361的软件程序即可实现软件配置无线电平台的需求。

AD9361需要对其射频模块工作状态机部分进行控制才能使其正常收发射频信号。AXI_GPIO可以将逻辑部分的GPIO信号通过AXI总线接口与软件部分连接,软件部分通过AXI接口的地址映射找到GPIO外设,读写该IP核的控制寄存器即可控制逻辑部分GPIO端口的状态,从而配置AD9361的控制引脚。

AD9361提供了标准的四线SPI接口用于芯片内部寄存器的配置。根据AD9361芯片手册的SPI时序要求:tcp最小值为20 ns,表示SPI时钟最高50 MHz,逻辑侧产生该时钟不能超过这个值。

SPI时钟频率计算如式(1)所示,其中,ext_spi_clk时钟频率为100 MHz,频率比例设为16,经计算可得,主从设备之间用于配置寄存器数据的SPI时钟为6.25 MHz,满足要求的同时还留有足够时序裕量。

(1)

APB(advanced peripheral bus) 作为高级外设总线是AMBA协议之一,主要用于和低速以及低功耗的外设通信,该总线中唯一的主设备为APB Bridge,可以锁存总线所有的地址、数据和控制信号[11]。使用Xil_In32( )和Xil_Out32( )函数可以实现读取或写入内存数据,每次操作32位。基带数据处理模块的关键信息,通过异步FIFO转换时钟域,采用APB协议经Xil_In32( )函数读取到PC上位机,并转换数据格式在串口打印,方便检验通信系统的功能;同时,在PC端可由Xil_Out32( )函数写入数据,经APB协议和异步FIFO缓存初始参数,可实现PC端对基带源初始参数的设置。通过ad9361_spi_read( )可回读配置AD9361时关键寄存器的值,以此验证AD9361芯片的初始化情况。

2.4 PCIe传输与DDR3缓存模块设计

PCIe总线的主要功能为实现FPGA与PC上位机之间的高速数据交互与命令控制。由于传输速率不匹配,采集数据需要经过DDR3缓存后经PCIe上行链路上传至上位机。同理,回放数据通过PCIe下行链路下发至DDR3后配置AD9361芯片的发射端。

AD9361的一路I/Q的数据位宽为12 bit,其中有1 bit符号位,其余为数据位。两发两收一共48 bit的数据。为方便后续处理,将12位宽数据扩展符号位至16位,因此一共有64 bit的数据。

DDR3数据缓存模块复位后,数据缓存到模块内部的异步写FIFO中,将64 bit数据位宽转化为512 bit数据位宽。模块会监测上述写FIFO内的512 bit位宽的数据个数,当该FIFO缓存的缓存数据数量超过一个AXI写burst长度时,通过AXI AW/W/B 3个通道将FIFO缓存中的数据发送到DDR3中进行存储。同时使用读写指针wr_ptr、rd_ptr对DDR3中的数据块进行管理。通过AXI AR/R 两个通道将DDR3中的新数据回读到模块内的读FIFO中,方便后续的输出接口时序与位宽转换。

Vivado在设计上提供XDMA IP核,包含PCIe硬核和DMA功能。XDMA核提供AXI4-MM、 AXI-Stream和 AXI-Lite接口,其中AXI4-MM接口针对大流量数据读写,AXI4-Lite 接口可以传输吞吐量简单的命令信息,完全满足本次设计的需求[12]。

PCIe部分需要配置XDMA核。数据接口的位宽设置为64 bit,与DDR3缓存模块相对应。通道个数为4,最大传输速率设为2.5 GT/s。

3 上位机界面及使用

利用Visual Studio2017平台开发上位机,上位机的使用界面如图6所示。

图6 上位机使用界面图

将AD9361插入FPGA的FMC接口,再将FPGA板卡插入PC机的PCIe插槽。点击“启动设备”,运行日志显示“启动成功”则表示设备运行正常。接着点击“FPGA复位”,运行日志显示“复位成功”则表示设备恢复初始状态。打开Vitis软件,设置采样频率、接收本振频率、发射本振频率、增益、衰减、信号带宽等参数后,下载运行,即可配置AD9361。

在完成环境搭建、系统复位、AD9361芯片配置的准备工作后。根据不同的项目需求,在MATLAB生成所需的信号源文件。选择好保存位置后,点击“打开文件”,“发送信号”,就能通过PCIe下发信号源配置DAC端,从而实现适应性强的射频矢量信号源功能。将频谱仪连接到发射端,可观察发射信号的频谱。通过“停止发送”与“继续发送”可随时控制信号源的下发与暂停。发送信号源后,使用SMA射频连接线将TX1端与RX1端相连接,指定文件保存路径与保存数据大小,在选择“开始连续采集”按钮后,点击“数据上传”。即可将ADC端采集的数据上传到电脑的指定文件夹中,实现采集存储的功能。将采集的数据文件复制到指定文件夹中,再一次选择“打开文件”,点击“发送信号”,此时完成回放的功能。将DAC端通过SMA连接线连到频谱仪上,检验回放结果的正确性。

4 系统测试

4.1 单音信号测试

使用Vivado自带的DDS IP核生成基带信号源,频率为1 MHz。使用SMA射频线连接AD9361的TX1端与RX1端,实现射频信号自发自收。设置采样频率为40 MHz,接收本振与发射本振均设为2 GHz。打开上位机程序,分别设置文件保存路径、数据大小,等待上传。此时,抓取发射端与接收端的基带信号以及DDR3缓存信号,如图7所示。由图7可知,发送与接收端的基带信号I、Q两路均符合相移90°的特性,且pcie_data_in_rdy握手信号拉高时,DDR3正确缓存采集信号。将上位机接收的数据文件导入MATLAB中,并作FFT频谱分析分析。自环得到的1 MHz的基带信号频谱如图8所示。

图7 单音信号测试抓取基带信号及DDR3缓存信号ILA图

图8 单音信号自环测试基带频谱图

基带信号中心频率为0.996 091 MHz,误差为0.4%。

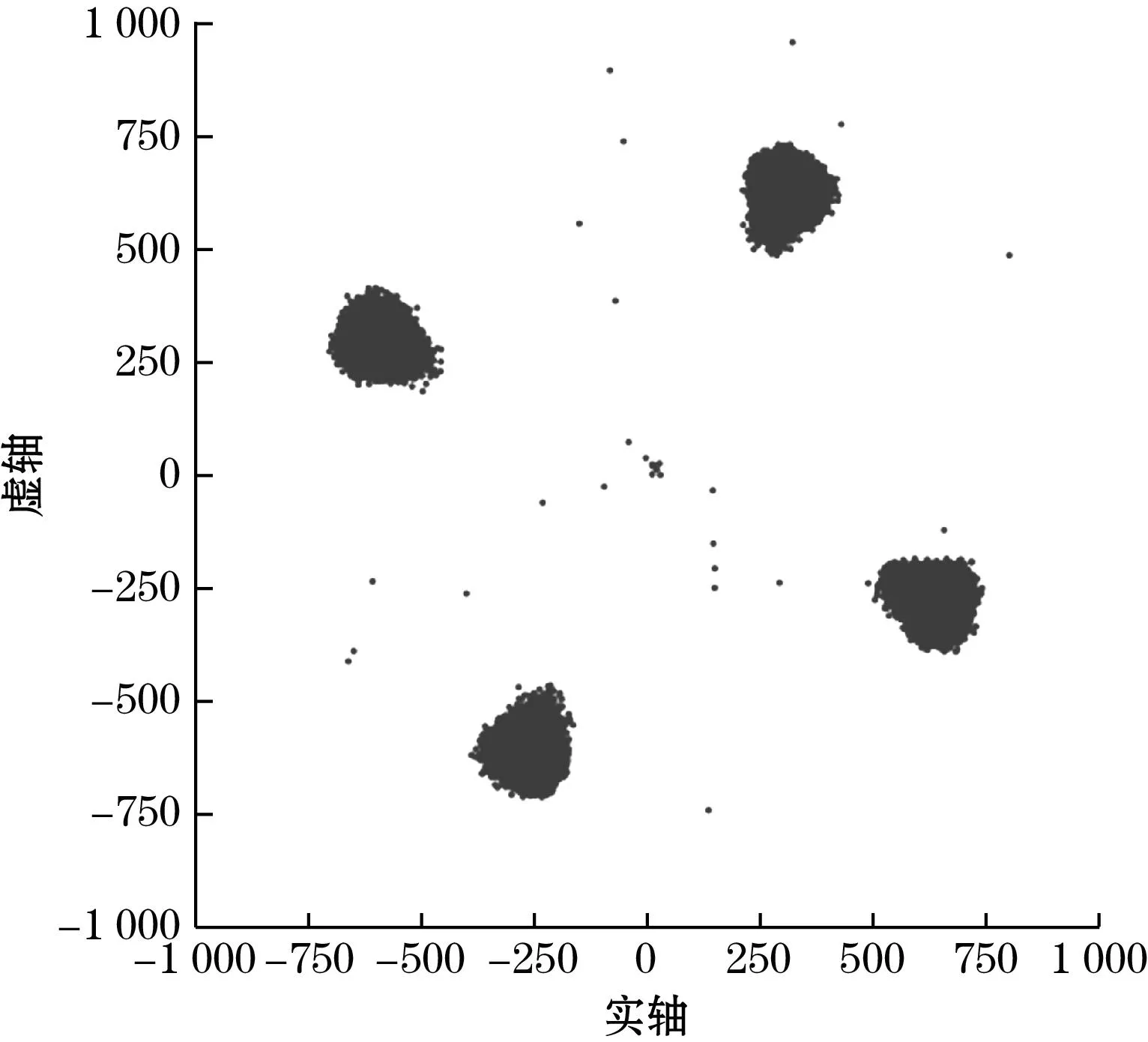

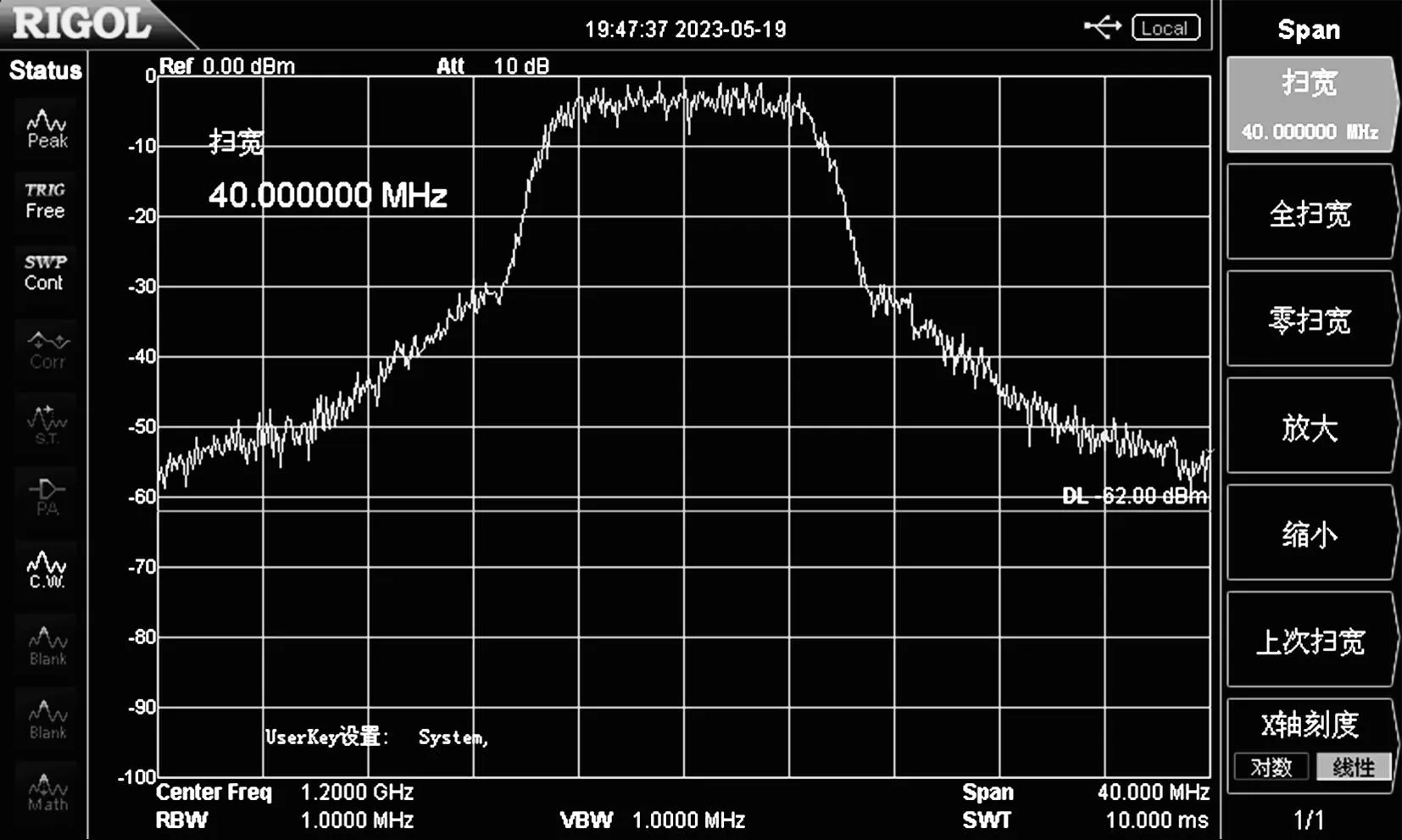

4.2 QPSK信号测试

MATLAB产生零中频的QPSK调制信号源,符号速率分别设为2.5 Mbit/s与10 Mbit/s。成型滤波器选择根升余弦滚降,滚降系数α设置为0.2。信号的带宽约为符号速率的1.2倍。将I、Q两路的数据导出,并保存为文本格式后由PCIe下发给AD9361的发射端。Vitis软件中设置采样频率为40 MHz,接收本振与发射本振均设为1.2 GHz。抓取发射端与接收端的基带信号以及DDR3缓存信号,如图9所示。

图9 QPSK信号测试抓取基带信号及DDR3缓存信号ILA图

将SMA回环线连接TX1A端和频谱仪,发射的QPSK信号频谱如图10所示。由图10可以看到AD9361将待发射的零中频QPSK信号的中心频率搬移到1.2 GHz处。频谱扫宽为40 MHz,无杂散动态范围均约为60 dBc。结果符合预期。

(a)符号速率为25 Mbit/s

(b)符号速率为10 Mbit/s图10 AD9361发射QPSK信号频谱图

自环得到的零中频信号由PCIe接口上传至上位机,导出数据文件后使用MATLAB作FFT频谱分析,如图11所示。采集信号频谱的主瓣宽度与发射端的QPSK信号频谱带宽基本一致,且旁瓣抑制效果满足要求。

(b)符号速率为10 Mbit/s图11 QPSK信号自环测试基带频谱图

为了证明接收数据的正确性,对接收的QPSK基带数据进行解调,数据经过预处理、数字滤波后,解调映射的星座图如图12所示。根据解调映射星座图,可见数据映射于4种相位附近,综合图9~图12结果,证明QPSK闭环通信成功。

(a)符号速率为2.5 Mbit/s

(b)符号速率为10 Mbit/s图12 QPSK信号解调星座图

将采集信号存储为文件到硬盘中,接着在上位机信源数据文件选项中打开上述文件。通过PCIe下发到AD9361的发射端进行回放。连接TX端至频谱仪观察回放信号的频谱,如图13所示。从图13可以看到,回放的QPSK调制信号与PCIe下发的信号源基本一致,但是带外谐波抑制稍差一些,仍满足系统的要求。

5 结论

本系统依托FPGA+AD9361设计了数据采集回放系统。经测试,该系统可根据用户需求,生成相应的射频矢量信号源,具有一定的通用性。可实现宽频段信号的采集与高速存储,同时回放具有抗干扰能力强、稳定性良好的优势。检验了PCIe数据传输通道的上行与下行,传输速率高且结果准确。

(a)符号速率为2.5 Mbit/s

(b)符号速率为10 Mbit/s图13 QPSK信号回放频谱图

此平台可作为一个良好的数字通信半实物仿真验证平台,对于复杂电磁环境下实现射频信号的高速采集、发射特殊多变的射频信号模拟不同通信环境、频谱监测、通信算法的研究与验证等领域具有十分重要的意义。