IC 设计中时序约束的自动化传播方法

巢 玮,徐 勇,杨 凡,吴浩泽

(1.哈尔滨工业大学(深圳),广东 深圳 518055;2.深圳国微芯科技有限公司,广东 深圳 518053)

静态时序分析(Static Timing Analysis,STA)作为电路设计中重要的时序验证方法,用来确保电路的功能运行在不同工作环境下都能符合设计的预期目标。在STA 时,一个完整的设计将被分解为数条不同的时序路径,通过计算每条路径上的信号传播延迟来验证在设计内部以及设计输入输出端口的时序情况是否符合给定的时序约束。时序约束是设计者根据不同设计的具体情况,设置一定的约束指标来模拟所设计电路的实际工作环境。STA 通过分析设计中时序路径的时序情况,确保所设计的电路能够正常工作在对应的工作频率下而不产生时序违例。

1 层次化电路设计与时序分析

随着电路集成密度的提高以及电路结构复杂程度的指数性增加,层次化架构设计已成为重要的电路设计方法[1]。在层次化架构的电路设计中,IC 顶层与下层模块的时序约束分别独立完成。时序约束的迭代与时序收敛的效率是芯片投片生产与产品上市时间的重要保证。随着工艺的愈发先进这一过程往往要设计者付出较多的时间和精力[2]。随着设计和制造工艺的不断进步,时序约束与时序收敛也迎来了新的挑战。如之前自主设计的芯片[3-4]尽管规模不算大,但时序约束及时序收敛依然经历了数次迭代,这部分较重复的手工迭代在一定程度上降低了芯片设计效率。

研究表明,精准的时序约束能有效避免不真实的时序违例及不必要的时序修复所带来的面积增加问题,从而减轻电路后端设计的工作量[5]。随着制造工艺的进步和电路设计复杂度的提高,时序收敛的难度及迭代周期都迎来了新的挑战[6]。为了准确地对电路进行分析并去除部分特别悲观和特别乐观的场景,时序分析方法经历了从工艺偏差方法学到先进的片上误差方法学,再到统计学片上误差分析的演进[7-9]。在超大规模集成电路中,单位面积中晶体管的数量呈指数性增长,基于时序约束的布局布线变得愈发复杂并有着庞大的计算量[10-12],实验表明,精准的时序约束能有效减少迭代从而缩短芯片设计的周期。

时序约束按照约束类型通常可分为三类,分别是时钟约束、端口约束以及时序例外约束。其中时钟约束是静态时序分析的基础,如在时钟MUX 的研究中[13],对常见的几种电路结构的时钟约束进行了分析与比较。此外,一种时钟约束的传播的方法被应用在了低功耗的异步RISC-V 处理器上,通过传播时钟与生成时钟对异步电路进行时序分析[14]。文献[15]介绍了一种静态时序验证方法,可以较早、快速、精确定位FPGA 端口时序设计存在的问题,从而缩短了验证时间,提高了验证效率、准确性和覆盖率。对于特殊的时序路径,需要通过时序例外约束进行定义,从而使得工具在STA 时能够使用正确的参数及指标分析特殊的时序路径[16]。

2 时序约束的自动化传播

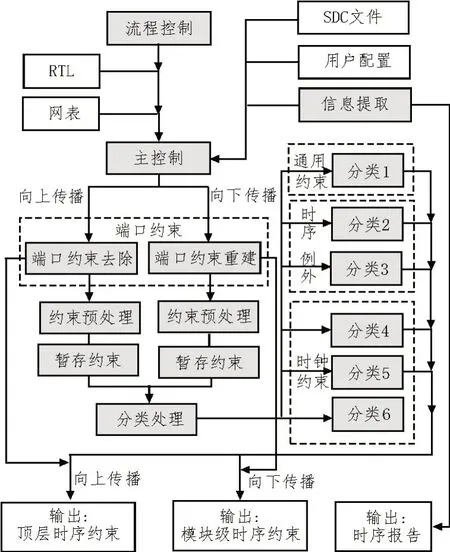

由于时序约束的多样性,同一类型的时序约束彼此之间的参数与选项可能存在较大差异,为实现时序约束在顶层及模块间的自动化传播,使用了业界标准Synopsys 设计约束(Synopsys Design Constraints,SDC)文件作为时序约束的标准。同时在时序约束分类的基础上,根据SDC 文件中时序约束的参数与选项结构,对分类进行了细化。根据SDC 中参数与选项结构的差异,该自动化流程将时序约束分为四大类,分别是通用约束、端口约束、时序例外以及时钟约束,如图1 所示。根据不同时序约束的类型,将除端口约束外的时序约束细分为六个分类,每个分类的时序约束都具有相似的结构与选项。在流程图中,白色框代表着输入和输出,灰色框表示自动化传播方法[17]。

图1 时序约束的自动化传播流程图

2.1 端口约束

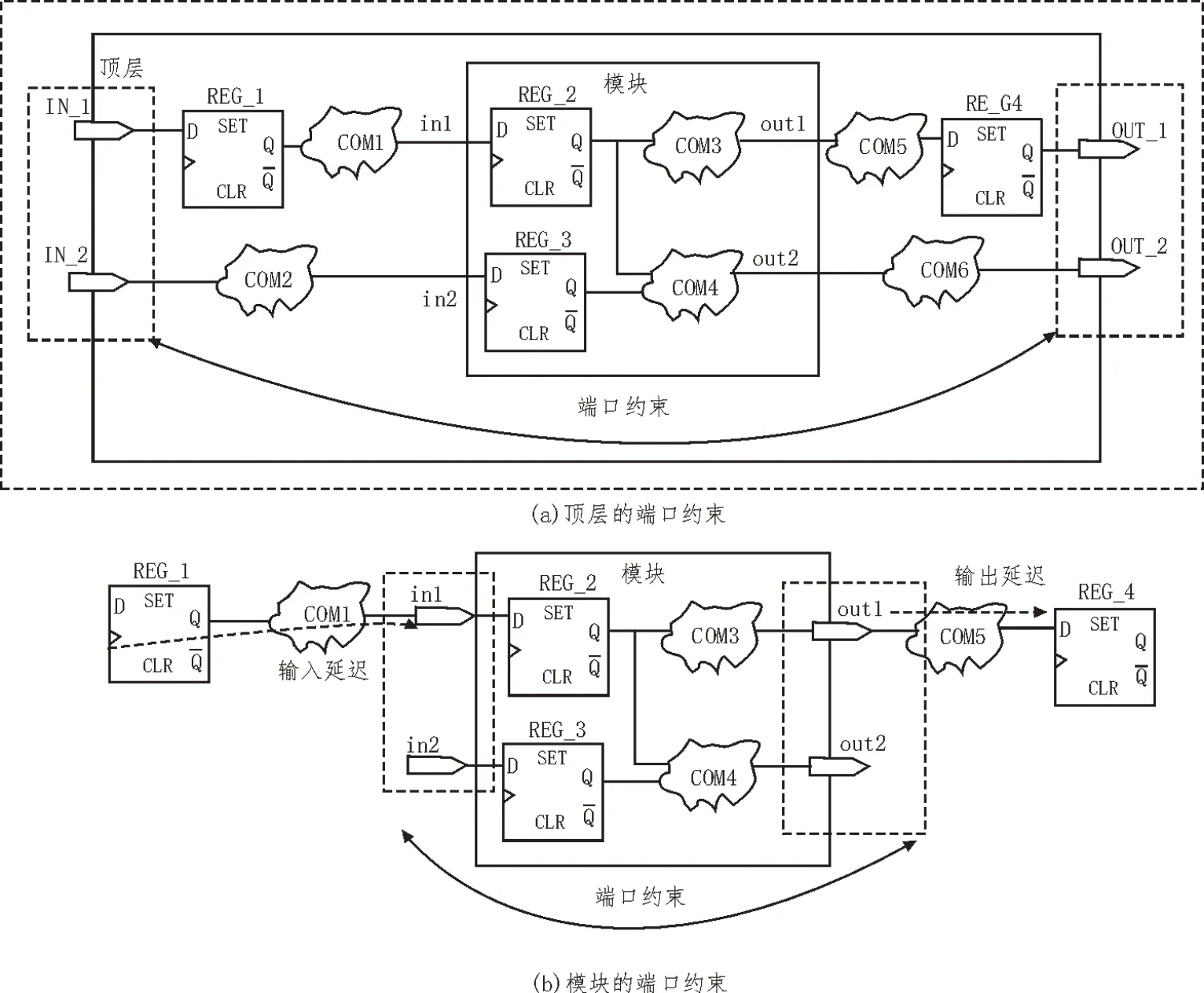

端口约束是用来描述端口外部延时、电容等信息以更准确地贴近电路的实际工作情况。因此,端口约束与时序分析的场景息息相关,不同时序分析的场景的端口可能存在较大差异。如图2(a)所示,在顶层的端口为IN_1、IN_2、OUT_1 以及OUT_2。当时序约束向下传播时,时序分析的场景从顶层变为模块,此时模块外的顶层电路将不再需要时序分析,且模块的输入输出引脚变为端口。为了准确分析模块的时序,模块时序约束需要对模块端口in1、in2、out1 以及out2 进行重新约束。

图2 端口约束在顶层与模块之间的差异

如图2(a)所示,假设顶层端口IN_1 与OUT_1 端口的输入延迟与输出延迟约束如下:

其中,$IN_1_delay 和$OUT_1_delay 分别对应端口IN_1 与OUT_1 的输入延迟与输出延迟,$IN_1_clock 和$OUT_1_clock 则分别对应端口外时序路径起点与终点的时钟。当时序约束向下传播时,由于模块端口in1 与out1 与顶层端口的约束不存在直接关联,将通过与端口相连的时序路径构建模块端口的等效延迟,因此可得到如下的输入延迟与输出延迟:

在不考虑线延迟的情况下,模块端口in1 的输入延迟等于寄存器REG_1 的时钟到输出延迟$REG_1_CQ_delay 加上组合逻辑COM1 的延迟$COM1_delay。输入延迟的约束时钟为在顶层与in1 相连的寄存器REG_1 的时钟$REG_1_clock。模块端口out1的输出延迟等于组合逻辑COM5 的延迟$COM5_delay 加上寄存器REG_4 的建立时间$REG_4_setup。此时寄存器REG_4 的时钟$REG_4_clock则用来约束端口out1 的输出延迟。

在端口约束向上传播时,顶层时序约束文件中通常已经存在端口约束,所以无需对端口进行重复约束。

2.2 时钟约束

时钟约束是时序分析的基础,精准的时钟定义是时序收敛的重要依据。时钟约束包括了创建时钟、创建生成时钟等。在大型芯片设计中,由于工作场景与需求的不同,时钟频率与时钟结构往往多种多样。

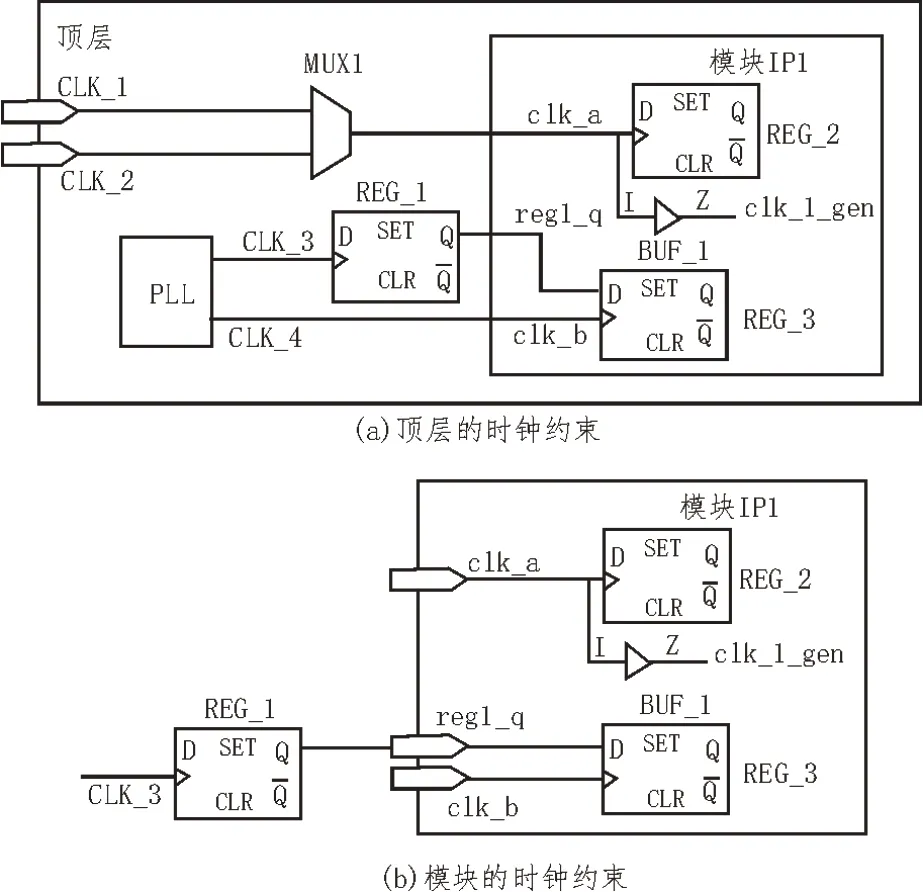

如图3(a)所示,顶层时钟由两个端口时钟CLK_1和CLK_2 以及两个PLL 时钟CLK_3 和CLK_4 组成。如果MUX1 的选择端不加以约束,则时钟CLK_1 和CLK_2 都能通过模块引脚clk_a 影响寄存器REG_2的时序。同时,模块引脚clk_a 的一个分支连接到了缓冲器BUF_1 并产生了一个时钟CLK_1 的生成时钟。另一方面,PLL 输出的时钟CLK_3 与CLK_4 之间存在一条时序路径从寄存器REG_1 到REG_3,而此时由于CLK_3 并没有直接连接到模块上。当进行模块级的时序分析时,需要创建CLK_3 的虚拟时钟以补全该条时序路径确保时序分析的正确性,如图3(b)所示。

图3 时钟约束在顶层与模块之间的差异

假设图3(a)的顶层的时钟有如下约束:

其中,每个时钟都有对应的时钟周期$CLK_period 以及波形$CLK_WF。当时钟约束向下传播时,与模块有直接连接关系的时钟CLK2 将根据电路结构等效传播至模块上。而CLK3 虽然没有连接到模块上,但其构成的时序路径与模块存在交互,故需要创建虚拟时钟,以此来对模块端口reg1_q 进行约束从而分析从寄存器REG_1 到REG_3 的时序路径。端口约束中对输入延迟的时钟约束将与这里定义的虚拟时钟名字自动保持一致,无需人为调整。此时,对应的模块时钟约束如下:

在时钟约束向上传播时,模块端口所创建的时钟以及模块所设置的虚拟时钟通常并不是顶层时钟的起始点,因此这些时钟及其对应的时钟不确定性等属性均不需要向上传播。相反,模块内部的时钟通常为时钟真正的起始点,如时钟门后的生成时钟、IP 内部PLL 所产生的时钟等。这些时钟在向上传播时,需要根据电路层级结构的改变进行对应的调整。

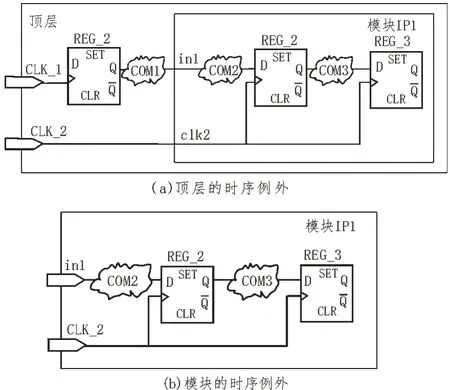

2.3 时序例外

在时序分析中,有时一些特殊的时序路径需要通过时序例外约束进行差异化分析,从而使得工具在STA 时能够使用正确的参数及指标分析特殊的时序路径。时序例外包括伪路径、多周期路径等。时序例外可设置在标准单元及其引脚上,也可设置在端口或时钟上。因此时序例外在顶层与模块间传播时,准确地获取标准单元的层级路径,灵活转换端口与引脚显得尤为重要。

由图4(a)可知,寄存器REG_1 与寄存器REG_2之间存在大量组合逻辑COM1 与COM2。假设时钟CLK_1 与CLK_2 是同步时钟且寄存器REG_1 与REG_2 之间需要数个时钟周期才能完成,那么它们之间存在多周期路径,可由如下时序约束描述:

图4 时序例外在顶层与模块之间的差异

这里的$setup_cycle 和$hold_cycle 分别对应了在建立时间检查时所对应的周期数以及保持时间检查时所对应的周期数。当时序例外向下传播时,完整的时序路径被模块的端口分为两部分,顶层的电路结构在模块级将不再可见,此时根据该条时序路径的电路结构,可以获取其在模块端口上的等效点,重新定义模块的时序例外,同时模块内标准单元的层级结构也随之改变。对应的模块时序例外如下所示:

当时序例外向上传播时,由于时序路径的补全,在时序分析时将多出一些额外的时序路径。为了模块的时序约束传播至顶层时不影响到顶层其他时序路径,此时序例外将仍旧停留在模块及其内部,并将从端口起始的路径从起点改为经过点,并将端口重新改为引脚。模块时序例外等效的新顶层时序约束如下所示:

3 实验结果与分析

该时序约束的自动化传播方法不论在测试用例还是工程项目中均能准确而高效地生成对应的时序约束。在实验的过程中,使用的测试电路一共有三个,分别是一个两百多标准单元的测试用例、一个约一万标准单元的工程用小型数字电路以及一个约六十五万标准单元的工程项目电路。每个测试电路都有一个顶层时序约束SDC 文件以及一个模块级时序约束SDC 文件,分别对应了时序约束向下传播时所需要的顶层时序约束以及时序约束向上传播时所需要的模块级约束。为了更好地贴近时序约束在芯片设计中的实际情况,三个测试电路中使用了两个已经成功signoff 的工程项目的网表以及对应的时序约束进行测试。

实验结果如表1 所示,该时序约束的自动化传播方法在不同的IC 设计中均能准确地将时序约束在顶层与模块间进行等效传播,不论是实验用的测试用例还是实际工程中signoff 的IC 设计均能精确地实现时序约束的自动化传播。自动化传播所产生的时序约束经过与传统时序约束传播方式进行对比,结果表明,自动化产生的时序约束在功能上100%匹配人为手动所生成的时序约束。

表1 不同测试电路的测试数据

4 结论

该文提出了一种时序约束的自动化等效传播方法,能够根据顶层时序约束或模块时序约束自动生成另一层级对应的等效时序约束。该自动化方法减少了设计时序约束的人力成本,通过自动化的方法替代了重复繁琐的手工迭代,从而提高了时序分析与时序收敛的效率。从实验结果来看,该方法在测试用例与项目工程应用中均能准确地生成对应的时序约束,显著提高了时序约束设计的效率及自动化程度。