一种提高SGT MOSFET雪崩耐量的方法

唐 威,俱 帅,张 蕾

(西安邮电大学 电子工程学院,陕西 西安 710121)

屏蔽栅沟槽型金属氧化物半导体场效应晶体管(Shielded-Gate Trench Metal Oxide Semiconductor Field Effect Transistor,SGT MOSFET)作为功率MOSFET的一类,由于比导通电阻较低[1-2]和开关速度较高等特点[3-4],在电机驱动和锂电池保护等领域得到广泛应用[5-6]。当SGT MOSFET器件并入电力系统时,电路中寄生电感[7-8]存储的能量会在器件关断时刻引起高的电压脉冲,使得电路性能退化甚至器件被损坏。此时,器件漏端被冲击时所能承受的最大能量为功率MOSFET的雪崩耐量[9-10]。雪崩耐量是衡量功率MOSFET鲁棒性的重要性能指标之一。通常采用非钳位感性负载开关(Unclamped Inductive Switching,UIS)来测试衡量功率MOSFET雪崩耐量的大小[11-12]。

器件的雪崩耐量越高,意味着当器件在面临极端应用情况时,拥有的安全裕度越高,性能更加稳定,鲁棒性也越强。为了优化功率器件在UIS过程中的性能退化及失效行为,文献[13]采用极窄源区结构,显著地降低了P型体区电阻,使得UIS能力较传统沟槽MOSFET提升了30%,但是,该结构较传统结构增加了两张掩模版,且阈值电压(Threshold Voltage,VTH)很难控制;文献[14]采用倒L形N+源区,同样降低了P型体区电阻,UIS能力为传统沟槽MOSFET的2.1倍,但是,该结构同文献[13]一样,同样较经典结构增加了两张掩模版,开发成本较大;文献[15]采用漂移区P柱、自偏置降低表面电场技术的阶梯氧化层(Reduce Surface Field Stepped Oxide,RSO)结构,通过减少寄生基区电阻的空穴电流,降低了寄生三极管基区电阻的压降,使得UIS能力提高了83.3%,但是,该方法采用了多台阶场氧化层结构,增加了两次光刻和氧化硅回刻工艺,实现难度较大;文献[16]在沟槽间加入深P型基区,降低了寄生三极管基区传输效率,使得雪崩耐量增加了13.8%,但是,该结构较常规结构增加了一张掩模版,增加了开发成本,并且增加了器件导通电阻,影响了器件的性能。

为了在不影响器件关键参数和性能的前提下,提升器件的雪崩耐量,并同时降低设计成本,本文拟提出一种提高SGT MOSFET雪崩耐量的方法。通过增加器件沟槽间接触孔宽度和深度、增加接触孔注入能量和剂量等方法降低P型体区电阻,从而增加器件在UIS过程中的通流能力。

1 UIS测试与分析

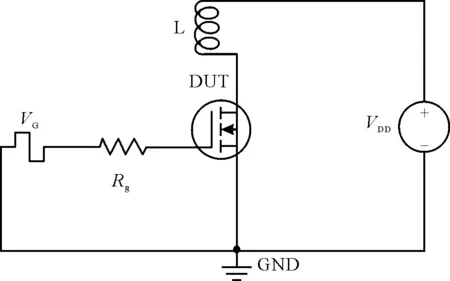

图1为功率MOSFET器件UIS测试电路原理示意图。其中,被测器件(Device Under Test,DUT),即功率MOSFET栅极和脉冲方波电压VG及栅极电阻Rg串联,漏极和负载电感L及电源VDD串联,DUT源极与电源负极相连接接地,表示为GND(Ground)。

图1 功率MOSFET器件UIS测试电路原理示意

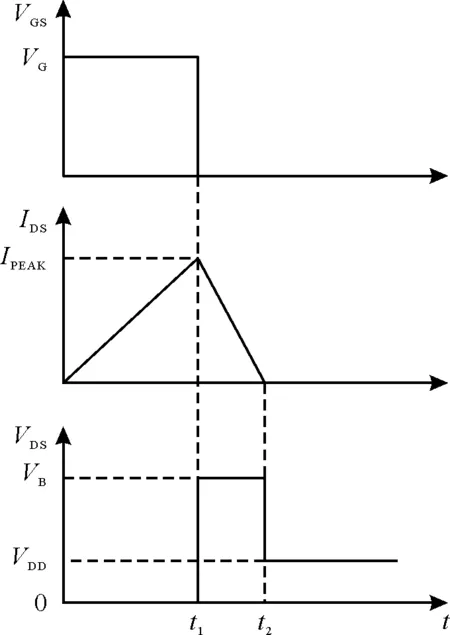

使用VGS、VDS和IDS分别表示功率MOSFET在UIS过程中器件的栅极电压、漏源电压以及漏源电流。在UIS过程中,MOSFETVGS、VDS和IDS变化示意图如图2所示。 在0~t1时刻,脉冲方波电压接高电平VG,DUT导通,电感开始充电;在t1时刻,脉冲方波电压由VG转为低电平,DUT关断,漏源电流升至雪崩电流IPEAK。由于电感电流无法突变,为维持电感电流持续泄放,DUT被迫进入雪崩击穿状态,此时,DUT漏源电压升至击穿电压(Breakdown Voltage,VB),漏源电流由IPEAK开始下降,直到t2时刻,存储电量被DUT消耗,此时,器件漏源电压将保持为电源电压VDD。

图2 UIS过程中MOSFET VGS、VDS和IDS变化示意

在t时刻,器件单次脉冲雪崩能量EAS的计算表示式为

(1)

目前,EAS测试方式主要是固定电感大小,通过不断增加DUT栅极方波电压高电平脉宽,获得使得器件刚好不失效的IPEAK值[12],然后,再根据式(1)获得器件的EAS能力值。

以上分析都是在器件不失效前提进行的。当器件在关断时刻遭受负载电感冲击而失效时,若打开失效器件的塑料封装外壳观察失效位置,可以发现失效点主要集中在器件边缘和中间位置。当失效位于器件边缘即终端位置时,表明器件终端击穿电压小于器件元胞,在关断时刻,负载电感在漏端引起瞬态电压脉冲,使得器件耐压较小的终端首先被击穿;当终端耐压大于元胞时,器件则在UIS过程中击穿于元胞区。

上述分析表明,器件终端击穿电压需要大于元胞,以避免在UIS过程中击穿点转移,从而增加器件雪崩耐量[17]。因此,在确定终端沟槽间距即台面(Mesa)宽度时,通常按照元胞区Mesa的75%进行设计,以确保SGT MOSFET能够获得较为稳定的击穿特性[18],从而使得终端击穿电压大于元胞。当器件在UIS过程中失效于元胞区,主要为栅极关断瞬间引起器件内部寄生三极管开启导致。此时,通过P型体区高剂量注入[7],应用窄N型源区,能够降低寄生三极管基区电阻,抑制寄生三极管开启,虽然这种做法提升了器件雪崩耐量,但是,牺牲了器件的部分直流性能[13]。

2 EAS优化机理

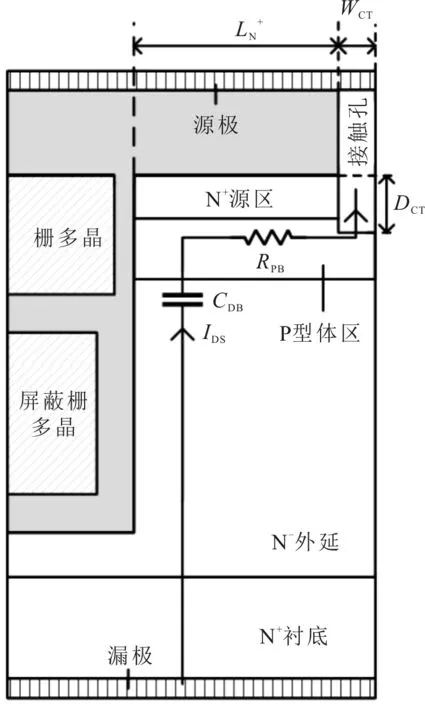

图3为UIS过程中SGT MOSFET元胞电流流径示意图。其中,LN+为源区横向宽度,WCT为接触孔宽度,DCT为接触孔深度,RPB为P型体区电阻,CDB为外延和P型体区形成的电容,IDS为UIS过程中器件的漏源电流。

图3 UIS过程中SGT MOSFET电流流径示意图

由于在UIS过程中,器件漏端存在较高的电压脉冲,漏源电流IDS借助CDB流动,此时有

(2)

式中,VD表示器件的漏端电压。

当该电流流经P型体区电阻时,电阻上的压降使得由N+源区、P型体区及N-外延构成的NPN寄生三极管发射结发生正偏,当电阻压降等于发射结内建电动势Vbi时,结内开始有注入电流。漏端能承受不导致产生注入电流的最大瞬态电压可以表示为

(3)

由式(3)可知,若减小SGT MOSFET结构中的P型体区电阻RPB,则可以使得器件获得更高的抗雪崩冲击能力,从而获得更高的雪崩耐量。

P型体区电阻值的计算表示式为

(4)

式中:ρSQ,PB表示包含N+源区补偿影响的P型体区方块电阻电阻率;Z表示器件沿沟槽方向P型体区方块电阻截面面积。

对于ρSQ,PB,由于空穴掺杂浓度NA远大于电子浓度ND,因此有

(5)

式中:σ表示P型体区方块电阻电导率;e表示单个电子所带电荷量,μn、μp分别表示电子迁移率和空穴迁移率;n表示P型体区电子的浓度;p表示多子空穴的浓度;NA表示P型体区受主杂质掺杂浓度。

结合式(4)和式(5)可以发现,为了抑制SGT MOSFET寄生三极管的开启,可以通过缩短N+源区宽度LN+、增加P型体区沟槽方向截面面积Z和P型体区杂质NA的浓度,以减小P型体区电阻RPB,从而使得器件获得更高的雪崩耐量。当器件沟槽间距固定时,缩短LN+的有效方法是增加接触孔宽度WCT,增加P型体区沟槽方向截面面积Z则可通过增加接触孔深度WCT实现。

另外,观察图3可以发现,SGT MOSFET源极接触孔深入P型体区并且将N+源区和P型体区短接,由于器件在接触孔刻蚀完成之后,会进行高浓度P型杂质注入以优化器件性能。因此,为了增加NA,可以增加接触孔注入剂量及能量,以降低P型体区电阻,从而达到增加IPEAK的目的。

3 EAS设计方案

所提设计基于一款耐压120 V SGT MOSFET,考虑到终端效应,击穿电压VB通常要求保留10%~15%余量[19],因此,将VB目标设定为135.0 V;对于器件所应用的同步整流电路,较低的阈值电压VTH有利于减小电路中体二极管导通损耗,并带来更短的延迟和开关时间[20],为此,将设计的目标阈值电压VTH定为2.0 V。

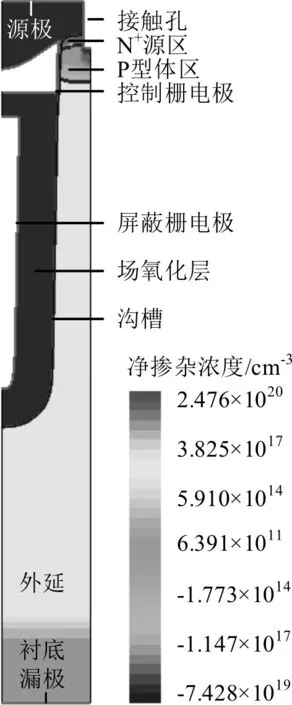

根据第2部分的分析结果,利用Sentaurus计算机辅助设计(Technology Computer Aided Design,TCAD)仿真软件对120 V SGT MOSFET元胞区接触孔宽度、接触孔深度、接触孔注入剂量和接触孔注入能量进行拉偏。由于SGT MOSFET元胞区内分布着大量重复且对称的元胞单元,因此,只针对器件半个元胞结构进行仿真分析,按照实际工艺流程搭建SGT MOSFET器件的半胞结构,仿真结果如图4所示。可以看出,器件的沟槽位于图4左侧,沟槽内上部为器件控制栅电极,下部为屏蔽栅电极,与源极设置同电位,器件源极位于结构顶部,底部为器件衬底,与漏极相连。

图4 器件半胞仿真结构仿真结果

3.1 接触孔宽度的设计

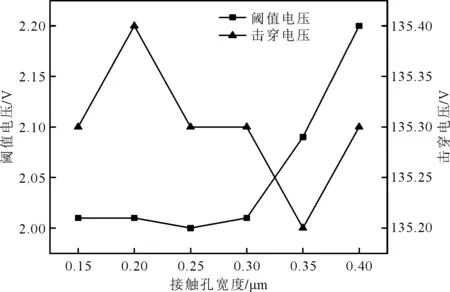

设计器件接触孔时,需要将N+源区和P型体区进行短接,以抑制元胞区寄生三极管开启。根据式(4),增加接触孔宽度WCT以缩短N+源区长度LN+,从而降低器件P型体区方块电阻阻值。此次拉偏范围选择0.15 μm~0.40 μm,图5为WCT拉偏对阈值电压VTH和击穿电压VB影响的仿真结果。

图5 WCT拉偏对VTH和VB影响仿真结果

从图5可以看出,随着接触孔宽度WCT的增加,因P型体区和N-外延构成的PN结电场强度保持恒定,器件击穿点仍位于沟槽底部,击穿电压VB基本稳定在135.3 V左右,虽有波动但变化不明显。对于阈值电压VTH,当接触孔宽度WCT由0.15 μm增至0.30 μm时,由孔注入的P型杂质并未影响到器件沟道受主杂质浓度NA,阈值电压VTH稳定在2.00 V左右;当WCT由0.35 μm增至0.40 μm时,孔注入P型杂质开始向沟道扩散,沟道处NA变大,VTH分别为2.09 V和2.20 V,并开始逐渐增加。为留够余量,固定接触孔宽度为0.25 μm,研究不同接触孔深度,器件阈值电压VTH和击穿电压VB的变化情况。

3.2 接触孔深度的设计

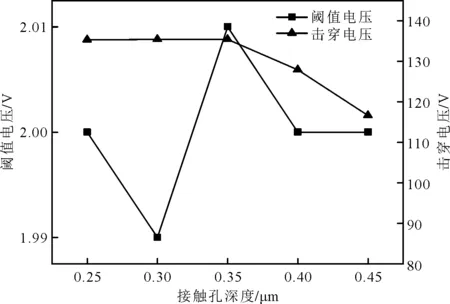

根据式(4),增加接触孔深度DCT可以增大P型体区方块电阻截面面积Z,从而降低器件P型体区方块电阻。此次接触孔深度DCT选择0.25 μm~0.45 μm进行拉偏,图6为DCT拉偏对VTH和VB影响的仿真结果。可以看出,随着接触孔深度DCT的增加,由孔注入P型杂质纵向扩散且未横向扩散至沟道,因此,器件阈值电压VTH稳定在2.00 V左右,虽然有所波动,但是变化不明显。

图6 DCT拉偏对VTH和VB影响仿真结果

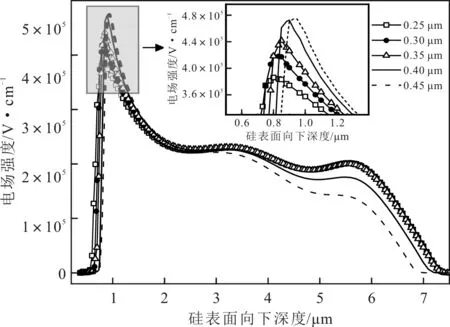

图7为从接触孔位置,沿器件硅表面垂直向下方向,DCT拉偏器件在不同深度条件下的电场分布图。

图7 DCT拉偏器件在不同深度电场分布图

如图7所示,随着接触孔深度DCT增加,器件接触孔底部PN结峰值电场不断增加,并且结面逐步向下移动。当DCT由0.25 μm增至0.35 μm时,因P型体区和N-漂移区构成的PN结峰值电场仍小于器件临界击穿电场,击穿电压VB基本稳定在135.4 V左右;在接触孔深度DCT继续由0.40 μm增至0.45 μm的过程中,PN结结面电场电场强度继续增加,并且超过器件临界击穿电场,器件击穿点开始向PN结面转移,沟槽底部器件电场强度下降,因此,使得击穿电压VB下降。为了留够余量,固定接触孔宽度为0.30 μm,接下来,将研究接触孔注入不同剂量时,器件的阈值电压VTH和击穿电压VB的变化情况。

3.3 接触孔注入剂量的设计

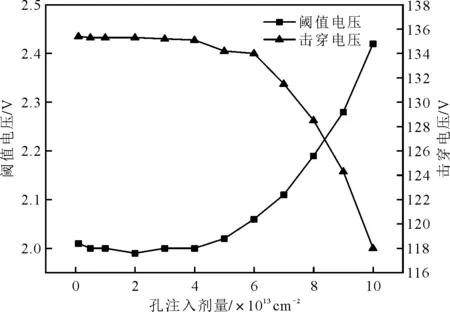

此次接触孔注入选择两步注入工艺。第一步为低能量注入,在20 keV左右较低能量条件下注入二氟化硼(BF2)。第二步为高能量注入,在较高能量条件下注入硼杂质。在注入过程中,BF2的主要作用是优化源极接触孔表面的接触电阻,因硼(B)的扩散系数较大,常用来降低P型体区方块电阻电阻率,以提升器件雪崩耐量。此处的拉偏操作只针对第二次注入的B杂质进行仿拉偏。注入剂量范围为1.0×1012cm-2~1.0×1014cm-2。图8为孔注入剂量拉偏对器件阈值电压VTH和击穿电压VB影响的仿真结果。

图8 孔注入剂量拉偏对VTH和VB影响仿真结果

从图8可以看出,当孔注入的B杂质剂量由1.0×1012cm-2到4.0×1013cm-2变化时,因为沟道杂质浓度NA未被影响,导致器件的阈值电压VTH稳定在2.00 V左右;随着孔注入剂量由5.0×1013cm-2增加至1.0×1014cm-2,由于退火后B杂质向器件沟道处扩散增加,使得沟道杂质浓度NA变大,因此,器件的阈值电压VTH开始增加。对于器件的击穿电压VB,因PN结峰值电场和杂质掺杂浓度成正比,当孔注入剂量小于5.0×1013cm-2时,器件耐压恒定在135.3 V左右;随着接触孔注入剂量由5.0×1013cm-2增加至1.0×1014cm-2,P型体区和N-外延构成的PN结峰值电场不断增加,当器件反向耐压时,击穿点开始向PN结转移,器件耐压不断降低,由134.4 V逐渐减小至118.1 V。为了留够余量,固定接触孔注入剂量为4.0×1013cm-2。接下来,将研究在接触孔注入能量不同的条件下,器件的阈值电压VTH和击穿电压VB的变化情况。

3.4 接触孔注入能量的设计

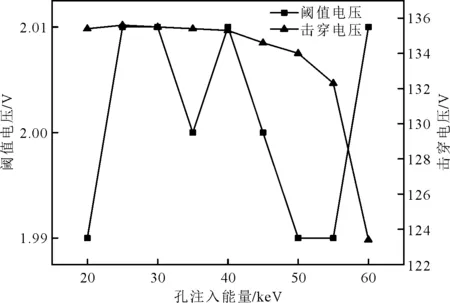

增加接触孔杂质注入能量,可以增加杂质B扩散范围,从而降低P型体区方块电阻电阻率,增加器件雪崩耐量。此次注入能量选取范围为由20 keV到60 keV,图9为孔注入能量拉偏对器件阈值电压和击穿电压影响仿真结果。

图9 孔注入能量拉偏对VTH和VB影响仿真结果

从图9可以看出,随着孔注入能量的增加,因为孔注入P型杂质纵向扩散且未横向扩散至沟道,所以导致阈值电压VTH稳定在2.00 V左右,虽然有所波动,但是,变化不明显;对于器件的击穿电压VB,随着孔注入能量由20 keV增加至40 keV,因为PN结电场强度小于器件临界击穿电场,所以,击穿点仍位于沟槽底部,器件击穿电压VB基本稳定在135.4 V左右,变化不明显;随着接触孔注入能量由45 keV增加至60 keV,器件存在反向耐压现象,PN结峰值电场首先到达临界击穿场强,击穿点逐渐由沟槽底部转移至PN结的结面,器件耐压逐渐由134.6 V降低至123.4 V。为了留够余量,固定接触孔注入能量为35 keV。

4 实验结果及分析

通过3.1节到3.4节仿真拉偏,基本确定了接触孔结构及接触孔注入工艺基准条件。按照图1搭建实验电路,其中,设置负载电感L为0.4 mH,电压源VDD为25 V,栅极脉冲方波电压高电平设置为10 V,低电平为0 V。不断增加方波脉冲宽度,直至器件发生击穿。

4.1 仿真结果

选取各结构工艺优化前和优化后的条件,即优化前WCT为0.15 μm、DCT为0.25 μm、孔注入剂量为1.0×1012cm-2和注入能量为20 keV,优化后WCT为0.25 μm、DCT为0.30 μm、孔注入剂量为4.0×1013cm-2和孔注入能量为35 keV,进行UIS仿真。

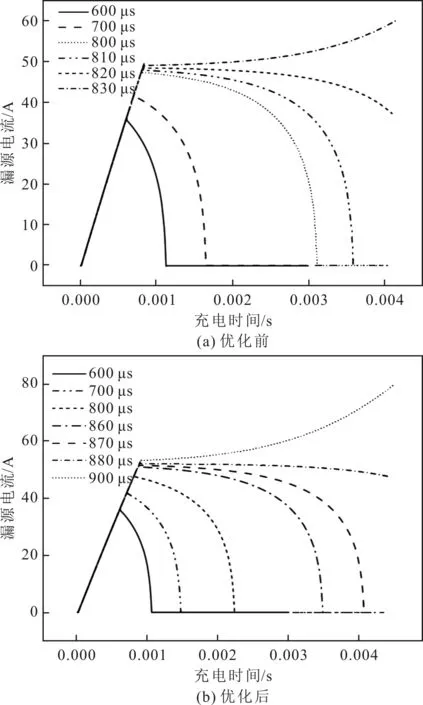

图10为优化前后不同充电时间器件漏源电流曲线。

图10 优化前后不同充电时间器件漏源电流曲线

从图10可以看出,随着充电时间增加,优化前后器件漏源电流皆呈增加趋势。这是因为,充电时间增加使得电感储能不断增大,当电感大小固定,器件关断时,电感能量以电流形式不断泄放,使得充电时间增加,电流不断增加。另外,与优化前相比,优化后器件的充电时间明显长于优化前,这是因为增加接触孔宽度、深度、注入剂量和能量,降低了器件P型体区电阻,从而增加了IPEAK。优化前,随着充电时间由600 μs增加至820 μs时,IPEAK由36.4 A不断增加至49.1 A,当充电时间为830 μs时,观察图10曲线可以看出,器件明显击穿,此时,漏源电流持续增加;优化后,随着充电时间由600 μs增加至870 μs,IPEAK由36.4 A不断增加至52.5 A,当充电时间为900 μs时,观察图10曲线可以看出,器件明显被击穿。

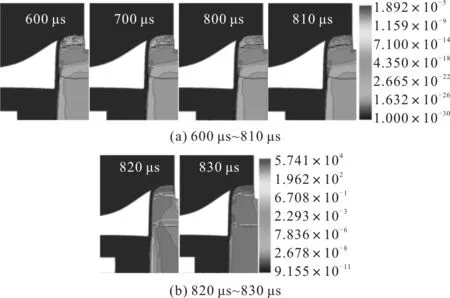

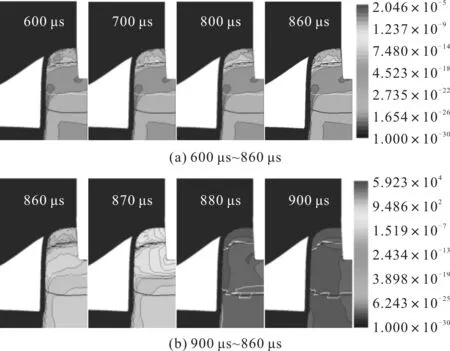

图11和图12分别为优化前和优化后不同充电时间下器件电流密度分布图。

图11 优化前不同充电时间的电流密度分布

图12 优化后不同充电时间下电流密度分布

从图11可以看出,对于优化前器件,当充电时间在600 μs~810 μs区间时,此时寄生三极管未开启,雪崩电流全部从P型体区流过;当充电时间增至820 μs及以后,观察器件电流密度分布可知,此时,寄生三极管开启,雪崩电流大部分从N+源区流过,小部分从P型体区流过。

从图12可以看出,对于优化后的器件,当充电时间为600 μs~870 μs时,此时寄生三极管未开启,雪崩电流全部从P型体区流过;当充电时间增至880 μs及以后,观察器件电流密度分布可知,此时寄生三极管开启,雪崩电流大部分从N+源区流过,小部分从P型体区流过。

为了接近实际UIS测试值,结合图10,将充电时间为810 μs时的漏源电流作为优化前的UIS极限电流,将充电时间为870 μs时的漏源电流作为优化后的UIS极限电流,此时,寄生三极管有开启趋势,IPEAK为52.5 A。

通过上述对比可以看出,通过优化接触孔结构及工艺,可以将UIS条件下雪崩电流由48.5 A提升至52.5 A,根据式(1)计算可得雪崩耐量可由470.45 mJ提升至551.25 mJ,提升约17.2%。

4.2 测试结果

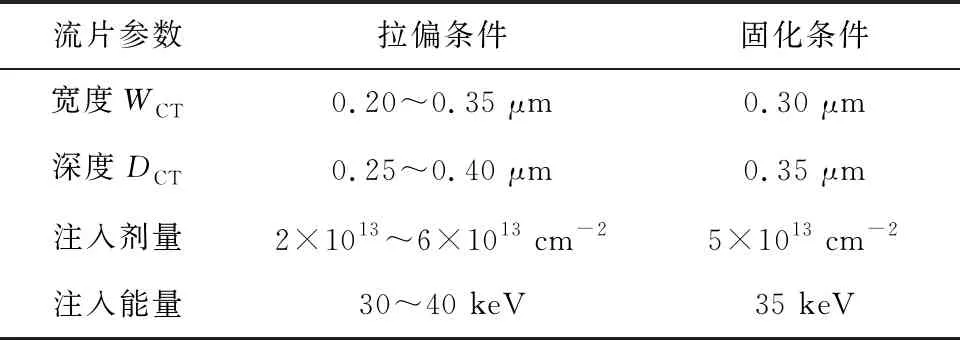

根据3.1部分到3.4部分得到的仿真结果,即确定WCT为0.25 μm、DCT为0.30 μm、接触孔注入剂量为4.0×1013cm-2和接触孔注入能量为35 keV作为基准条件,进行流片验证实际工艺窗口。最终确定的120 V SGT接触孔条件参数如表1所示。

表1 120 V SGT接触孔条件参数

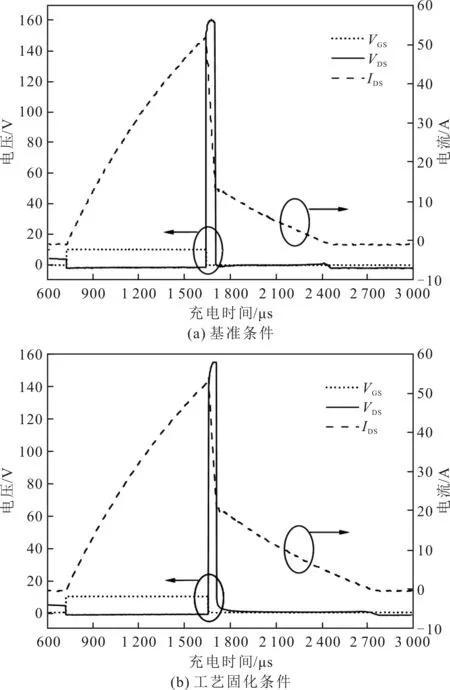

图13为包含最终流片后基准条件和工艺固化条件样品的UIS测试波形图。经过测试,流片基准条件测得IPEAK为50.9 A,固化条件测得IPEAK为54.2 A,因为最终固化条件工艺窗口略大,故UIS测试结果较大。根据式(1)计算可得,雪崩耐量由518.2 mJ提升至583.2 mJ,提升约12.6%。

图13 流片后样品UIS测试波形图

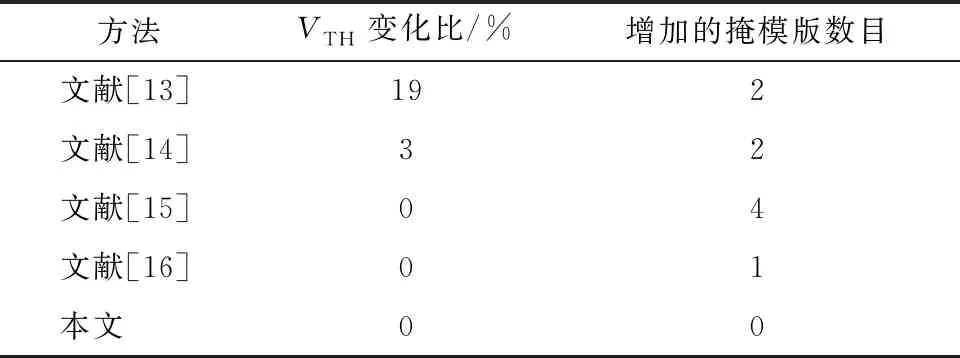

表2为所设计的SGT MOSFET与相关方法的性能对比。相较于基准条件,文献[13]和文献[14]都增加了两张掩模版,且文献[13]和文献[14]分别使得器件VTH增加了19%和3%;文献[15]增加了4张掩模版;文献[16]增加了一张掩模版。综合考虑优化前后器件VTH性能损失和设计成本等因素,所设计优化方法的综合性能更好。

表2 不同方法性能对比

5 结语

通过仿真设计和实际流片两个方面,验证了对于SGT MOSFET,通过增加元胞区接触孔宽度、深度、注入剂量及注入能量等方式,可以有效地提高SGT MOSFET器件的雪崩耐量。测试结果表明器件雪崩耐量提升明显,且器件的阈值电压和击穿电压均未受到影响。后续应持续研究接触孔单个结构和工艺变动对雪崩耐量影响程度,从而更加有效地降低设计成本。