基于FPGA的自适应动态规划控制算法研究

孔祥晔,王如刚,周 锋,郭乃宏

(1.盐城工学院信息工程学院,江苏盐城 224051;2.盐城雄鹰精密机械有限公司,江苏盐城 224006)

0 引言

步进电机是一种将电脉冲信号转换为角位移或者线位移信号的电动机。因其具有成本低、控制性能好、开环精度高、不易受外界环境影响等优点,广泛应用于工业电机控制装置中。加减速算法是运动控制中的关键技术,加减速算法是实现高速、高效的基础,实现加速度稳定,保证精度、高效,避免失步是目前工业生产加工需解决的问题[1]。目前常见的加减速算法有:梯形加减速、指数加减速、S形加减速。

传统的步进电机控制电路常用STM32和单片机芯片,但是单片机、STM32存在灵活性差、易受损、工作效率不高等缺点。FPGA具有丰富的逻辑单元、乘法器等硬件资源,无限编程重新配置可以减少硬件资源的使用,且灵活方便,并行程度高,可靠性高,在设计过程中可以根据实际情况进行灵活修改,目前常被应用于研究与生产中[2]。目前,众多研究人员利用FPGA研究加减速控制并取得了较好的成果。2017年,刘鹏等利用滑动滤波器改善了加减速中加速度突变的问题,在FPGA上实现了梯形加减速控制,但是加减速时间较长[3]。2020年,陈祖霖等利用FPGA优化了加减速节点的突变,一定程度上避免步进电机运动过冲,但也存在一定的失步现象,可以通过减小发送脉冲周期进行改善[4]。2021年,胡呈祖等提出了通过查表的方法实现FPGA加减速运动控制,能够实现较准确的运动目标控制,降低了成本,但是计算繁琐、降低了灵活度[5]。2021年,邱靖超等提出了基于FPGA的查表法多轴加减速运动,这种算法可以实现多轴同时控制运动、提高工作效率,减少加工时间,但是一定程度上增加了计算量,降低了工作效率[6]。

在现有研究的基础上,结合FPGA并行处理的优势,本文在基于FPGA的S形加减速的基础上,利用跟踪微分器的思路提出了一种自适应动态规划控制模型,并通过FPGA进行实验验证和功能仿真。基于动态规划搜索算法及最大速度限制算法可以避免连续修改目标频率,减少突变,保持速度变化连续平稳,减少加工时间、提高工作效率。

1 S形加减速算法

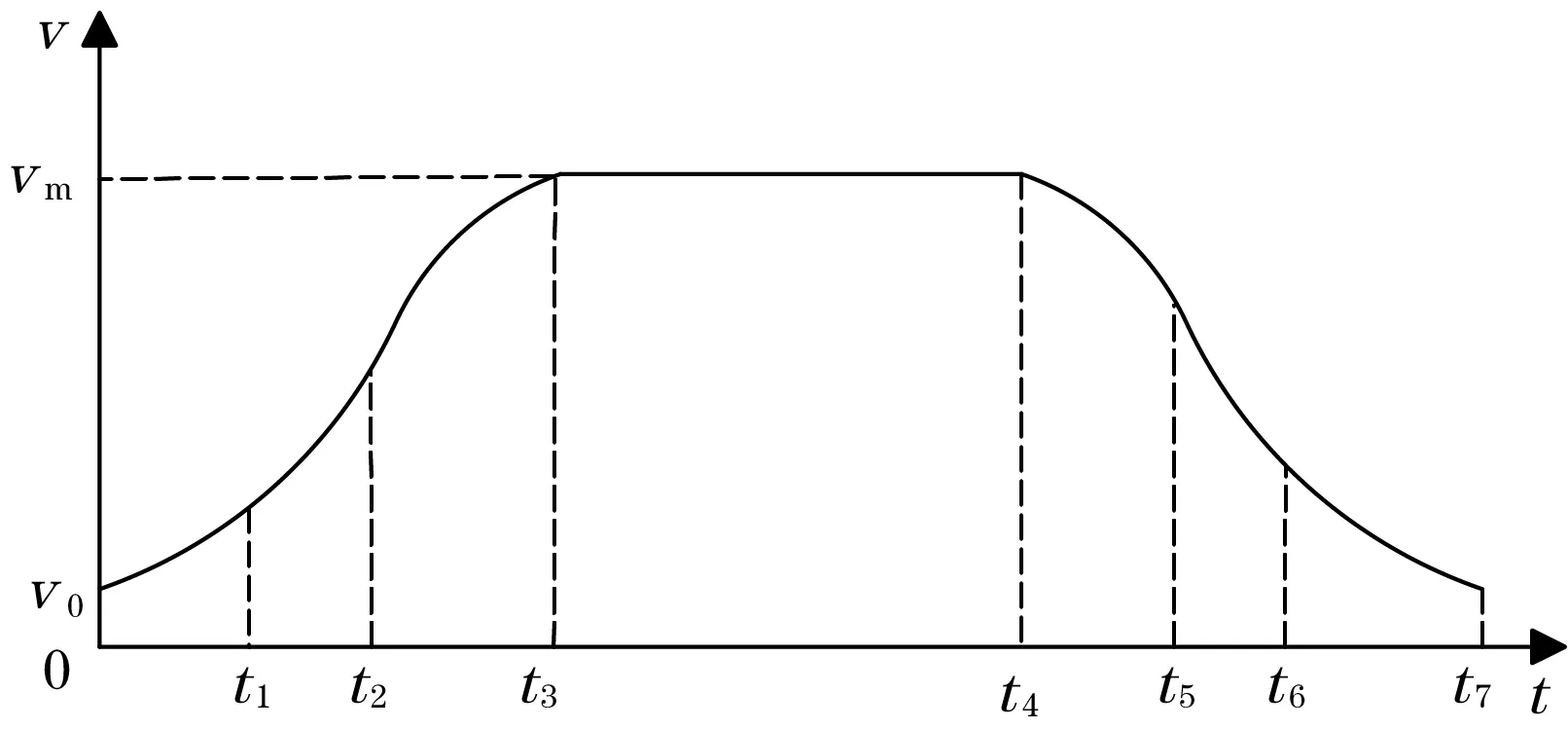

传统的梯形加减速和指数型加减速具有算法简单、响应快、实现方便的特点,但是随着工业自动化、复杂化的发展,加减速控制需要精度高,控制灵活、加速度连续变化等特点,梯形和指数形加减速已经不适应当今大多数加减速的控制需求。如图1所示,S形加减速具有变化连续、冲击振动小,柔性程度高的优点,符合现代发展的需求,常见的S形控制算法有:查表法[7]、卷积法[8]、积分法[9]。

图1 S形算法速度变化曲线

1.1 查表法

查表法的原理是通过曲线公式预先计算减速与减速过程中的各个点,再将这些点转换为定时器的比较匹配值,在MATLAB中写入S形曲线比较匹配值,将曲线中的16 bit数据输入到FPGA里的ROM核中,产生一个.mif文件放在rom文件夹下,通过查表,进一步结合脉冲控制步进电机的加减速,S形查表法图像数据的.mif文件如图2所示。

图2 图像数据ROM表

查表法加减速控制运行速度快,占用少量的CPU资源,但是该方法占用较大的存储空间,更改速度、加速度不方便,操作繁琐。

1.2 卷积法

X1[k]为输入速度序列,如图3所示,表达式为式(1)。

图3 X1[k]序列

(1)

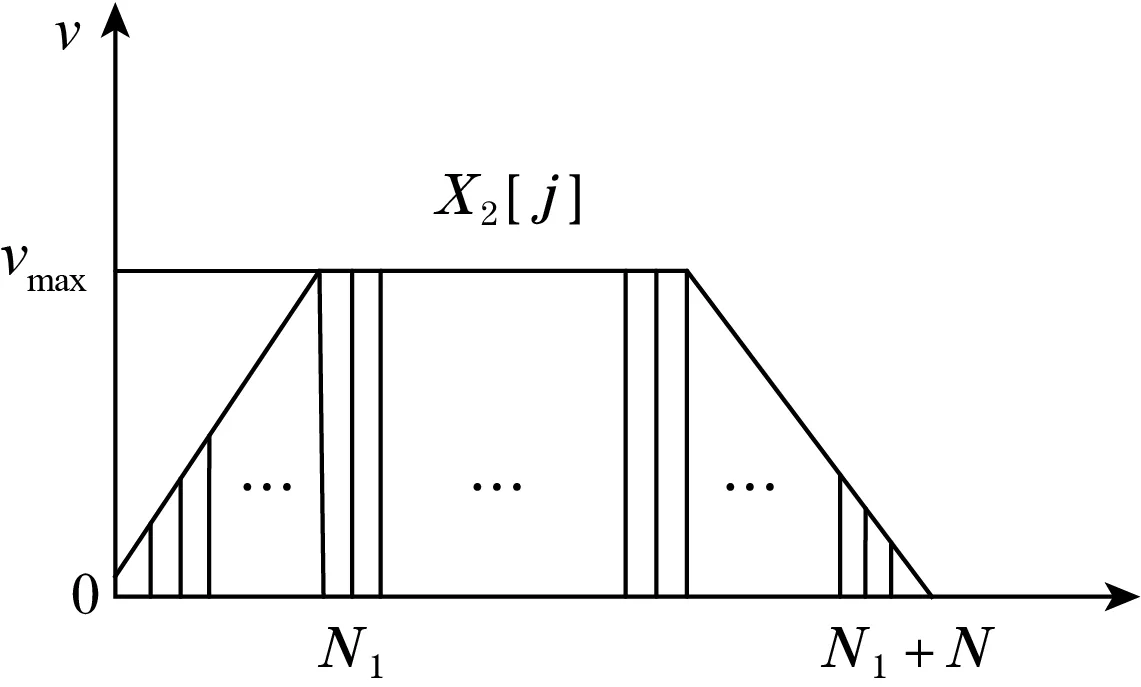

Y1[i]为卷积算子序列,如图4所示。

图4 Y1[i]序列

图5 梯形加减速速度序列

(2)

第2次卷积的卷积序列长度为N2,N2 图6 Y2[n]序列 图7 S形曲线加减速速度序列 (3) 通过结合FPGA实现卷积法加减速控制算法,能够有效提高运算效率,优化系统结构。由于FPGA上实现余数的浮点数计算困难,所以在计算不是整数的余数时,会占用较大的CPU资源。 通过插入4段连续分段函数,累加前一个数据,连续积分,得到4段曲线。得到位移、速度、加速度、加加速度之间的数量关系,再依次对加加速度、加速度以及速度分别进行积分,得到加速度、速度、位移的曲线[11]。图8为连续积分曲线。 图8 连续积分加加速度、加速度、速度、位移曲线 此算法相对于查表法和卷积法加减速控制算法,能够减少加工时间,减少电机失步,提高工作效率。但是也存在一定的缺点,当要给系统一个速度改变时,会容易产生步进电机的颤振,突变。 跟踪微分器(TD)是自抗扰控制技术中的重要组成部分,对于一个有噪声的输入信号x(t),使用常见的微分器进行微分会使其噪声增大,使用跟踪微分器,将原来的输入信号x(t)作为输出的跟踪信号x2(t),从不连续的带有噪声信号的中提取连续、微分信号,可获得平滑的微分信号[12]。本文使用跟踪微分器,是将步进电机不平滑的转动中提取连续平滑的信号,在进行信号突变时,跟踪信号能够进行补偿,使得运动控制的连续平稳。本文采用的跟踪微分器为二阶跟踪微分器[13],离散化形式可以表示为: (4) fhan为快速跟踪控制综合函数,表达式为: (5) fsg函数表达式为 fsg(x,d)=(sign(x+d)-sign(x-d))/2 (6) 快速控制跟踪微分器的作用是起到一个缓冲的作用,当给定一个阶跃信号时,快速跟踪控制微分器会抑制其速度或者频率防止过冲,否则会导致步进电机在加减速过程中过冲导致失步[11]。 在FPGA开发板中,只添加上述跟踪微分算法还不能够使速度突变得到很好的抑制,所以还需要在此基础上添加最大速度限制模块,来判断下一时刻的速度是否超过设置的最大速度,该速度必须大于实际情况下电机使用场景下所需的最大速度[14]。该改进既能够满足加速也能满足减速情况下的限制。设本实验的最大限制速度为v。当v0+ha>v时,v0为当前速度,h为积分步长,a为控制量(加速度),判定此时超速,这时就要判断下一个周期内速度,并赋予本周期的速度在下一周期速度的限制,计算出a 因为步进电机有正转和反转2个方向,所以x的值有正有负,所以将正负2种情况合并,得到: a=[vsign(x)-x]/h (7) 将式(7)加至式(5)中,可以得到最大速度限制公式: (8) 上述最大速度限制算法可以判定速度是否到达最大值并对其进行减速操作,但是在加速至匀速阶段,不能断定是否运动到应到位置,动态规划算法是将大问题转换为小问题,是求运动过程中最优数学解[15]。加减速运动中,每个周期步进电机重复进行频率判断,直至达到最大速度,所以本实验添加此算法,避免进行重复搜索,解决小问题,算出最优解,再逐步进行求解,最后提供解决方案[16]。此算法具体如下。 2.3.1 阶段 阶段变量是离散的,设转动位移是Sm,解数列为g(sm),将加速阶段若干个相互联系的周期分成若干个小问题。因为是实现S形加减速,所以设备选速度块为di。 di={1,3,5,7,9} (9) 2.3.2 构造 构造初始状态,从di中可以得到: (10) 2.3.3 约束 设qi为g(sm)序列中第i个值,判定条件为:qi-qi-1 2.3.4 转移 从上面可以递推得到下面转移方程的一般形式: (11) 根据上面递推公式,可以通过判定条件得到目标位移的最优解,也就是步进电机运动速度轨迹图像。 2.3.5 优化 由于本文实验电机是一个由加速匀速再减速的过程,如果使用上述算法,会占用大量内存,计算量也大,因为本实验的加速与减速过程本质上是完全相同的2个阶段,只是两阶段加速度成相反数。所以,为了减小计算量和少量的内存,对上述算法进行优化,降低搜索量,只搜索加速到匀速阶段,另一部分由最优解序列的逆排序得到。假设S为整个过程的总位移,S1为加速阶段的位移,S2为速度到达最快即匀速运动时,每个单位周期内的位移。 (12) 当步进电机的基本参数确定时,为了提高效率,可以先预先搜索出解数列,与最高速度的目标数列进行匹配,可以快速计算出位移的速度块数列。 本实验流程图如图9所示。 图9 实验流程图 本次实验采用的实验平台是由SF-CY4开发板,A3977型号驱动器,型号为42BYGH34-04A的12 V步进电机组成。硬件设计框图如图10所示。 图10 实验硬件设计框图 2.4.1 硬件设计 FPGA开发板选用Cyclone系列的SF-CY4开发板,利用串口通信将PC端UART协议转USB协议与FPGA 的通信,FPGA通过H桥集成电机驱动器驱动电机转动,三者之间通过数字IO接口对电机角速度控制。FPGA与驱动器A3977的数字IO接口连线如图11所示。其中,DIR为方向信号,控制步进电机的转动方向,当方向信号为高电平时,正转,反之反转;EN为步进电机的使能信号,信号为低电平时,使能信号拉高,电机正常转动;STEP是产生步进电机位移的脉冲信号,当步进电机检测到一个上升沿时,STEP信号拉高;HOME是反馈信号,不同的STEP,对应不同的HOME信号。A、B代表步进电机驱动线的2项。 图11 FPGA与驱动器数字信号接口 2.4.2 软件设计 FPGA采用自顶而下的模块化设计理念,图12是本次实验主要的模块的RTL视图,包括PLL锁相环模块,跟踪微分模块、规划搜索模块、最大速度限制模块及除法器模块,共同驱动步进电机运动模块进行驱动。 PLL锁相环模块整合本实验所需时钟信号,分配给各模块分频时钟及复位信号,跟踪微分模块将原始输入使能信号输出为输入的跟踪信号和微分信号,将电机设定角度看成原始信号,实际转动角度看做跟踪信号,在给定反向转动的指令后,通过跟踪微分能够抑制速度的突变,产生过冲现象。在滤波的同时,为判断步进电机转动的脉冲数是否转动相对应的角度,通过搜索规划模块搜索求出本周期内的最优解,独立设定控制周期与实际脉冲周期,将跟踪微分模块和搜索规划模块输出值输入最大速度限制模块,保证电机在可运动的最大速度限制值内进行最优的速度控制。为方便计数,最后添加除法器,将频率转换成周期输入步进电机,达到步进电机运动控制。 利用MATLAB与FPGA之间方便的数据交互能力和MATLAB的数据分析和可视化功能,为验证本实验的可行性,图13是在MATLAB中计算得到的速度和位移的仿真图像。 (a) 本文搭建了由SF-CY4型号的FPGA开发板、A3977驱动器、步进电机组成的实验平台,开发环境为QuartusⅡ 13.1,开发语言为Verilog,仿真软件为Modelsim。仿真输出的波形如图14所示。为了便于观察本次实验的结果并进行分析,模拟波形中real信号是添加DIR转向信号的波形,由于速度只能为正,在实际仿真中,没有负值,实际输出给电机的是不带real信号的,但2个仿真图最终效果一致。实际仿真如图15所示。 图14 效果仿真图 图15 实际仿真图 图16为实验结果反馈结构框图,由控制单元向反馈单元进行反馈。梅花联轴器连接控制单元和反馈单元,编码器每1 ms进行转速收集,收集到的数据脉冲信号通过驱动板驱动用UART串口发送到PC端。 图16 反馈结构框图 实验设定步进电机启动频率为500 Hz,目标频率为5 100 Hz,在加减速控制运动过程中,分频计数逻辑每1 ms产生1个高脉冲,用来切换当前速度,用增量式旋转编码器对步进电机的转角进行测试。在每个运动状态运行时间相同的情况下,将改进后的控制系统的结果和动态控制算法中的最优解进行对比,一共对比708次,定义上下浮动超过3 Hz为突变点,表1为各运动状态的突变点的个数及精准度,结果显示整个运动过程的精准度为99.91%。 表1 改进后的突变点数 如图17所示,实线是没有改进的实验结果,虚线是改进后的实验结果。在给定参数均相同的情况下,改进的加减速运动在A点到达目标频率,加速时间为113 ms,比改进前的B点提前11 ms到达最大频率且加速过程平滑。在同一时间,给定电机一个反向转动的指令,没有添加跟踪微分器的加减速控制匀速运动达到反向转动目标频率,并在到达最大速度C点处产生过冲现象,从对比图中可以看出,添加跟踪微分模块的运动控制在正转减速到0且反转从0加速的过程中,采用了S形算法控制,并在反转达到最大速度前避免过冲现象的产生。同时,从实验结果来看,反向转动的过程中,改进算法运行时间比改进之前快了14 ms。本实验中动态规划算法可以减少D点突变现象的产生。 图17 结果对比图 表2为本次实验改进前后加减速对比表,加速时间是从起始频率加速至最大速度的时间,反转时间指的是从正转最大速度至反转最大速度使用的时间,改进后的S曲线控制系统较之前的精准度上升了8.14%,效果更好。 表2 改进前后加减速对比表 针对步进电机在运动过程中突然改变目标速度或者反向转动的情况下产生突变、过冲,柔性程度差、运行时间较长的缺点,设计了一种基于自抗扰控制理论中的跟踪微分器的原理,结合动态规划算法和最大速度抑制算法的加减速运动控制系统。相比于改进前的连续积分的算法,该算法可以减缓加减速及反转产生的突变及过冲现象,加工时间提高11ms,改进后的S曲线控制系统较之前的精准度上升了8.14%,效果更好。实验结果表明,该算法加减速平稳、加速时间适中,符合大多数中小型企业的生产需求,运用闭环控制,有利于今后从单轴运用至多轴的控制研究。

1.3 积分法

2 原理及系统设计

2.1 跟踪微分器

2.2 最大速度限制算法

2.3 动态规划搜索算法及改进

2.4 系统设计

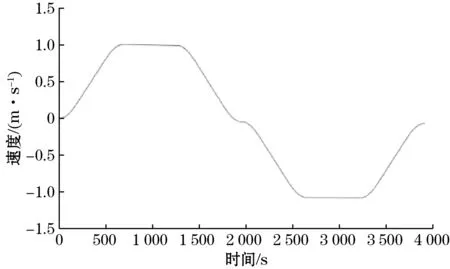

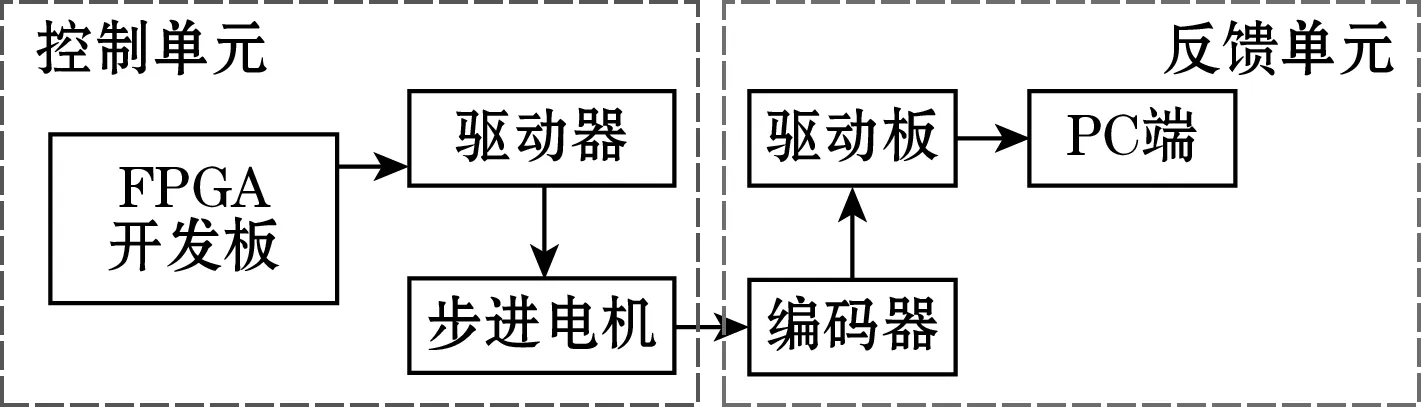

3 结果与分析

3.1 MATLAB验证

3.2 实验结果反馈

4 结论