一种12位5.5MS/s同步FLASH-SAR ADC的设计

朱朝峰,汪 东,,邓 欢,龙 睿,唐金波

(1.湘潭大学物理与光电工程学院,湖南湘潭 411100;2.湖南毂梁微电子有限公司,湖南长沙 410000)

模数转换器(Analog-to-Digital Converter,ADC)作为数字和模拟信号连接的桥梁,对于提高芯片的数字运算能力有着至关重要的作用。其中逐次逼近型(Successive Approximation Register,SAR)模数转换器凭借着结构简单、面积小、功耗低等优点被广泛运用。但是传统同步SAR ADC 受限于串行的工作方式,N位的SAR ADC至少需要N个转换周期,从而限制了SAR ADC转换速度。以SAR ADC为核心的混合结构,如流水线SAR ADC[1]、VCO-SAR ADC[2]、时间交织SAR ADC[3]等,虽然可以解决传统SAR ADC 的此类问题,但仍然存在着精度和速度不能折衷的问题。

在此基础上设计了一款同步FLASH-SAR ADC,利用FLASH ADC 并行的工作特点,解决SAR ADC 只能串行的工作问题,同时设计了一种新的DAC 电容阵列以及跨电压域比较器,并针对DAC 结构进行编码设计,进一步提高ADC 的转换速度。最后采用55 nm CMOS 工艺经版图设计,寄生参数提取,在5.5 MS/s(Million Samples per Second,MS/s)采样速率下,后仿真有效位达到11.82 bit。

1 整体架构设计

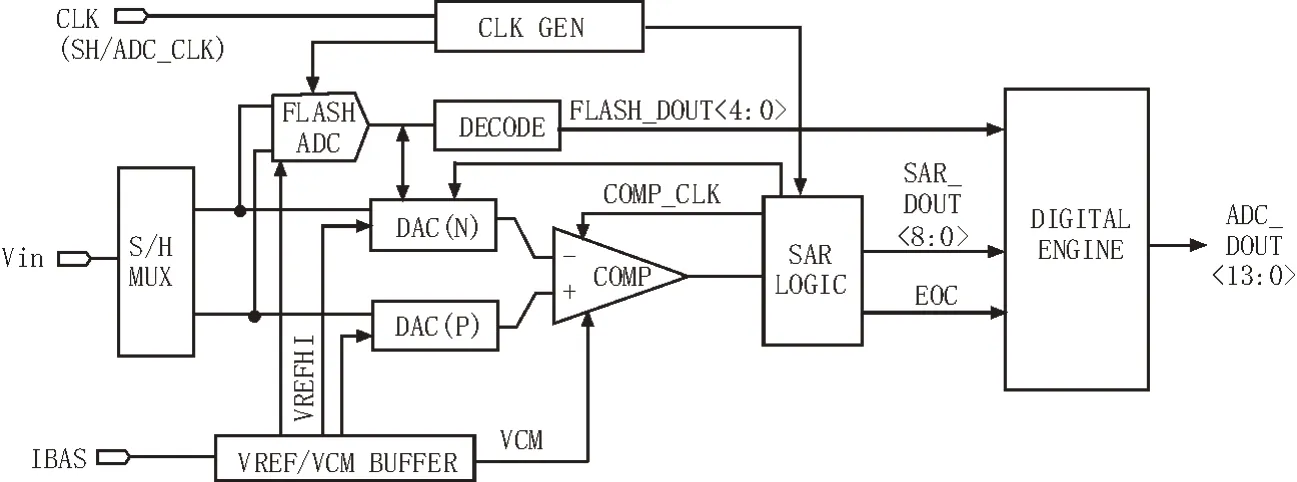

FLASH-SAR ADC 结构框图如图1 所示,核心模块为FLASH ADC 和SAR ADC 两部分。FASLH ADC由电阻串分压电路和31 个比较器电路组成。SAR ADC 由采样保持模块(S/H MUX)、DAC 电容阵列模块、比较器模块(COMP)和控制逻辑模块(SAR LOGIC)组成。外围模块由参考产生电路(VREF/VCM BUF FER)、时钟产生电路(CLK GEN)和数字处理模块(DIGITAL ENGINE)组成。

图1 FLSAH-SAR ADC结构框图

该ADC 采用同步时序控制逻辑、基准时钟(ADC_CLK)和采样时钟(SH)通过外部输入,其余时钟均由内部时钟产生模块(CLK GEN)产生。IBAS 由带隙基准产生,并通过VCM BUFFER 和VREF BUFFER产生ADC 所需要的参考电压和共模电压(VCM)。

FLASH-SAR ADC 中的高5 位由FLASH ADC 以温度码的形式进行粗量化,低7 位由SAR ADC 以二进制码的形式进行细量化[4],其工作过程分为3 个阶段:

1)采样阶段:FLASH ADC 和SAR ADC 同时对输入信号Vin 进行采样;

2)FLASH ADC 量化阶段:采样结束后,SAR ADC 进入保持阶段,FLASH ADC 进入工作阶段,粗量化高5 位,在一个时钟周期内完成,通过计算可以得到量化电压VFlash;

3)SAR ADC 量化阶段:FLASH ADC 以温度码的形式将结果传输给SAR ADC,得到残差电压Vresidue=Vin-VFlash,然后对残差电压Vresidue进行细量化,得到低7位数字码。

2 关键模块电路设计

2.1 DAC电容阵列设计

DAC 对SAR ADC 的精度、转换速度以及功耗等指标起决定性作用[5]。图2为该设计的DAC电容阵列,采用电荷重分配结构,利用电容的电荷守恒和再分配特点实现SAR ADC 的转换功能,并且采用分段式设计,减小电路开销,降低功耗[6]。DAC 的高5位为单端结构,低7 位为差分结构,这种结构能够抑制共模噪声的影响,使输出电压在共模点附近且摆幅较小。

图2 DAC电容阵列示意图

FLASH ADC 粗量化的结果传给DAC,在DAC的N 端得到残差电压Vresidue,其P 端高5 位电容下极板保持接地。为了降低DAC 的功耗,采用基于共模电平(VCM_based)的切换方式[7],在电容下极板引入共模电压。共模电压的引入增加了低位切换开关以及控制时序的设计难度,因此采用高位电容采样的方式减少低位电容下极板所需电位。但参与采样和具有校准功能的冗余位下极板仍然需要4 个电位,所以在切换过程中用GND 代替VCM 电位,从而减少所需开关个数,降低控制时序的设计难度。

为验证DAC 的线性度,对每个工作阶段电压推导如下:

假设单位电容为C,在采样阶段,DAC 两端对应的电荷分别为式(1)和式(2)。

FLASH ADC 将结果以温度码的形式传输给DAC,为方便推导,转换为5 位数字码,以F4、F3、F2、F1、F0表示。待DAC 输出结果稳定后,进行第一次比较,根据电荷守恒可推导出P 端输出电压VXP1和N 端输出电压VXN1分别为式(3)和式(4)。

其中,VREF为参考电压,式(3)和式(4)相减得:

根据比较结果,决定下一位开关切换。当比较结果为1 时,下一位N 端电容下极板接VREF,P 端电容下极板接GND;当比较结果为0 时,下一位N 端电容下极板接GND,P 端电容下极板接VREF。

后续每次开关切换,DAC 输出端电压差为:

其中,k=24-j,j=2,3…9。当j-1 位比较结果为0时,式(6)中±k/128 为减号;当j-1 位比较结果为1 时,式(6)中±k/128 为加号。第j位切换同上所述。

2.2 跨电压域的动态比较器设计

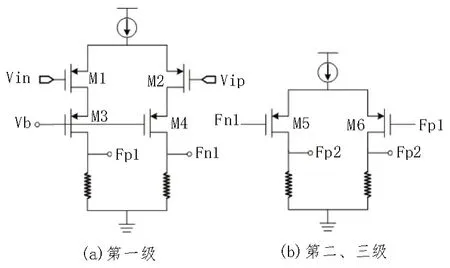

比较器作为ADC 的另一个核心电路,决定了ADC 的分辨率和转换速度等核心参数[8]。文中设计了一款高性能跨电压域的动态锁存比较器,该比较器采用三级预放大器和锁存级(LATCH)级联的结构,结构简图如图3 所示。

比较器第一级预放采用共源共栅结构,利用其隔离特性,避免比较器影响到DAC 输出端电压,同时提高第一级增益。NMOS 管相对于PMOS 管,在比较阶段更容易受到迟滞效应的影响,导致放大后的电压下降缓慢,加大了比较出错的概率,同时PMOS管和NMOS 管相比,拥有更低的闪烁噪声[9],因此采用PMOS 管作差分输入对管。第二、三级预放采用电阻做负载的传统运放结构,电路图如图4 所示。

图4 预放大级框图

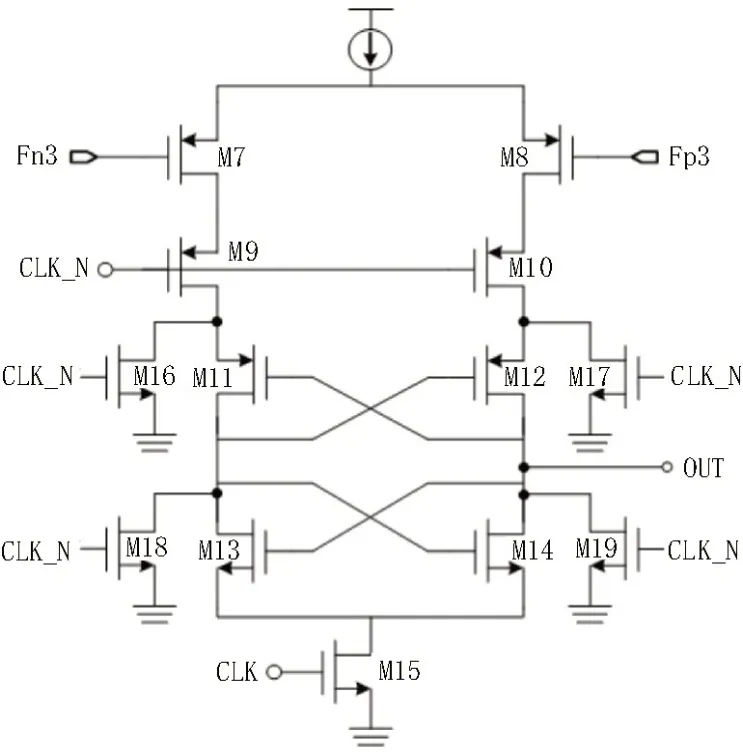

该设计FLASH-SAR ADC的参考电压为2.5 V,根据2.2 节,可求得DAC 输出电压范围为1.18~1.33 V,因此预放大级采用3.3 V 器件设计,用3.3 V 模拟电压供电,留有足够的裕度,确保MOS 管在不同情况下均能工作在饱和区。经过三级预放大后,LATCH级输入电压小于1.2 V,且预放大级和LATCH 级通过电容耦合连接,预放大级直流输出不会影响LATCH级,因此LATCH 设计时选用1.2 V 的器件,用1.2 V数字电源供电,在1.2 V 电压域完成比较过程,同时SAR 控制逻辑也采用1.2 V 数字电源,所以比较器可以和SAR 控制逻辑衔接,不需要额外降压处理。LATCH 级电路如图5 所示。

图5 LATCH级电路图

该设计采用输出失调存储(Output Offset Storage,OOS)技术[10],在预放输出端增加电容,消除比较器失调电压。为将校准效果最大化,分别对三级预放进行失调校准,如图3所示。开关的控制时序如图6所示。

2.3 数字逻辑及编码

数字逻辑电路是整个ADC 的控制核心,负责寄存比较器结果,控制DAC 开关切换,以及输出编码等工作[11]。核心模块SAR 控制逻辑电路由一排移位寄存器产生移位时钟控制数据寄存器来寄存比较结果,并把结果传输给DAC,控制DAC 的开关切换。同时增加一组寄存器,由移位寄存器产生的时钟控制,依次产生DAC 中低位部分VCM 的控制时序。

根据2.2 节所述,FLASH ADC 输出数字码为F4、F3、F2、F1、F0;SAR ADC 输出9 位码,记为S8-S0,其中包含一位冗余位。由于低位采用差分结构,根据SAR ADC 每次转换的数字码来判断后续数字码在FLASH ADC 输出的基础上需要加还是减,冗余位数字码和权重相同位对应相加[12]。最终所有数字码处理如图7 所示,其中,A1、A0 为符号位,00 表示正常转换,01 表示ADC 上溢,11 表示ADC 下溢。

3 仿真结果与性能比较

3.1 比较器仿真结果

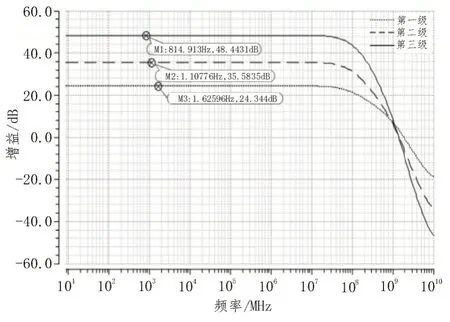

该12 位单端结构FLASH-SAR ADC 的LSB 为610 μV。为满足ADC 精度需求,比较器至少需要比较出0.5 LSB 大小的电压,即305 μV。一般情况下,LATCH 比较器的失调电压可以达到10 mV 以上,前置放大级需要将最小识别电压放大到比LATCH 的失调电压更大的程度,这样比较时才不会出错,因此假设比较器预放大级能够将0.5 LSB 电压放大到30 mV,此时预放大级需要的增益为:

比较器每次转换的时钟周期为13 ns,假设一半时间用于比较,即t0=6.5 ns。在估算情况下,可以把多级级联结构的预放大级视为特征常数为τ的一个单极点系统。如果设t0=2τ,此时预放大级能建立到总增益的(1-e-2)≈86%,足以满足LATCH 级的输入要求[13],总的预放大级带宽按式(8)进行估算:

利用Cadence 平台进行AC 交流小信号仿真,结果如图8 所示,由仿真结果可知,预放大级增益可以达到48.4 dB,-3 dB 带宽可以达到89.3 MHz,完全满足指标要求。

图8 比较器增益

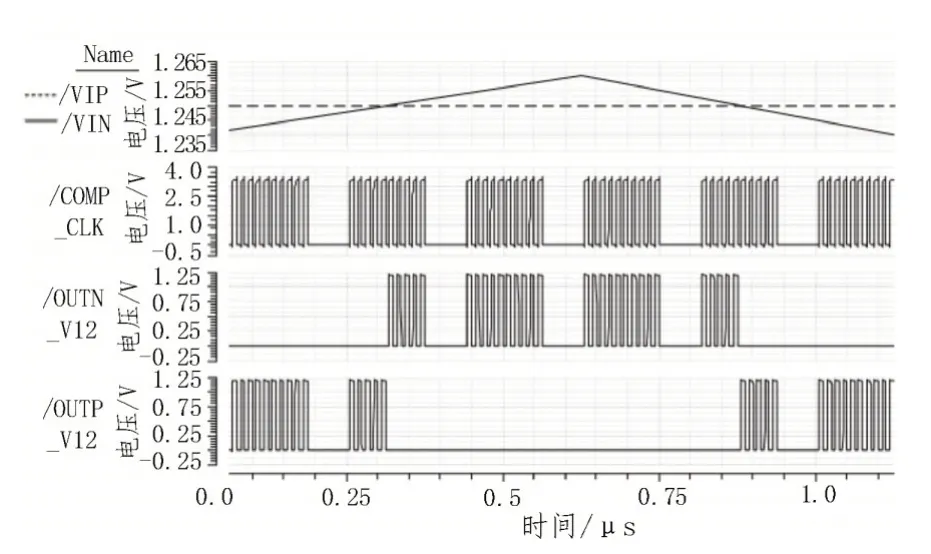

对比较器整体功能进行仿真,按照FLASHSAR ADC 设计要求,将比较器的时钟频率设置为82.5 MHz,结果如图9 所示,比较器可以根据输入端压差的变化,进行正确的翻转,说明比较器可以正常工作,且满足12 位单端ADC 的精度以及速度要求。

图9 比较器功能仿真结果

3.2 FLASH-SAR ADC仿真结果

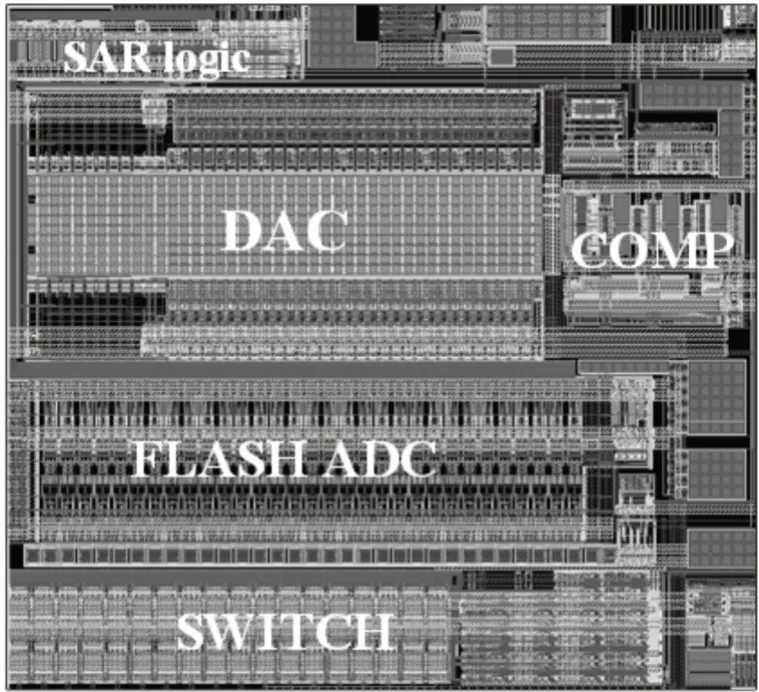

FLASH-SAR ADC 基于55 nm CMOS 工艺进行布局规划和模块设计,优化后的版图如图10 所示,版图有效面积为0.53 mm×0.5 mm。

图10 FLASH-SAR ADC版图

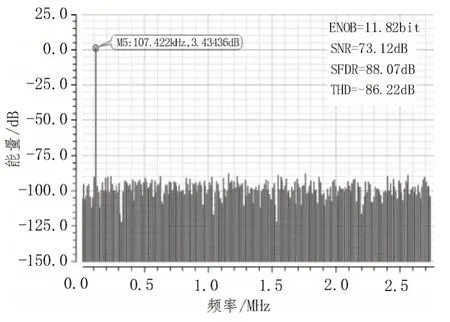

利用Cadence 平台对电路进行仿真,在模拟电源电压3.3 V、数字电源电压1.2 V、采样率5.5 MS/s、输入频率为0.118 MHz、TT 40 ℃工艺角(Process Corner)下进行后仿真,将ADC 的输出结果经过理想DAC 还原后,取512个点进行FFT分析,频谱图如图11所示。

图11 FFT分析结果

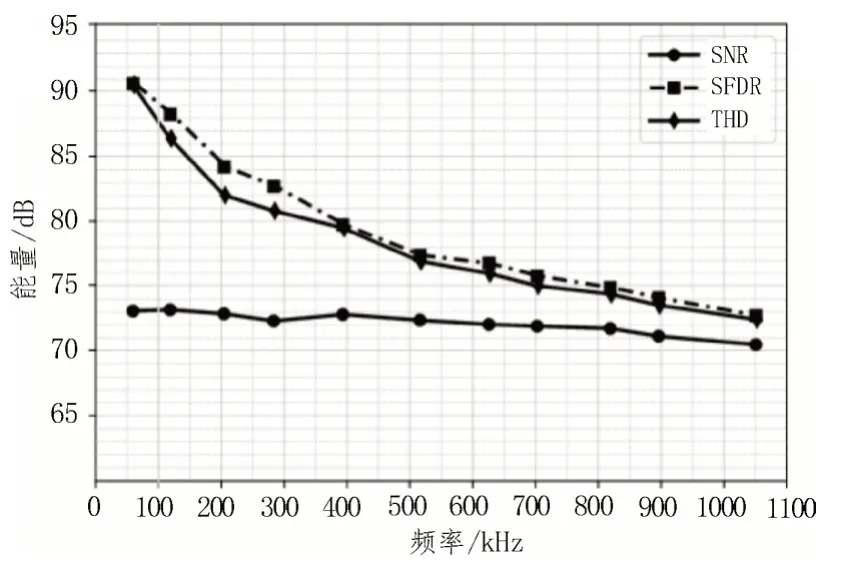

当采样率为5.5 MS/s时,改变输入信号频率,对仿真结果进行频谱分析,统计结果如图12所示。可以发现当输入信号频率改变时,ADC 的SNR 均能超过71 dB,SFDR 均能超过74 dB,说明ADC 性能良好。

图12 不同输入信号频率仿真结果

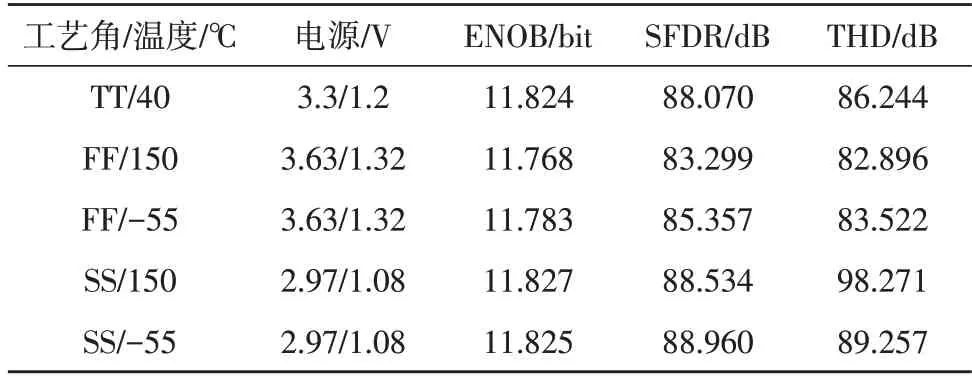

运用PVT(Process Voltage Temperature)测试方法[14],通过几种不同组合,在输入信号频率为0.118 MHz时,对电路进行后仿真,结果汇总如表1 所示。在FF工艺角,150 ℃下性能最差,但此时有效位也可以达到11.768 bit,满足设计要求。

表1 PVT仿真结果

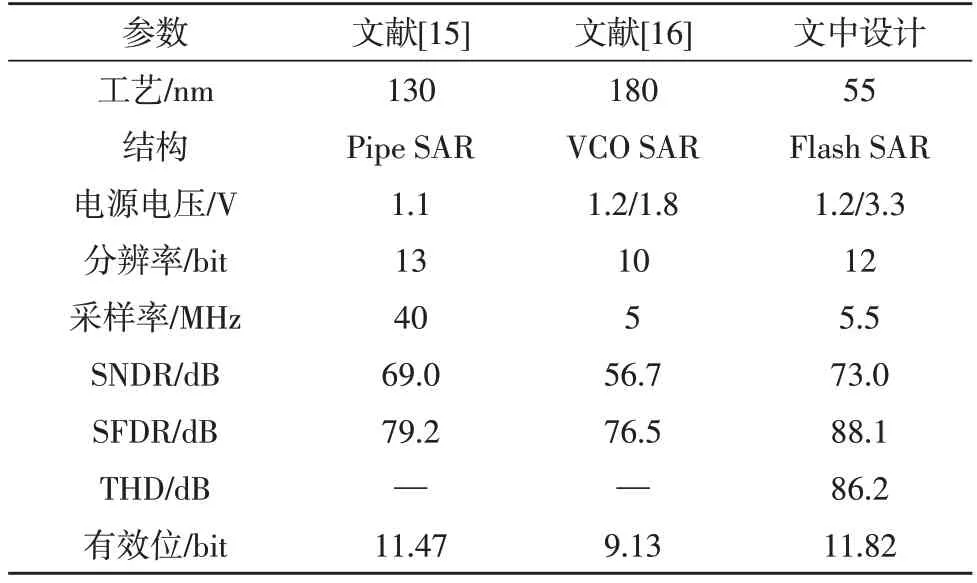

3.3 性能比较

FLASH-SAR ADC 和文献[15]、文献[16] 的主要参数进行对比,结果如表2 所示,该设计的有效位和其他动态参数均优于文献[15]和文献[16]。

表2 性能对比统计

4 结束语

文中基于55 nm CMOS 工艺设计了一款采样率为5.5 MS/s 的同步FLASH-SAR ADC,提出了一种差分结构和单端结构融合的电容阵列,并进行编码设计,在保证精度的基础上提高转换速度,最后完成了整个ADC 的电路设计以及版图设计,并在电压变化范围为3.3 V±10%、1.2 V±10%,温度覆盖范围为-55~150 ℃的情况下,进行后仿真验证,结果表明有效位可以达到11.82 bit,信噪失真比为73.12 dB,无散杂动态范围为80.07 dB,总谐波失真为86.22 dB,说明该FLASH-SAR ADC 具有良好的性能。