面向SoC 开发的一致性时钟信息管理方案

刘 斌,虞小鹏,谭年熊

(1.浙江大学微纳电子学院,浙江杭州 310000;2.西安路科验视集成电路技术咨询有限公司,陕西西安 710000)

在常规芯片开发流程中,时钟信息来源于系统工程师(System Engineer,SE),包含时钟树[1]和时钟频率。核心时钟信息一般会采用Excel 表格形式进行人工维护。接下来该表格信息交由设计工程师(Design Engineer,DE),他们根据时钟信息来实现设计,并进一步细化时钟表格内的信息。DE 在填充更多时钟信息后,将其交由验证工程师(Verification Engineer,VE)和后端工程师(Backend Engineer,BE)。最终,不同模块、子系统的时钟信息会合并在一起用来描述整个系统的时钟信息。在这一过程中,不同时钟信息来源、不同时钟信息的维护角色的合作可能会增加时钟信息出现错误的可能性,同时在系统级和子系统级之间的时钟信息不匹配也会带来物理实现时的时序集成风险[2]。

在具备了时钟信息一致性管理的方案以后,就可以实现中心化的时钟信息存储、集成和提取[3],该方案基于Python、Tkinter[4]和Graphviz[5]实现。时钟信息一致性管理方案由SE 和DE 共同维护,而VE、BE和DFT(Design For Test)工程角色均可以从时钟信息中提取并生成准确的时钟信息脚本,用于不同的工具流程。

1 时钟表格和一致性数据

要解决时钟数据的一致性,就需要提供一种新的定制化方案,不但需要中心化地存储时钟数据,也需要满足各种数据信息的提取需求,这一方案取名为ClockManager(CM)。采用CM 对时钟信息管理时,SE 一般会采用Excel 格式存储、编辑时钟信息,由CM 将其提取为各个设计部分的时钟信息,接下来DE 会基于CM 来修改时钟信息。同时CM 也会基于SE 初始提供的时钟信息与DE 做过编辑改动的时钟信息做比较,以确保在SE 和DE 编辑的时钟信息的一致性[6]。

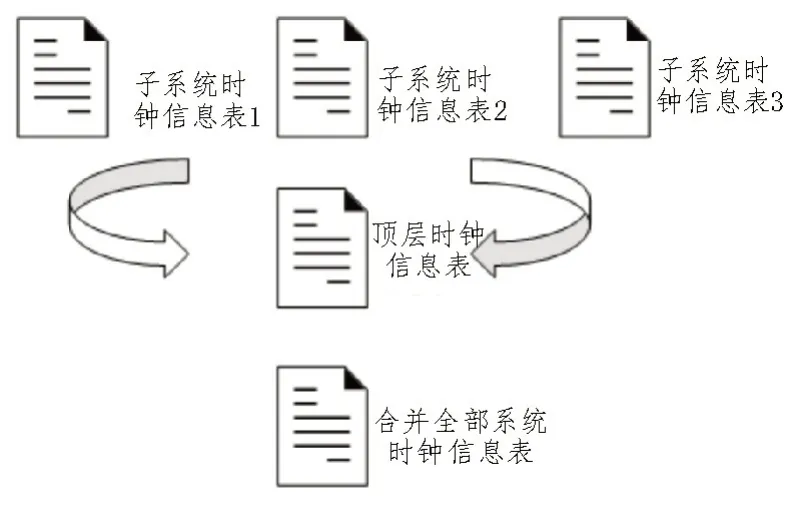

一旦各个模块和子系统的时钟信息一致性得到保证,则顶层系统DE 就会将各个设计部分的时钟信息组织在一起,继而合并构建为完整的系统级时钟信息数据,也可以由此生成一个完整的覆盖系统全部时钟信息的表格。在此之后,SE、DE、VE、BE 和DFT 都可以从CM 提取时钟数据,快速生成与时钟有关的脚本信息[7]。CM 合并系统时钟信息表如图1所示。

图1 CM合并系统时钟信息表

CM 工具用户可以基于表格信息提取时钟信息,并将时钟信息显示在图形用户界面(Graphic User Interface,GUI)。CM GUI 编辑窗口可以对时钟信息做出多种编辑、比较、核对和导出功能:

1)可以将不同时钟组按照不同颜色组显示。

2)可以在导入或导出时钟信息时做时钟信息一致性检查。

3)会对当前导入编辑的时钟信息库做总结,例如时钟数目、PLL 数目等。

4)会对时钟树结构的源时钟和子一级时钟做图形显示。

5)可以对时钟源和时钟序列做快捷跟踪,以便梳理特定时钟的时钟信息,获得其父一级时钟和子一级时钟,如图2 所示。

图2 CM GUI中的时钟树界面

6)可以快速查找到目标时钟。

7)可以查询详细的时钟编写日志。

8)可以将不同版本的时钟信息表进行对比。

9)VE、BE 和DFT 可以提取方便的时钟信息脚本用于不同的工具。

在SE 提供给CM 的时钟信息Excel 表格中往往只包含非常有限的信息,例如时钟源数目、频率要求和时钟关系。在CM 导入这些信息交由DE 编辑后,时钟信息会逐渐丰富起来,它们包含以下信息:

1)时钟名称:在全局的时钟信息中具有时钟名称的唯一性。

2)时钟类型:用来表明时钟是否为PLL 源时钟、分频时钟、门控时钟或者管脚接入时钟等。

3)频率:即时钟对应的频率,在某些情况下,不同电压设定也会设定不同的时钟频率。

4)时钟源:用来指明产生当前时钟的时钟源。

5)分频数:用来表明当前时钟与时钟源的分频关系。

6)波形:用来指导后端设定时钟的占空比。

7)所属布局:用来指明当前时钟所属的物理实现布局块。

8)同步关系:用来定义某些时钟组,在同一时钟组的时钟会视为同步关系。

9)扫描时钟映射:芯片系统需要若干测试扫描时钟。

10)实例名:由时钟所处的结构层次和时钟名称共同构成,用来指向系统中的时钟路径。

1.1 时钟信息表合并

SE 先编辑基础的时钟信息,而后会由DE 扩展编辑这些时钟信息。子系统DE 和系统DE 会在最后将其编辑的时钟信息表交由CM,由它完成时钟信息的合并。例如可以将顶层时钟信息表与子一级时钟信息表完成合并,生成了合并后的系统时钟信息表[8]。

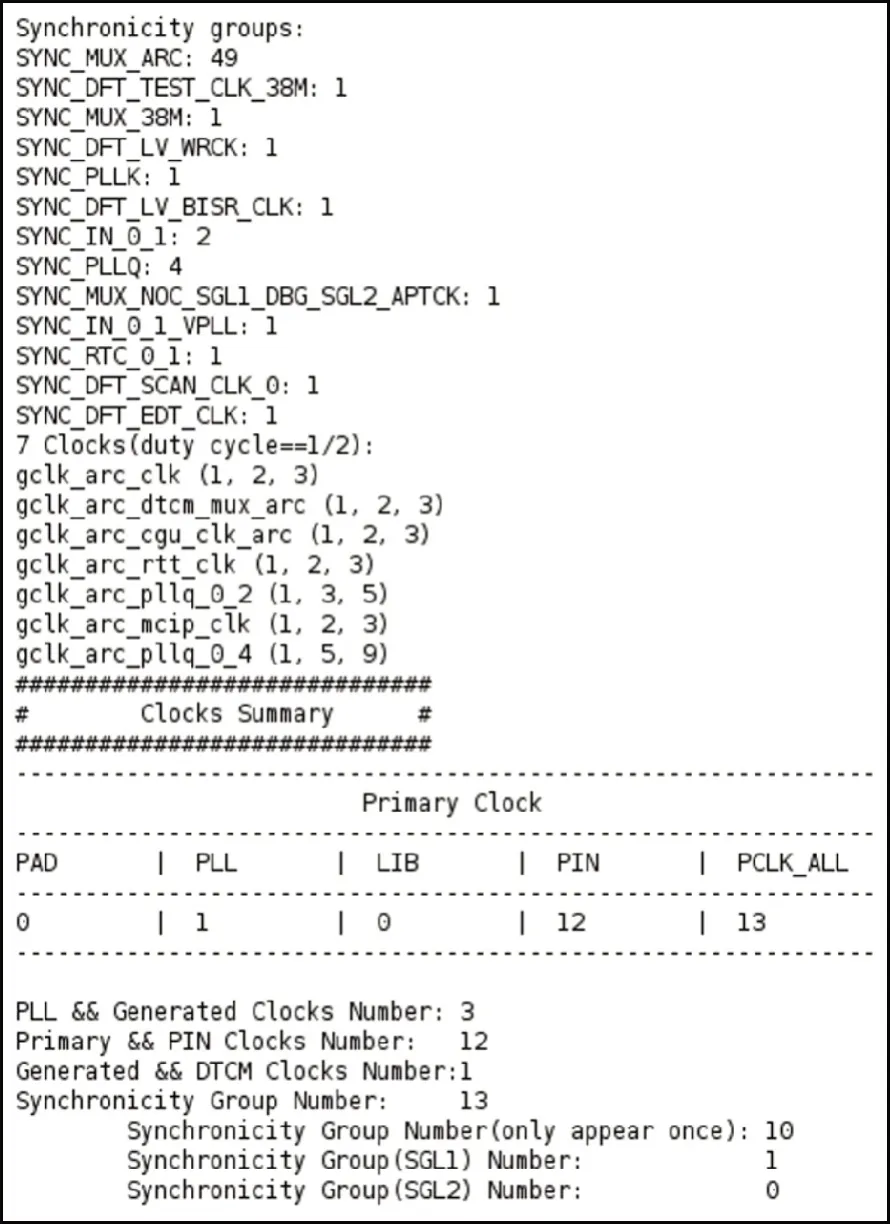

1.2 时钟信息表分析

在CM 首次导入某一个时钟信息表(Excel 格式)时,会同时完成时钟数据源的提取和数据库的建立。在提取时钟数据时,CM 既会就原有时钟数据做检查,也会将提取的数据做格式规范化[9]。在提取时钟数据时,会对整体时钟数据作报告,包括具体的时钟信息以及任何可能违反时钟数据要求的信息。例如在图3 中对导入的某个子系统的时钟信息做总结报告,其含有同步时钟组信息、时钟源信息、各个时钟的类型信息以及可能的时钟信息违例。

图3 时钟信息的一致性检查

以上所报告的时钟信息总结有助于CM 用户掌握目标系统的全局时钟信息。其后,用户可以将CM中的时钟信息导出到CSV 或者Excel 表格。用户也可以稍后继续通过CM 或者Excel 编辑导出的时钟信息表。在CM 导入时钟信息数据后,建议继续使用该工具做后续编辑和查看。CM 就时钟信息提供了多种常规操作,可以对某个时钟信息项完成创建、克隆、编辑等操作。

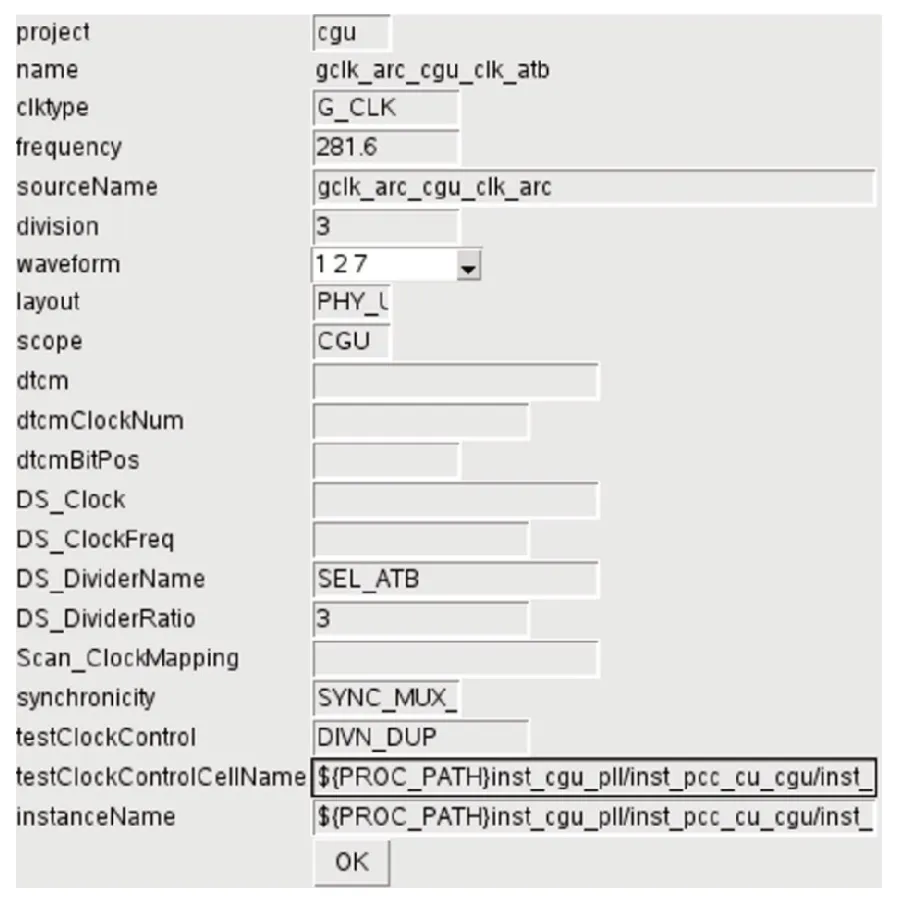

在编辑时钟信息项时,弹出的编辑界面可以显示该时钟信息项的详细属性。用户可以对其参数进行修改,在保存信息时CM 仍然会对该时钟信息做时钟信息规则检查。如果有信息违例的情况存在,则在对话窗口会弹出警告信息和详细的违例解释。时钟信息项的参数编辑界面如图4 所示。

图4 时钟信息项的参数编辑界面

1.3 时钟信息智能编辑

在CM 完成了初始的时钟信息导入、分析和规范化以后,全部的时钟信息就会被存入CM 内部的格式化时钟数据库中。在掌握了每一个时钟项的父时钟和子时钟后,便可以产生时钟树结构图。时钟树结构图有助于用户更好地理解时钟的组织,并且对时钟树上的时钟进行编辑。

CM 的另一个编辑功能是在用户编辑时钟时做若干项时钟规则检查,并且对于一些时钟信息做出自动修正[10]。这些时钟规则和信息修正包括:

1)检查时钟项编辑是否有效,并伴随时钟信息一致性检查。

2)如果当前时钟项编辑有效,则会自动编辑其他可能会受影响的时钟。例如父时钟A 从400 MHz降低为了200 MHz,则它的子时钟B 和C 的频率也会自动从200 MHz 降低为100 MHz。

3)如果对时钟树结构添加或者移除了某些时钟,例如将时钟A 的父时钟从时钟B 修改为时钟C,则在用户刷新了时钟列表后,时钟树结构也将得到重新排序。

4)一旦时钟树结构发生变化,在用户刷新了时钟树结构以后,CM 也会刷新其内部的时钟信息数据库,并对时钟信息项做重新排列。为了更好地分辨不同的时钟组,CM 会为其自动设定不同的颜色以用来识别时钟组信息。

1.4 时钟信息编辑历史

对于时钟信息表的编辑,有时需要对两个版本的时钟信息进行比较。采用CM 可以跟踪时钟信息的编辑历史。从图5 看到,可以对两个时钟信息表做比较,并给出分类的比较信息。详细的比较信息可以报告哪些时钟项的参数发生变化、哪些时钟项被移除和添加。这一特性可以方便地追踪时钟信息,即便时钟信息表由多位DE 维护,也可以利用该特性梳理在不同时钟信息表版本的编辑历史。

2 时钟信息提取过程

在CM 将不同设计部分的时钟信息导入、合并在一起后,便可以使用CM 的统一时钟信息为芯片开发过程的多个流程生成所需要的时钟信息输出。例如,CM 可以产生用来完成CDC 检查的脚本、用来做STA 流程的脚本、用来设定时钟频率的验证配置等[11]。CM 支持命令行模式和GUI 模式,帮助用户产生所需要的文件。

2.1 面向设计提取的CDC脚本

在CM 将多个设计部分的时钟信息提取之后,就可以利用中心化的规范时钟信息为不同的功能组产生所需要的脚本。CM 提供易用的用户编程接口(Application Programming Interface,API),用户可以利用这些接口来产生所需要的脚本。为CDC 做检查的Spyglass 工具支持的脚本格式和模板可以由DE 独立开发,而后由CM 结合开发的模板文件,即可从时钟信息数据中产生所需要的脚本[12]。

如果缺少自动化的CM 提取流程,以往在CDC流程中,DE 往往需要就时钟有关配置文件做逐一检查。而在CM 提取流程引入之后,一致性的时钟信息会尽可能避免人为引入的错误。

2.2 面向验证提取的时钟频率

在芯片验证过程中,对时钟频率的配置和检查也是一项必要的工作,继而保证在子系统或者系统验证中,各个时钟输入以及时钟之间的同步关系是正确配置的。否则,一些异步时序处理不恰当的地方可能会在仿真过程中被遗漏。以往在验证过程中人为完成的时钟设定和检查也会有出错的风险[13]。VE 利用CM 的一致性时钟信息,在准备了定制化的Python 脚本和模板文件后,就可以产生用来做时钟频率配置和检查的测试序列(C 或者UVM 格式)。

2.3 面向后端提取的STA脚本

CM 的一致性时钟信息也可以用来为BE 的后端流程工具(Design Compiler,DC)STA 和其他工具生成准确的时钟信息脚本。一旦能够确保时钟信息的准确性,则BE 将会对CM 工具产生依赖。在生成DC工具流程脚本时,每一个时钟项的信息不仅要准确,还需要保证与其父时钟、子时钟的信息均保持信息一致。因为如果有两个时钟之间的异步信息没有被描述准确,则产生的时钟脚本信息很有可能会对某些本应该完成同步处理的设计区域遗留盲区。一个典型的SoC 时钟数据库需要产生上百个类似的后端脚本,它们之间需要在时钟信息发生添加或者更新后,也能够完成及时的、准确的信息更新和文件结构组织[14]。CM 已经在多个芯片项目中得到推广,并且不再需要在为后端生成脚本时引入人工的修改,进一步减少了出错的可能性。

3 时钟信息用户界面管理端

除了图2 展示的CM GUI 时钟信息主窗口,CM也同时具备其他窗口用于DE、VE 和BE 对时钟信息的查询和编辑。CM 也像其他商业电子设计自动化(Electronic Design Automation,EDA)工具一样有菜单栏和多个嵌入的窗口界面。这些窗口界面除了主窗口以外,还包括时钟树窗口、时钟图窗口和时钟查找窗口。

3.1 时钟树窗口

在查看某个时钟项的信息时,往往需要跟踪它的父时钟或者子时钟。获取时钟的信息结构有助于理解相关时钟之间的关系。如图2 所示,用户可以在时钟树窗口点击某一个时钟项,然后选择查看时钟树图或者时钟序列图,也可以在时钟信息对话窗口获得该时钟详细的信息。

3.2 时钟图窗口

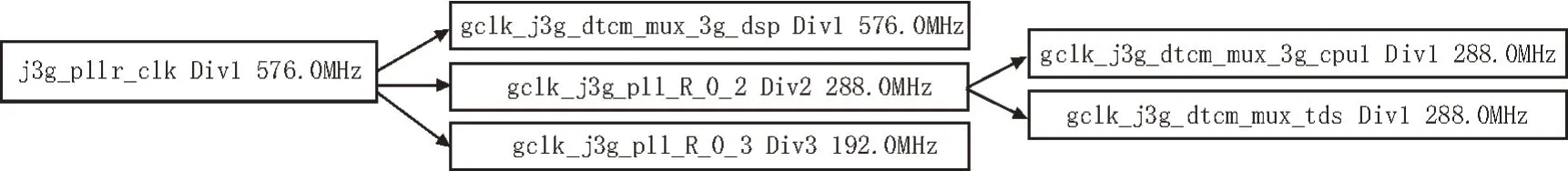

如果需要跟踪一个较大的时钟组,该时钟组内包含许多同源的时钟项,则除了选择时钟树图显示以外,也可以采用时钟图窗口来显示。用户可以在时钟信息主窗口或者时钟树窗口中选择某个时钟项,并由CM 生成该时钟的时钟图。图6 展示了由某个时钟项所产生的时钟图。时钟图的展示方式对于用户理解某些大型复杂的时钟组更为合适[15]。

图6 CM GUI中的时钟图界面

3.3 时钟查找窗口

伴随着时钟信息的集中管理,CM 中的时钟信息会增加到一个非常可观的数目。用户在此时需要利用一个独立的窗口用来查找和浏览一些他们感兴趣的时钟信息。例如有时用户需要查找某个子系统的一个时钟树结构信息。时钟查找窗口可以很好地满足用户想要实现时钟信息查找的需求,它也可以提供正则表达式查找模式。用户可以通过时钟查找窗口,输入时钟名称、类型、实例名、路径、设计块等信息进一步查找和过滤时钟信息。

4 测试验证

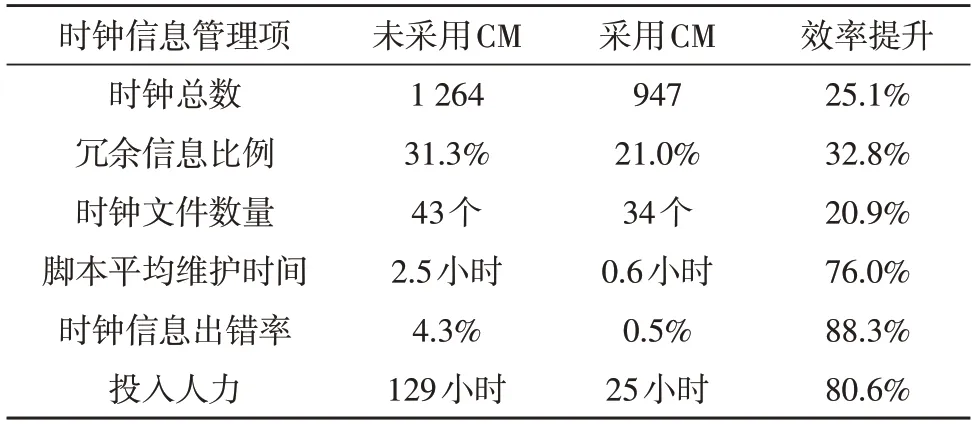

在将CM 投入到芯片研发后,为了得到该方案的比对数据,将同一款5G SoC 芯片在第一次流片(未采用CM)和第二次流片(采用CM)作为对比,分别就时钟总数、时钟冗余信息、时钟文件数量、投入人力、脚本维护时间、时钟信息出错率等方面做比较。

从表1 可以看到,5G SoC 芯片的时钟信息数目在使用CM 之后,可以得到有效的信息合并,继而减少管理的时钟总数。原有的时钟文件数量和冗余信息比例也能得到优化。由于采用了时钟信息合并、对比、分析等新功能,用来维护每个时钟有关脚本的时间得以有效缩短,而一致性和自动化的管理方式也显著降低了时钟信息出错率。在最终的投入人力对比中,未采用CM 时需要多人投入、更多工作时间,而在采用CM 后只需要一人管理所有的时钟信息,而且采用更少的时间即能够完成任务。

表1 CM投入时钟管理使用前后的数据

5 结束语

CM 是一个为芯片项目开发的用于解决时钟信息一致性的管理工具。在硅前(pre-silicon)开发和硅后(post-silicon)开发过程中均体现了它的价值[16]。CM 已经投入到多个大型芯片开发的过程中,有效地降低了在多个流程中时钟信息不一致所带来的风险。中心化的时钟信息维护方式和智能的时钟信息规则检查也有效地降低了在编辑时钟信息时出错的可能。

在投入使用CM 之前,DE、VE 和BE 在以往都是按照自己业务执行方式准备时钟信息,这增加了不同流程之间时钟信息不一致的风险。而在使用了CM 之后,只有管理时钟结构和设计的DE 才需要统一维护时钟信息。由于与其他EDA 工具的流程可以通过CM 支持的模板形式来完成定制化,CM 目前已经能够很快地投入到新项目的使用,并能够与各个业务部门之间做紧密的配合,加快时钟信息管理有关的流程,促进设计、验证和后端等过程的快速交付。