小型化高阻带抑制声表面波滤波器组件设计

张 伟,蒲志勇,龚 旭,温桎茹,杨桃均,吕 翼

(中国电子科技集团公司第二十六研究所,重庆 400060)

0 引言

声表面波(SAW)滤波器组件是一种包含多个滤波通道的滤波模组[1-2],一般集成有多颗SAW滤波器、射频开关等有源器件,通过外部控制码自由、快速切换射频开关以实现不同频段的滤波功能。基于SAW技术的多通道滤波组件已被广泛应用于通信、对抗、雷达、航空航天等领域[3]。随着通讯产品的发展,整机用户对于多通道滤波组件的体积、阻带抑制等要求也越来越高[4-9]。

本文介绍了一款包含8个滤波通道的SAW滤波器组件,其工作于L波段,-3 dB带宽大于48 MHz,插入损耗小于7 dB,带内幅度波动小于1.5 dB,近端阻带抑制大于70 dBc,组件尺寸仅为18 mm×15 mm×5 mm(不含引针绝缘子)。该SAW滤波器组件可应用于手持、背负等通信终端设备[10]。

1 小型化组件设计

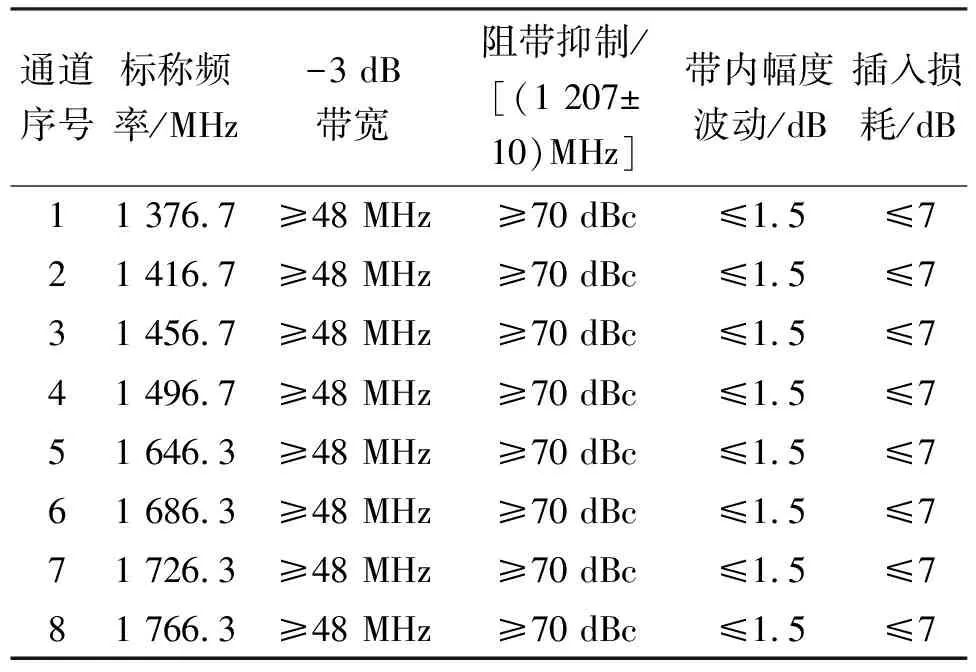

本文介绍了一款工作于L波段的SAW滤波器组件,具体指标参数如表1所示。

表1 组件指标要求

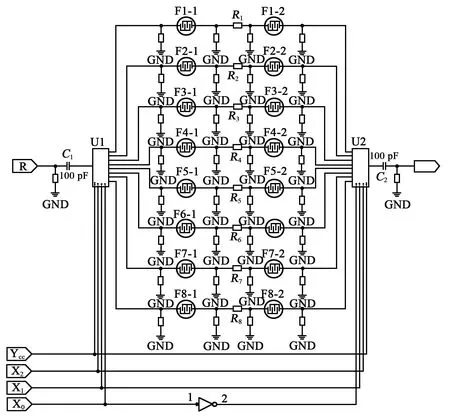

针对上述指标开展设计,组件设计结构如图1所示。组件设计方案是:通过两颗滤波器级联实现高阻带抑制,将滤波器和射频开关进行组合,通过控制码切换开关来实现不同通道的滤波功能。

图1 组件设计结构框图

1.1 电路设计

根据标称频率、插入损耗、带外抑制及结构尺寸要求的综合考虑,采用小型化SMD3030C封装表贴SAW滤波器、集成开关等元器件,双面贴装于一块多层电路板上,并安装于金属腔体内的技术方案。根据图1进行电路原理图设计,如图2所示。

图2 组件电路设计

本文采用两级SAW滤波器级联的方案以满足阻带抑制大于70 dBc的要求,将组件指标分解到单颗SAW滤波器,指标分解如下:

1)-3 dB带宽

该指标主要由SAW滤波器决定,以第一通道的SAW滤波器为例。滤波器是两级级联,考虑到温度漂移和制作误差的影响,将单级滤波器-1.5 dB带宽设定为不低于50 MHz。

2) 插入损耗

该指标主要由滤波器及开关决定。组件要求总的损耗在7 dB内,考虑到单只开关损耗约在1 dB,由于采用了两个滤波器级联,两级滤波器的损耗控制在5 dB内,单个滤波器的损耗控制在2.5 dB内。

3) 带内幅度波动

该指标主要由SAW滤波器以及匹配调试效果决定。考虑到滤波器采用级联结构,带内波纹可能会严重恶化,组件要求带内幅度波动控制在1.5 dB内,因此,单个滤波器的带内幅度波动要求控制在0.7 dB内。

4) 阻带抑制

该指标主要由SAW滤波器本身的阻带抑制及电磁兼容性等决定。本项目阻带抑制要求大于70 dBc,单个滤波器的阻带抑制无法满足要求,故采用两级滤波器级联的方式。为了产品调试时留有一定的余量,需要SAW滤波器的阻带抑制指标优于产品指标至少3 dB,因此要求单个滤波器的阻带抑制大于38 dBc。

5) 外形尺寸

组件尺寸为18 mm×15 mm×5 mm。该指标主要由开关尺寸、滤波器尺寸和匹配电路决定。为了满足小体积的要求,滤波器采用SMD3030C封装来实现小型化。

1.2 SAW滤波器设计

本文组件包含8款SAW滤波器,以第8通道的SAW滤波器为例,要求滤波器的中心频率为1 766.3 MHz,插入损耗小于2.5 dB,-1.5 dB带宽大于50 MHz,阻带抑制大于38 dBc,带内幅度波动小于0.7 dB。

SAW滤波器由陶瓷外壳底座、金属盖板及SAW滤波器芯片构成。外壳采用SMD3030封装,典型尺寸为3.0 mm×3.0 mm×1.2 mm。芯片与外壳之间采用金丝键合,封装方式采用平行封焊工艺,以保证产品良好的气密性。产品整体尺寸小,质量小。

根据上述要求制作的SAW滤波器,其实测响应曲线如图3所示。滤波器实测中心频率为1 766.18 MHz,插入损耗为-1.1 dB,-1.5 dB带宽为57.6 MHz,阻带抑制为40 dBc,带内幅度波动为0.3 dB。

图3 单颗SAW滤波器实测曲线

1.3 PCB版图设计

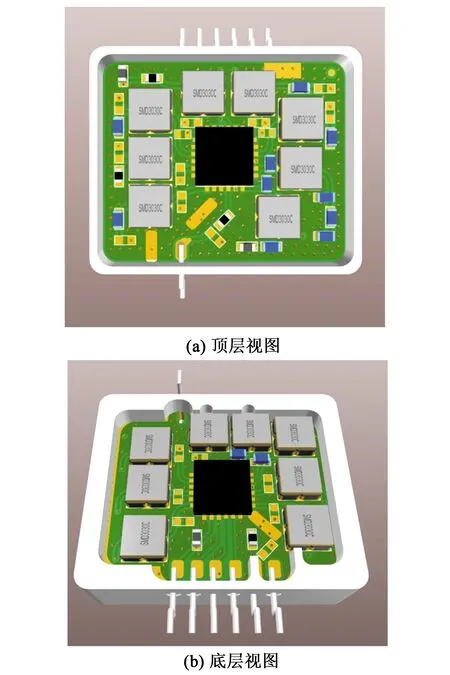

为了满足组件小体积的要求,版图布局采用滤波器环绕开关布局法:将开关置于版图中心,器件环绕开关四周放置,以实现更加紧凑的结构。选用小体积器件,采用双面布局方式,器件紧凑排列,充分利用壳体内部空间,实现产品小型化。

版图设计时,射频走线需满足50 Ω的阻抗。根据传输线理论,其特征阻抗为

(1)

式中:εr为材料介电常数;h为传输线与基板的介质厚度;w为传输线宽度;t为传输线厚度。

根据SI9000软件计算可得到走线宽度约为0.16 mm,计算方法如图4所示。元器件的焊盘宽度一般远大于0.16 mm,易导致射频走线的阻抗不连续,从而影响组件的损耗、带内波纹等指标,因此需要根据计算来优化元器件焊盘的阻抗,让大焊盘不会因阻抗不连续而产生太大的信号反射。设计时,先将射频信号的焊盘对应位置的中间层掏空,再用SI9000软件计算出该掏空处所对应的层数,以实现焊盘50 Ω阻抗控制。同时在级联滤波器中间增加一个π型匹配网络,以改善级联后的通带性能。

图4 PCB阻抗控制

为了满足阻带抑制指标,采用两级SAW滤波器级联方式以及多通道抗干扰布局方法,以实现近端70 dBc以上的阻带抑制。设计时需要考虑射频辐射影响,当射频走线有足够的参考平面时,电场大部分被参考平面所耦合,只有少部分电场辐射到了空间中。为了进一步较少辐射的影响,让射频线的四周都存在参考平面,此时电场全部被参考平面所耦合,基本无电场辐射到空间中。因此,电路设计时,在射频走线旁设置大量接地孔,以最短路径将辐射引入地,可以避免射频辐射带来的影响。印制板设计时需注意通道之间的串扰,降低输入、输出端口之间的直通耦合。射频走线要有最短的接地回路,电源、控制信号要远离射频信号,要有完整的接地铜皮屏蔽,避免射频信号通过电源线直接串扰。组件设计版图如图5所示。

图5 组件设计图

2 版图仿真

为了验证小型化滤波组件是否能够达到高阻带抑制的指标,对滤波器、开关等元器件的射频性能进行联合仿真分析。若各通道相互存在串扰信号,信号相位叠加后可能出现不同频率在幅度上的差异,导致信道通带内的幅度波纹变大。利用HFSS软件对组件进行仿真,将PCB版图导入建立仿真模型,仿真结果如图6所示。由图可见,通带内插入损耗在5~6 dB,在1~1.25 GHz较低频段内,组件的阻带抑制高于80 dB;在2~3 GHz较高频段内,组件的阻带抑制高于60 dB。

图6 组件仿真曲线

3 实验测试

根据上述方法制作了多通道级联滤波组件,实物如图7所示,各通道实测曲线如图8所示。

图7 组件实物图

图8 组件仿真和实测曲线对比

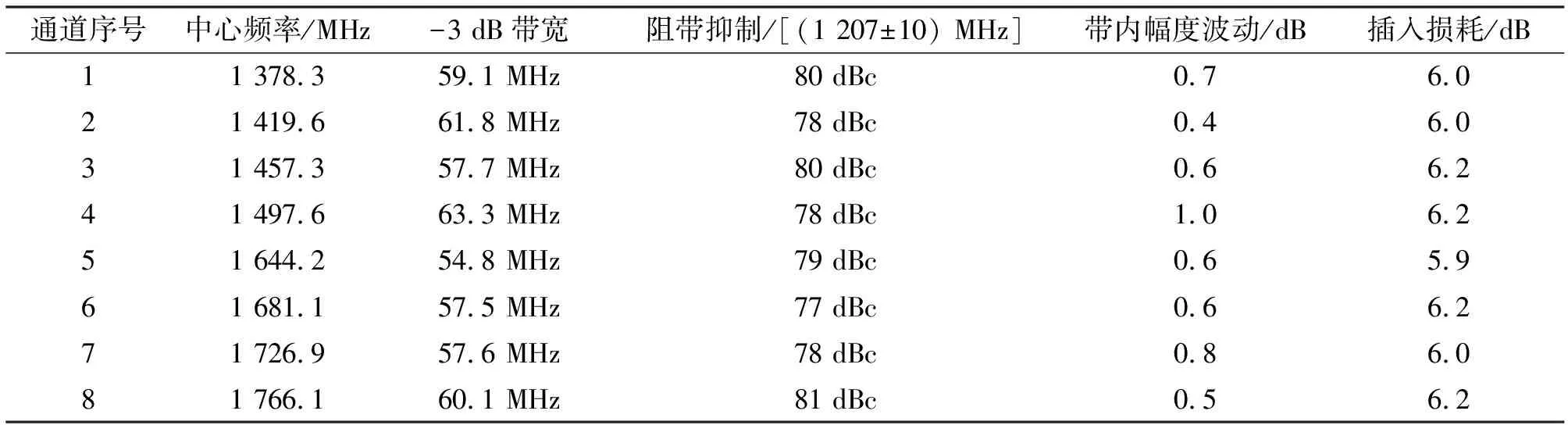

组件实测数据如表2所示,由表可见,其满足表1中各项指标要求。

表2 组件实测数据

4 结束语

本文介绍了一款小型化、高阻带抑制SAW滤波器组件的设计实例,组件外形尺寸仅为18 mm×15 mm×5 mm,其-3 dB带宽大于48 MHz,插入损耗小于7 dB,带内幅度波动小于1.5 dB,近端阻带抑制大于70 dBc。本文提出的版图设计方法实现了在紧凑空间内的小型化布局,组件同时实现了较高的阻带抑制,对同类型产品的研制具有指导意义。