载荷管理器通用地检测试板卡的系统设计*

李旭峰 周 莉 朱 岩 赵文杰 郝 澄

1(中国科学院国家空间科学中心 北京 100190)

2(中国科学院大学 北京 101499)

0 引言

在进行星上设备研发的同时,还需要设计有相应的地面检测设备(简称地检)对其进行功能和性能检测,确保满足任务要求[1]。卫星载荷分系统的载荷管理器负责星上有效载荷的统一供配电管理、遥测遥控、运行控制和数据处理,以及卫星平台与载荷之间的通信,是卫星重要功能部件之一。不同的卫星载荷分系统配置载荷的数量、硬件接口、软件协议等各不相同,导致不同型号任务的载荷管理器功能和接口各不相同,相应的载荷管理器地检需要进行个性化设计。不同型号任务载荷管理器的差异性使得地检的通用性一直成为设计难点[2]。

卫星平台对外电接口包括供配电接口、总线接口、科学数据输入接口、直接遥测输入接口、遥控输出接口、秒脉冲输出接口等[1-4]。载荷对外电接口包括供配电接口、总线接口、科学数据输出接口、直接遥测输出接口、遥控输入接口、秒脉冲输入接口等[5,6]。载荷管理器既连接卫星平台又连接多台载荷,因此载荷管理器接口分为对平台和对载荷两种。按照电接口传输速率可以分为高速接口和低速接口[6-8];高速接口速率为几百Mbit·s-1至几Gbit·s-1,通常采用同轴电缆或者光纤接口;低速接口包括速率小于100 Mbit·s-1的接口,以及一些分立的遥测遥控接口。星上总线接口有1553 B总线、CAN总线、RS422总线、RS485总线等,星上低速科学数据接口包括单线制或者三线制的LVDS接口或者RS422接口。

载荷管理器地检的常规方案是每种接口使用独立的设备或硬件板卡实现,再通过一个或多个上位机控制。当前常规方案一般是采购工控机[3,9],即带有PCIE接口的1553 B板卡、RS422板卡、LVDS板卡、模拟量采集板卡、OC板卡等货架设备,每个板卡上有可编程器件FPGA,在工控机进行上位机的界面设计以及与每个板卡FPGA的接口和逻辑设计。这种方案的缺点是成本高,集成度低,软件设计复杂,需要编程的FPGA数量多,通用性差。为减少对地检的人力、物力和时间投入,提出一款硬件接口兼容性高、软件可配置、通用性高、使用成本低、与上位机接口简单的地检板卡,为多种任务型号的载荷管理器提供支持,加速管理器的研制进度,使得每个任务型号无需单独研制一台专用的地检。

本文根据地检实现通用性在数据格式与物理层约定的难点,针对以上问题,分析了板卡硬件设计和FPGA软件设计方法,并对地检测试板卡通用性进行测试,验证板卡设计的可行性。

1 地检测试板卡系统设计

载荷分系统结构如图1 所示。为了适配不同型号任务载荷分系统的硬件和软件接口协议[3,10-12],基于配置文件的通用地检测试板卡的系统设计基本思想是:地检测试板卡集成尽可能多通道的常用硬件接口,在硬件上通过拨码开关或跳线实现物理层的兼容;软件方面,在FPGA设计时允许上位机通过配置文件修改内部寄存器,并将配置文件存储在非易失性存储器Nor flash上,后续上电自动从Nor flash加载寄存器配置,不需要重新配。适配不同任务时,FPGA代码不需要重新写,只需要设置对应的配置文件,达到通用的要求。

图1 载荷分系统结构Fig.1 Load subsystem structure

下面从硬件设计、FPGA设计和上位机设计三方面进行分析。

1.1 硬件接口设计

地检测试板卡系统架构如图2所示,板卡由4部分组成,包括与上位机的通信模块、缓存和配置文件模块、模拟平台接口模块和模拟载荷接口模块。

图2 地检测试板卡系统Fig.2 Block diagram of ground testing board system

与上位机的通信模块包括RS422接口和百兆/千兆网口,用于接收上位机的指令和配置文件等,并且发送地检板卡状态和接收数据。缓存和配置文件模块由SRAM和Nor flash组成,SRAM用于缓存科学数据,Nor flash用于存储对应型号任务软硬件接口协议的配置参数。模拟的平台接口模块具备OC指令输出、遥测采集、秒脉冲产生、科学数据接收功能;模拟的载荷接口模块具备载荷总线响应、科学数据发送、载荷模拟量产生、OC指令接收检测、秒脉冲接收、GPIO接口功能。

板卡硬件设计的硬件接口和通道数如表1所示,能够满足绝大部分卫星平台、载荷硬件接口和数量的要求;由于1553 B总线、CAN总线板卡技术成熟,接口标准,以及高速Serdes接口速率较高,因此未在地检板卡中集成,可以采购货架板卡集成在工控机中。

表1 通用地检测试板卡硬件接口Table 1 Hardware interface of ground testing board

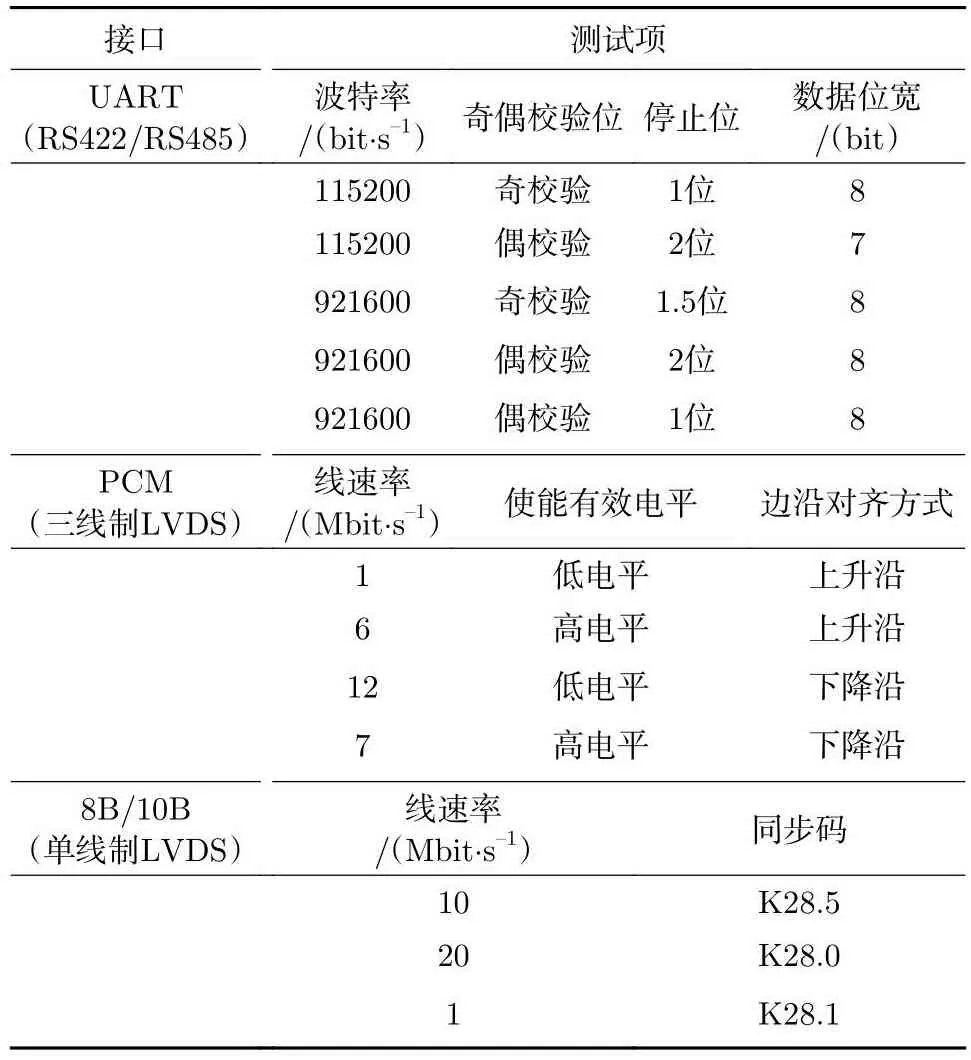

板卡支持的科学数据和载荷总线通道,支持UART协议、三线制LVDS协议和单线制8 B/10 B编码的LVDS协议。UART协议的奇偶校验位、停止位、数据位和波特率可配置,数据位支持8位和7位,停止位支持1位、1.5位和2位。三线制LVDS协议的使能和速率均可配置,支持低有效和高有效的使能,数据支持在时钟的下降沿或上升沿改变;单线制LVDS的K码和速率均可配置。

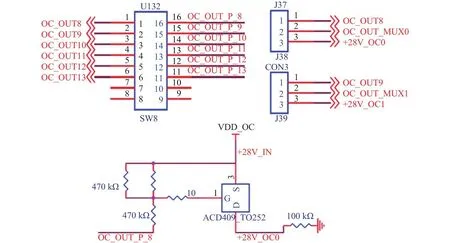

硬件的可重构设计基于拨码开关/跳线和通过软件重配置FPGA管脚控制寄存器实现。如图3所示,OC指令输出通过拨码开关和跳线选择,若OC指令为输出低电平脉冲,拨码开关U132将置于关闭,跳线J37短接1/2两点;若输出指令为高电平脉冲,拨码开关U132将置于打开,驱动后级MOSFET(U136)工作输出高电平,跳线J37短接2/3两点。

图3 基于拨码开关/跳线的硬件可重构设计Fig.3 Hardware reconfigurable design based on dial switch/jumper

科学数据输入与输出选择RS422还是LVDS接口,由FPGA内部寄存器控制,该寄存器控制输入与输出接口连接内部UART逻辑、三线制或者单线制逻辑模块。具体通过一个寄存器控制多路器,根据寄存器的值导通多路器的相应通路实现。寄存器配置为0时,输入与输出使用UART协议;配置为1时,输入与输出使用三线制PCM协议;配置为2时,输入与输出使用8 B/10 B单通道协议。

1.2 FPGA程序设计

FPGA设计根据外部输出接口(见图2),分为配置控制、科学数据、命令工参、DA控制、AD采集等功能模块,这里重点介绍配置控制、科学数据、命令工参等核心功能模块。

1.2.1 配置控制模块

FPGA通用性的设计由配置控制模块和Nor Flash实现。具体型号任务应用时需根据平台和载荷的接口类型、数量、数据格式对地检测试板卡上的FPGA寄存器进行配置,并将这些信息按照设计的地址定义存放到Nor Flash中;后续上电不需要上位机重新配置FPGA内的寄存器,由配置控制模块自动从载荷配置的Nor Flash中将配置信息读到各功能模块。配置信息包括科学数据格式、载荷指令格式、工程应答格式、通信协议选择及配置、常用功能接口模块的配置。

载荷管理器地检测试板卡的具体软件工作流程如图4所示。针对具体型号任务的载荷指令和科学数据格式,形成载荷指令和科学格式配置表;上位机通过串口将载荷指令和科学格式配置表发送给FPGA,由FPGA写入载荷配置表Flash中。后续FPGA上电后,首先检查载荷配置Flash的地址0,验证配置Flash中的数据是否可用:如果可用,则按照载荷配置Flash中数据配置各功能单元的寄存器组,等待上位机的启动命令,根据上位机的命令响应处理结果;如果不可用,则进入等待配置命令模式。

图4 FPGA配置控制模块工作流程Fig.4 FPGA configuration control module workflow

1.2.2 科学数据模块

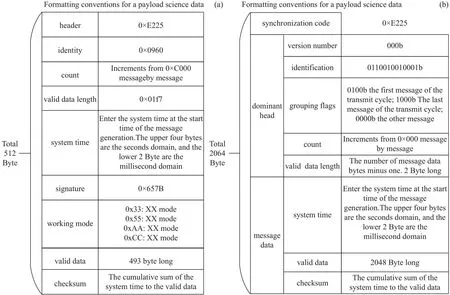

不同的任务型号科学数据以及指令应答数据包格式一般是不同的[6],主要体现在数据包内字段的组成不同、单一字段长度不同、单一字段取值不同和数据包长度不同,如图5所示。科学数据与命令工参中多变的数据格式使得地检测试板卡FPGA设计很难通用。

图5 某两个任务型号科学数据的数据格式对比Fig.5 Data format comparison of scientific data of two task models

针对这一难点,采用基于序列解析的数据包生成方法。将数据格式中的字段根据其特点进行分类、编码(见表2)。科学数据与命令工参的数据包中固定不变的字段,例如包同步码、版本号、包标识、载荷标识等,定义为固定字节;循环冗余校验(CRC)、校验和等需要根据校验规则计算得出的字段,定义为校验字节;有效数据、科学数据等需要填入随机数或有序自增数的字段,定义为填充字节;需要填入实时时间的时间码字段,定义为时间码字节;包序列计数、分组标识、包计数等起到计数作用的字段,定义为计数字节;在命令工参中,由于无需关注时间码、包计数等字段,因此均被归纳为无关字节。

表2 字段的抽象表示Table 2 Abstract representation of fields

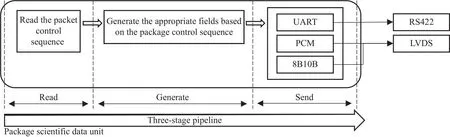

依照上述规则将具体数据包内各个字段转换为由编码表示的组包控制序列(见表3),上位机将序列以及对应数据写入科学数据模块,科学数据模块根据读出的编码在数据包对应字节位置填入相应的数据。具体FPGA的实现如图6所示,分为读取、生成、发送三个阶段。读取是读取上位机发送过来的组包控制序列,生成是根据组包控制序列的编码填充数据包,发送是根据任务要求的协议产生相应的时序输出。

图6 科学数据模块架构Fig.6 Scientific data module architecture

1.2.3 命令工参模块

命令工参模块采用与科学数据模块相同的方法解决数据格式不同的问题,但命令工参模块还需要判断接收指令的有效性。具体实现方法是,命令工参模块会根据编码序列预生成一个字节,当收到一个字节时,会将当前接收到的字节与预生成的字节比较,然后根据编码序列生成下一个字节,以此循环。若两个字节不相同,则会生成错误信息发送至应答控制模块,用于控制应答数据包的生成。

与科学数据包不同的是,在某些任务中,指令数据包的长度也存在较大差异,例如校时时间码指令只有6字节,而平台状态信息指令长数百字节。有的任务指令数据包存在有效数据字节数字段,有的任务指令数据包不存在有效数据字节数字段,无法推出整包的长度。因此在指令数据包不可预知长度时,判别指令数据包是否接收完毕,是地检测试板卡通用设计的另一个难点。

为此,采用一种超时接收的方法,即将依据长度接收指令数据包转换为依据时间接收指令数据包。当数据接收接口超过规定时间未接收到数据时,即认为指令数据包接收完毕。在任务型号中一般严格规定接收到指令数据包后的应答时间,为此设计了一个经验公式用于计算超时时间,保证命令工参模块可以接收到完整的指令数据包,并且应答数据包的时间间隔满足任务要求。

超时接收用于解决命令工参中指令数据包长度不可知的问题,以等待时间为依据判别指令数据包是否接收完毕。设超时接收等待时间为T,当一个字节接收完毕后,若在时间T内未收到下一个字节,则认为当前指令数据包接收完毕,将接收的数据送至指令解析单元,并复位接收单元准备接收下一个指令数据包。指令解析单元接收到指令数据包后,核验数据包的格式和内容是否正确。若数据包的格式与文件要求的格式不符,则不响应该条命令,并通过串口向上位机发送链路异常信息。若数据包的格式与文件要求的格式相符,则根据数据包内容的正误分别应答指令正确应答数据包和指令错误应答数据包。

在命令工参中不同类型的应答数据包的回复时间的要求一般是不同的,设一路命令工参存在n种应答数据包,每种应答数据包的回复时间最大不超过ti,max,在吞吐率为1的情况下每种应答数据包发送完毕所需时间为ti。等待时间T不应大于Tmax, 即

当时间T小于Tmax才能严格保证应答数据包能在规定时间内发送完毕。设接收一个字节的数据需要时间tr,则T应满足

命令工参模块按照上述功能划分为解包单元和组包单元,如图7所示。解包单元与科学数据模块类似,根据上位机配置的序列进行比对,将比对结果发送给组包单元,并增加了超时接收检测功能;组包单元根据接收到的指令进行组包,组包格式也是按照配置序列格式进行响应。命令工参模块目前支持最常用的UART协议。

图7 命令工参模块架构Fig.7 Structure of command working parameter module

整个功能单元按流水线处理,保证命令工参模块的吞吐率为1,并且发送应答包时不会因为数据未准备好而中断。

命令工参模块的设计解决了数据格式多样和指令数据包数据无法预知长度的问题,是一种与具体数据格式和数据长度无关的实现方法,具有更高的通用性。

1.3 上位机设计

上位机通过RS422接口对FPGA进行控制和状态读取,通过以太网口接收科学数据。如前所述,基于序列的配置文件由上位机生成。使用地检测试板卡时,只需要将给定需求/数据格式转化为对板卡寄存器的配置,再将全部寄存器待配置值组织成配置表写入FPGA内,即实现了FPGA参数的重配置。另外,上位机可以周期性读取各个功能接口采集到的数据并实时显示,为用户实时监测工程参数。

如图8所示,板卡中设计了一片Norflash用于存储最新的寄存器配置表,由上位机控制FPGA进行维护。板卡上电后,FPGA自动读取存储在NorFlash内的寄存器配置表并配置内部寄存器,用户将无需再次生成并写入寄存器配置表。寄存器配置表可以通过上位机界面或者excel表生成,通过excel管理寄存器配置表便于用户进行配置项编写、版本管理和调试。

图8 上位机架构Fig.8 Upper computer architecture

2 系统验证

以科学数据输出为例对板卡的通用性进行验证。科学数据输出功能是板卡的核心功能模块,也是板卡的设计要点。

2.1 实验平台

搭建一套地检测试板卡测试平台,包含直流稳压电源、示波器、工控机箱、地检测试板卡和电压表各一块。另外,工控机箱配有一块PCIe接口的LVDS板卡,用于接收地检测试板卡发出的三线制LVDS和单线制LVDS数据,还配有一块MOXA盒通过RS422通路与板卡相连,用于向板卡发送命令工参的指令数据包并接收板卡的数据。示波器用于测量板卡接口的参数,电压表用于测量模拟量产生接口的模拟量,检查板卡的输出是否符合预期。

2.2 科学数据模块通用性实验

为验证科学数据模块的通用性,首先设计了一系列接口测试例程,用于遍历接口的全部功能,其次选取多个任务型号的科学数据格式,测试科学数据模块产生的数据是否能满足全部要求。测试流程如下。

步骤1根据表4通过上位机配置板卡,使板卡产生相应的接口。

表4 板卡传输接口测试例程Table 4 Test routine of board transmission interface

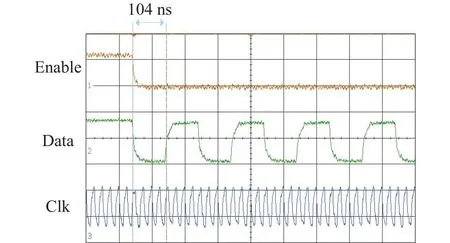

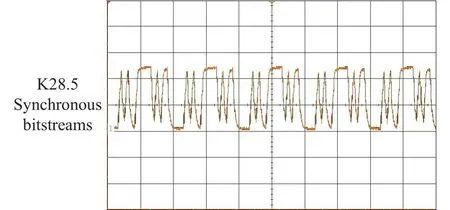

步骤2使用示波器测试对应引脚,观察波形是否符合预期。RS422接口需要关注波特率、校验位、起始位、停止位、数据位是否符合预期,如图9所示。PCM接口需要关注线速率、使能有效电平和数据位变化时刻与时钟边沿的对齐情况是否符合预期,如图10所示。8B/10B需要关注线速率和同步码流是否符合预期,如图11所示。重复步骤1和步骤2遍历表4的测试用例。

图9 RS422接口波形Fig.9 Waveform of RS422 interface

图10 PCM接口波形Fig.10 Waveform of PCM interface

图11 8B/10B接口波形Fig.11 Waveform of 8B/10B interface

步骤3以嫦娥系列任务型号的接口控制文件中对科学数据的格式要求作为测试例程,通过上位机配置板卡,使板卡发送对应数据。

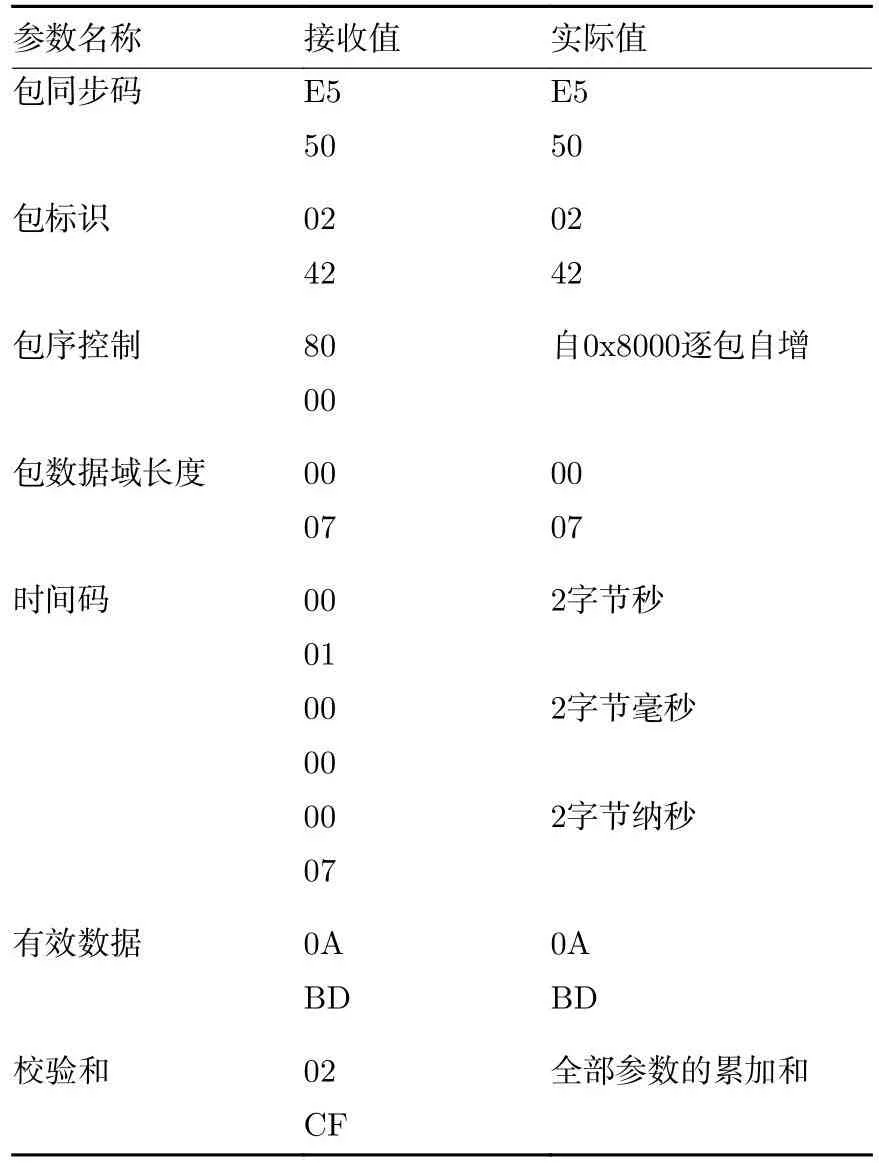

步骤4使用MOXA盒和LVDS板卡接收数据,通过上位机观察接收的数据是否符合预期,如表5所示。其中RS422接口发送的数据通过MOXA盒接收,LVDS接口发送的数据通过LVDS板卡接收。重复步骤3和步骤4遍历测试用例。

表5 科学数据Table 5 Scientific data

遍历表4和嫦娥系列任务型号的数据格式的全部测试用例后,测试结果全部符合预期。

2.3 命令工参模块通用性实验

为验证命令工参模块的通用性,首先设计了一系列接口测试例程,用于遍历接口的全部功能,其次选取多个任务型号的命令工参数据格式,测试命令工参模块是否能正确解析指令数据包并应答对应的应答数据包。测试流程如下。

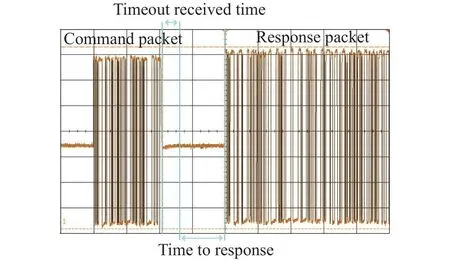

步骤1根据表4中UART部分通过上位机配置板卡,使板卡产生相应的接口。该模块还需要配置超时接收时间与应答间隔时间,如图12所示。

图12 命令数据包的接收与应答Fig.12 Command packet reception and response

步骤2使用示波器测试对应引脚,观察波形是否符合预期。

步骤3以嫦娥系列任务型号的接口控制文件中对命令工参的格式要求作为测试例程,通过上位机配置板卡并发送指令数据包,使板卡应答对应的应答数据包。

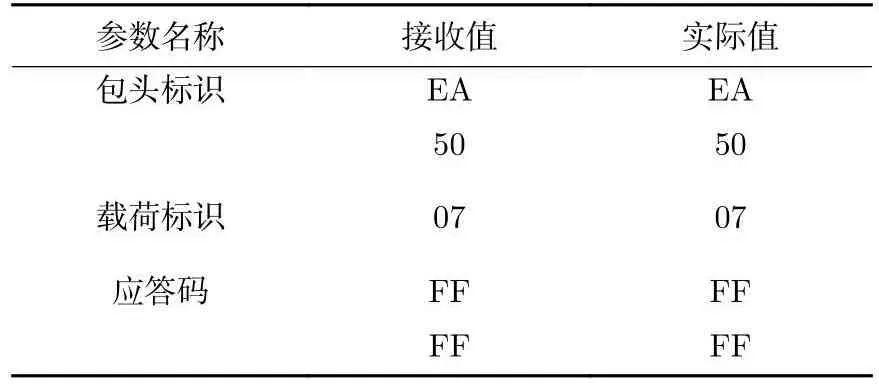

步骤4使用MOXA盒接收数据,通过上位机观察接收的数据是否符合预期,如表6和表7所示。重复步骤3和步骤4遍历测试用例。

表6 指令正确应答数据包Table 6 Response packet when command packet is correct

表7 指令错误应答数据包Table 7 Response packet when command packet is wrong

遍历表4和嫦娥系列任务型号的数据格式的全部测试用例后,测试结果全部符合预期。

2.4 其他功能模块通用性实验

为了验证模块OC指令控制模块、模拟量生成模块、秒脉冲生成模块和PWM输出模块的通用性,设计了一系列接口测试例程,用于遍历接口的全部功能。

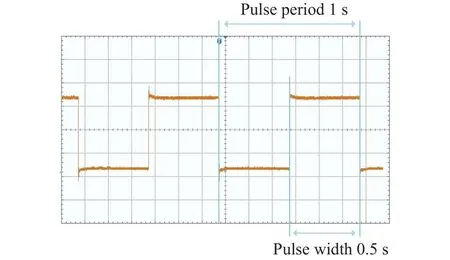

步骤1根据表8中接口测试例程配置板卡,使板卡产生相应的接口。

步骤2使用示波器和电压表测试对应引脚,观察波形是否符合预期。OC指令控制模块需要关注有效电平与有效电平持续时间,如图13所示;模拟量生成模块需要使用电压表测量对应管脚,观察电压值是否与配置值相符,误差需要在±20 mV内;秒脉冲生成模块与PWM输出模块基于同一模块实现,需要关注脉冲周期和脉冲宽度,如图14所示。

图13 OC指令输出波形Fig.13 Waveform of Open Collector (OC)

图14 PWM输出波形Fig.14 Waveform of Pulse Width Modulation (PWM)

遍历表8的全部测试用例后,测试结果全部符合预期。

3 结论

针对不同型号任务载荷硬件接口和软件协议差异大导致载荷管理器地检通用性差的难题,提出了一种硬件可重构、软件协议可配置的通用地检测试板卡的系统设计,该设计具有高集成度、高通用性、低成本、可重用、开发界面友好等优点,保证了项目研制进度,降低了对开发、成本和测试的需求。地检测试板卡已在嫦娥任务多台载荷管理器中得到应用,后续将支持空间科学卫星以及其他应用卫星等多个任务,具有较高应用价值。