基于FPGA的DDR SDRAM测试平台设计

谢树平,毛源豪

(湖南艾科诺维科技有限公司,长沙 410000)

0 引言

现场可编程逻辑门阵列(FPGA,field programmable gate array)是一种半定制芯片,因其独特的电路可编程特性区别于其他器件。随着近年FPGA芯片的快速发展,其内部的资源数量与丰富度显著提升[1]。FPGA在通信、图像处理[2]、深度学习[3]、人工智能[4]与数据中心[5]等领域发挥着重要的作用。双倍数据传输速率同步动态随机存储器(DDR SDRAM,double data rate synchronous dynamic random access memory)是FPGA板卡中最常用的高速缓存解决方案。DDR SDRAM的工作情况直接影响到整个设备能否正常运作,所以DDR SDRAM测试也是FPGA板卡测试中最重要的测试项目之一。此前对DDR SDRAM的测试主要通过DDR SDRAM控制器的调试端口进行。然而这种测试方案存在操作人员学习门槛高、测试流程不灵活、无法自动生成测试报告等缺点。操作人员在测试前需要充分了解调试端口中约200个信号的定义、各控制信号间的逻辑关系以及操作DDR SDRAM的相关知识。此类方案在生成比特流后测试内容相对固定,可在线配置的测试参数有限,无法设置测试队列并自动完成。且没有生成测试报告的功能,相关数据需要操作人员手动记录。降低了工作效率,增加了出错风险。

在FPGA与DDR SDRAM的数据交互设计中,设计者通常使用FPGA厂家提供的DDR SDRAM控制器。比如Xilinx公司为旗下的FPGA提供了成熟的存储器接口生成器(MIG,memory interface generator)。MIG内包含控制器和物理层,设计者可以通过用户接口或先进可扩展接口(AXI,advanced eXtensible interface)访问DDR SDRAM。文献[6]提出了一种基于MIG用户接口的应用,在MIG用户接口的基础上设计了先入先出(FIFO,first in first out)接口,使其既拥有FIFO缓存简单易用的特点,又有DDR SDRAM存储空间大的优势。文献[7]在数据FIFO接口的基础上增设了一个命令/地址FIFO,实现了随机读写功能。

在DDR SDRAM控制器的测试技术中,通常使用的方案是向DDR SDRAM写入特定的pattern,然后读取数据并校验数据一致性。文献[8]提出了一种包含内部自测(BIST,built-in self-test)模块的DDR SDRAM控制器。该模块将来自随机数发生器的数据写入DDR SDRAM中,并将读出的数据与写入的数据在数据比较器中进行对比,从而实现自监测的功能。文献[9]提出了一种基于在线逻辑分析仪(ILA,integrated logic analyzer)知识产权(IP,intellectual property)核验证DDR SDRAM控制器的方法。使用AXI Trafficgen IP核产生AXI总线的读写事务,并用ILA抓取AXI总线上的信号,分析其时序与数据正确性。

实际应用中,通常使用标准JTAG接口实现PC上位机与FPGA之间的通信。文献[10]设计了一种基于FPGA的DDR SDRAM通用测试电路。该设计使用JTAG接口启动测试电路,电路自动完成整个测试过程并将测试结果从JTAG接口传回PC上位机。文献[11]提出了一种使用工具命令语言(TCL,tool command language)脚本语言测试数字电路的方法。该方法通过在Vivado软件中执行TCL脚本实现自动对调试核虚拟输入输出(VIO,virtual input output)的修改与读取,从而达成高效率的测试。文献[12]提出了一种基于LabVIEW软件调用TCL脚本的测试方法,将Vivado软件的启动与执行TCL脚本的命令封装为批处理文件,实现了自动化测试与生成报表。文献[13]提出了一种FPGA的AXI总线接口调试方法,通过使用JTAG to AXI IP核,允许用户通过执行TCL脚本来对AXI总线上的从设备进行访问。

为了解决当前FPGA板卡中DDR SDRAM测试工作复杂及效率低下的问题,本设计做了如下工作:

1)设计了DDR SDRAM控制器的测试器IP核MIG Tester。该IP核具有生成读写事务、校验数据、记录数据读写用时等功能。同时MIG Tester支持对数据位宽、pattern类型、起始地址、测试地址范围、突发长度等参数的在线配置,具有高度的灵活性。

2)设计了TCL脚本。用于控制VIO、ILA、JTAG to AXI 等IP核,从而实现对整个测试流程的控制以及测试结果信息的读取。

3)设计了上位机图形界面程序。将测试流程中各个阶段需要执行的TCL脚本封装。通过文本框打印测试信息,同时自动生成测试报告,便于操作人员使用。

1 测试平台架构及原理

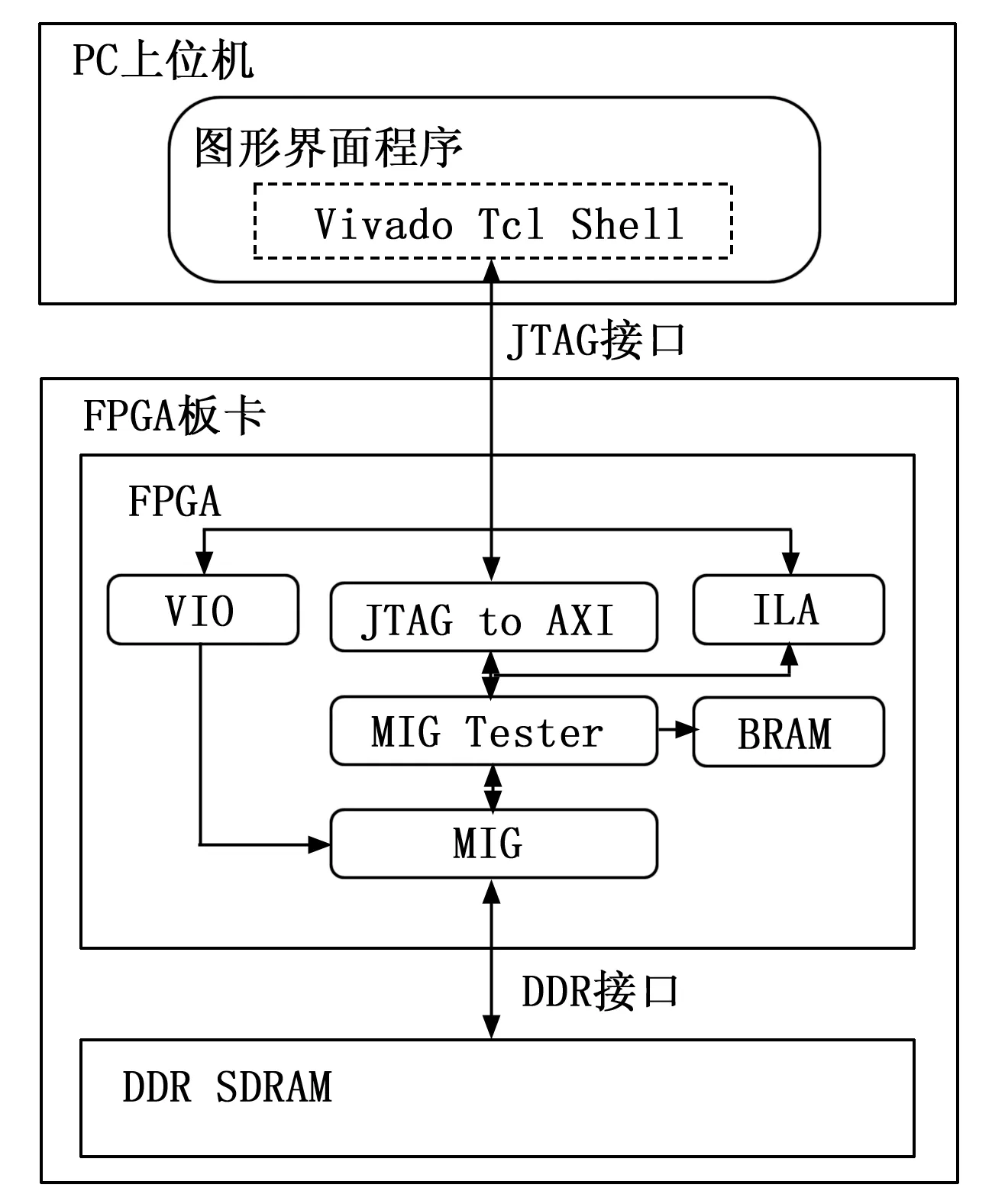

测试平台架构主要由两个部分构成:FPGA板卡与PC上位机。FPGA板卡内包含FPGA与DDR SDRAM,二者通过板卡上的DDR SDRAM接口相连接。PC上位机与FPGA通过JTAG接口实现通讯。用户在PC上位机操作图形界面程序,完成测试流程与输出测试结果[14-15]。所述架构如图1所示。

图1 测试平台架构框图

DDR SDRAM是待测的目标器件,由FPGA中的MIG控制。在对DDR SDRAM的测试中,重点关注的是DDR SDRAM的读写正确性与带宽两项性能[16]。

FPGA与DDR SDRAM通过DDR SDRAM接口相连接,FPGA内例化的MIG控制DDR SDRAM的初始化与数据读写。MIG Tester可以通过MIG的AXI slave接口对DDR SDRAM进行数据读写。MIG Tester的功能是测试读写正确性与带宽。MIG Tester有两个主要接口:一个是AXI slave接口,作为控制接口与JTAG to AXI相连,TCL脚本控制JTAG to AXI来与MIG Tester进行通信,控制测试流程与读回测试结果;另一个是AXI master接口,作为数据读写接口与MIG相连,测试过程中对MIG的数据传输均由此接口实现。此外MIG Tester还有一个块随机存取存储器(BRAM,block random access memory)主接口,用于向BRAM写入错误数据对应的地址信息,便于后续对错误数据的溯源分析。FPGA内例化的VIO、JTAG to AXI和ILA调试核互相配合下起到控制MIG初始化、控制MIG Tester、抓取AXI总线信号的作用,这些调试核均受PC上位机控制[17-18]。

PC上位机通过JTAG接口与FPGA进行通信。通过在PC上位机的VivadoTcl Shell程序中执行TCL脚本,可以对FPGA中调试核的信息读取与控制。图形界面程序将VivadoTcl Shell作为子进程运行,并将测试相关的TCL脚本封装为对应的按钮。操作人员可以通过图形界面程序便捷地控制整个测试流程,提高了测试效率,降低了学习门槛[19-20]。

2 FPGA工程设计

测试板卡使用的FPGA产自Xilinx公司,型号为xc7k325tffg900-2,使用的DDR SDRAM型号为MT8JTF2-5664HZ-1G6M1。

2.1 FPGA工程主要模块

工程主要包含JTAG to AXI、MIG Tester、AXI Smart-Connect、MIG、AXI Bram Controller等IP。模块之间主要通过AXI总线进行连接,所有AXI总线通过AXI SmartConnect互联IP连接在一起。地址空间分配中,MIG基地址被设为0x80000000,可被MIG Tester和JTAG to AXI访问。MIG Tester基地址设为0x44A00000,AXI BRAM Controller基地址设为0x00000000,两者都只能被JTAG to AXI访问。BRAM的类型为真双口BRAM,其中一个接口受AXI BRAM Controller控制,另一个接口供MIG Tester的BRAM主接口写入数据[21-22]。

2.2 Memory Interface Generator

MIG是由Xilinx官方提供的存储器接口成熟的解决方案,是可靠的DDR SDRAM控制器。MIG由一个控制器与DDR物理层接口组成。MIG将复杂的DDR物理接口封装为被广泛使用的AXI接口,简化了用户的设计。在FPGA工程设计中,MIG的AXI slave接口与MIG Tester的AXI master接口相连接,在测试过程中完成数据传输。MIG的复位信号控制着MIG初始化的开始,由VIO驱动。MIG的初始化完成信号是高电平时表示MIG完成了初始化,由VIO监听。

根据DDR SDRAM型号与具体电路,对MIG进行了如下配置:使能AXI接口,并设置数据位宽为512,以适配MIG Tester的AXI主接口;工作时钟频率设为800 MHz,参考时钟输入设为200 MHz,以适配板卡上的参考时钟晶振。

2.3 Memory Interface Generator Tester

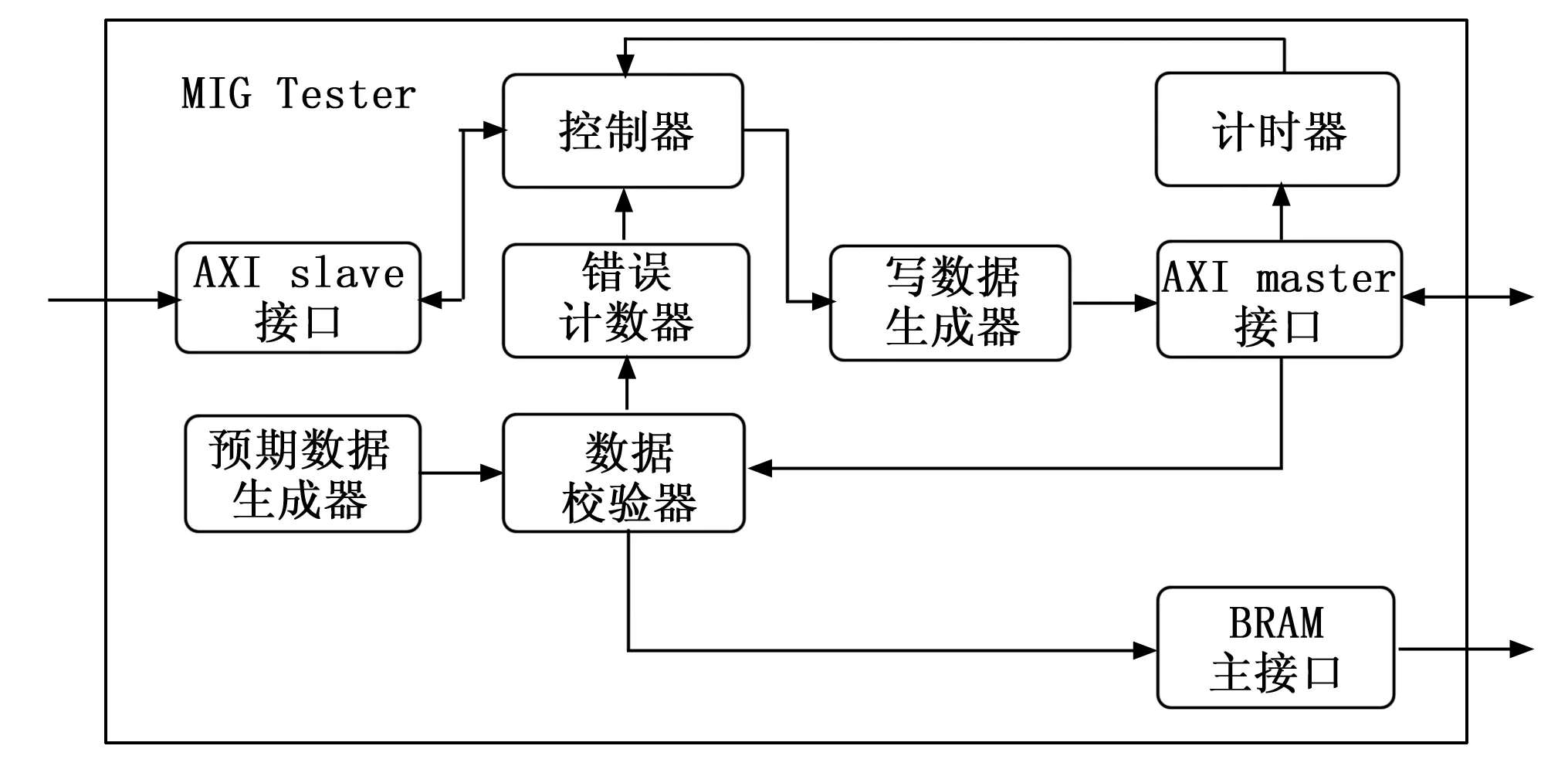

MIG Tester是自主设计的MIG专用测试IP核,主要包含以下模块:AXI slave接口、控制器、写数据生成器、AXI master接口、数据校验器、预期数据生成器、错误计数器、计时器与BRAM主接口。MIG Tester的框架如图2所示。

图2 MIG Tester框架图

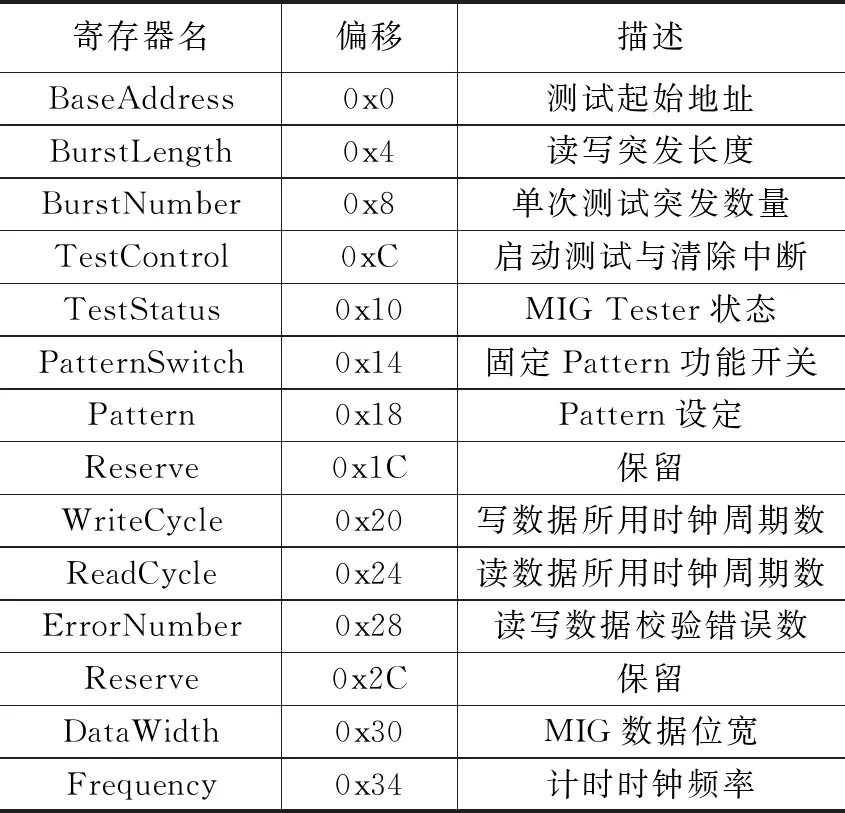

AXI slave接口是控制接口,通过AXI slave接口可以读写控制器中寄存器的值,各寄存器与地址的映射关系与详细描述如表1所示。

表1 AXI slave接口寄存器地址映射关系

AXI slave接口的寄存器位宽均为32位。其中偏移为0x0~0x18的寄存器是可读可写的,主要包括可配置的测试参数与测试控制。偏移为0x20~0x34的寄存器是只读的,主要包括测试结果以及固定测试参数。

写数据生成器在控制器的控制下,生成所设地址范围与所设pattern的写数据事务。DDR SDRAM测试的地址范围由测试起始地址、读写突发长度、单次测试突发数量与MIG数据位宽4个参数共同确定。公式如下:

(1)

Ahigh=Abase+Stest

(2)

式中,Stest是测试地址范围大小,Ahigh是测试终止地址,Abast是测试起始地址,Wdata是数据位宽,Lburst是突发长度,Nburst是突发数量。测试中写入DDR SDRAM的数据默认是8bit长的递增数pattern,当固定pattern开关被使能后,DDR SDRAM写入的pattern将和0x18地址寄存器内的数据保持一致。

AXI master接口是数据传输接口,与MIG的AXI slave接口相连接。写数据生成器生成的写数据事务和数据校验器生成的读数据事务均由此接口完成具体的数据传输。

数据校验器用于校验读回的数据与预期数据的一致性。当两者数据不相符时,错误标志信号error_flag置“1”,使错误计数器计数加一,并将错误数据对应的地址写入BRAM。

错误计数器接收数据校验器的错误标志信号进行计数。在完成测试后把错误计数写入ErrorNumber寄存器。每次开始测试时错误计数器清零。

计时器用于计算AXI总线读写数据所用时钟周期。在完成测试过程后计时器会将读写数据用时分别写入ReadCycle寄存器与WriteCycle寄存器。根据这两项测试结果以及计时时钟频率得出读写数据用时以及平均带宽。公式如下:

(3)

(4)

式中,Twrite是写数据实际所用时长,Cwrite是从寄存器中读取的写数据所用时钟周期数,Ftimer是计时器频率,Bwrite是写数据平均带宽。读数据所用时间和平均带宽的计算方式类似,不再赘述。

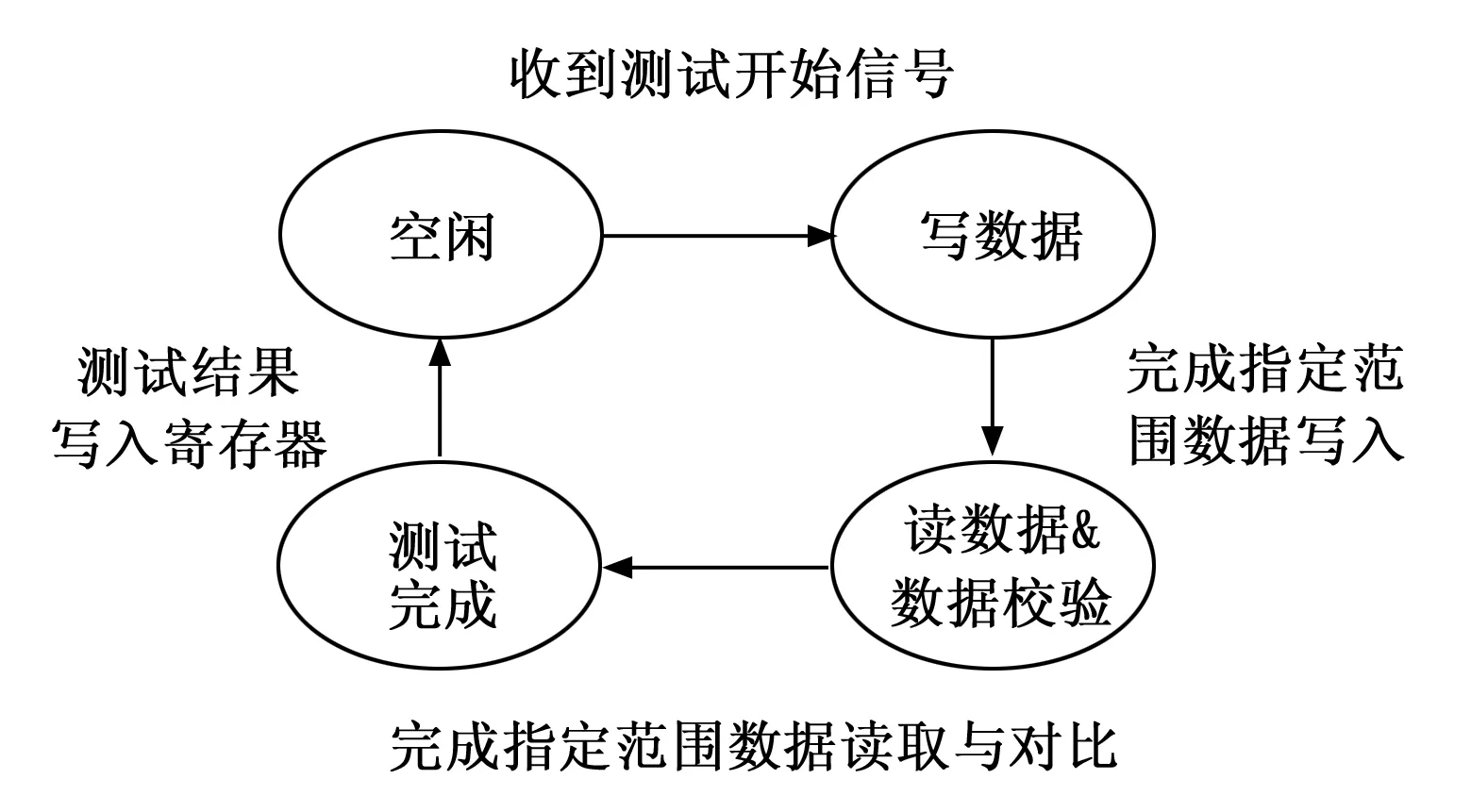

图3为MIG Tester控制器的状态机示意图。当TestControl寄存器的启动位被写入“1”时,处于空闲状态下的控制器进入写数据状态。AXI master接口开始对指定地址范围写入所设pattern。在完成指定地址范围的数据写入后,控制器进入读数据与数据校验状态。AXI master接口读取指定地址范围的数据并校验。在完成指定范围数据的读取与比较后,进入测试完成状态,测试结果被写入AXI slave接口的测试结果寄存器中,同时完成中断信号置“1”。测试结果写入完成后,控制器回到空闲状态。

图3 控制器状态机

2.4 Block Memory Generator

Block Memory Generator可以使用FPGA内的BRAM资源生成性能优秀的存储器,这类存储器一般就被称为BRAM。在设计中BRAM被设置为真双口模式,用于存储读写校验发生错误的错误数据对应的地址信息。

2.5 AXI BRAM Controller

AXI BRAM Controller提供了可供访问本地BRAM的AXI slave接口,支持突发事务,性能优秀。在设计中AXI BRAM Controller控制真双口BRAM的其中一个端口。JTAG to AXI可以通过此IP读取BRAM中的数据。

2.6 Virtual Input Output

VIO用于在线监测或驱动FPGA内部的信号。本设计中主要使用VIO驱动MIG的复位信号,以及监测MIG的初始化完成信号。VIO由PC上位机通过JTAG接口控制。

2.7 AXI to JTAG

AXI to JTAG用于生成AXI接口事务。本设计中主要使用AXI to JTAG控制MIG Tester,并读回测试结果。AXI to JTAG由PC上位机通过JTAG接口控制。

2.8 Integrated Logic Analyzer

ILA用于捕获FPGA内部信号。本设计中主要使用ILA捕获读写数据校验错误时MIG的AXI接口的数据,并通过TCL命令将数据保存至PC上位机。ILA由PC上位机通过JTAG接口控制。

2.9 AXI SmartConnect

AXI SmartConnect是由Xilinx官方提供的AXI总线互联IP,可以将一个或多个AXI内存映射主设备连接到一个或多个AXI内存映射从设备。本设计中主要使用AXI SmartConnect将各AXI设备互联。

3 PC上位机软件设计

PC上位机软件的设计主要包括TCL脚本设计与图形界面程序设计两个部分。

3.1 TCL脚本设计

TCL作为一门具有简明高效、便于移植的脚本语言,应用于众多EDA软件。Vivado软件在TCL语言的基础上增添了许多命令,以帮助开发者提高生产力。在本设计中,通过TCL脚本编程控制FPGA中的3个调试IP,配合完成初始化测试与读写测试两种测试功能。

3.1.1 VIO控制脚本

通过在Vivado软件中执行TCL脚本,PC上位机可以控制VIO的驱动值或读取VIO探针的电平。需要修改VIO输出探针驱动值时,使用set_property命令修改对应探针的OUTPUT_VALUE值,之后使用commit_hw_vio命令执行驱动值的修改。需要读取VIO输入探针电平时,使用refresh_hw_vio命令刷新VIO输入探针的电平,然后使用get_property命令获取对应探针的INPUT_VALUE数值。

3.1.2 AXI to JTAG控制脚本

PC上位机可以通过执行TCL脚本来控制AXI to JTAG发起AXI总线读写事务,从而访问目标设备。当需要对AXI设备进行读操作时,使用create_hw_axi_txn命令创建读数据事务,执行run_hw_axi命令运行该事务。随后使用report_hw_axi_txn命令报告读取数据。在完成传输数据事务后,使用delete_hw_axi_txn命令删除该事务。写AXI设备数据的过程与读数据过程类似,区别在于生成写事务时需要指定事务类型为写,并增加一个写入数据作为参数。

3.1.3 ILA控制脚本

TCL脚本可以控制ILA执行信号抓取任务,并将抓取的数据展示或保存下来。需要通过ILA抓取特定信号时,首先使用set_property命令修改需要抓取的信号以及触发方式,然后使用run_hw_ila命令开始执行抓取信号。抓取到信号后,使用upload_hw_ila_data命令更新数据,并用write_hw_ila_data命令将抓取到的信号数据保存为ila文件和csv文件,便于后续进行分析。

3.1.4 初始化测试脚本

初始化测试的原理是,对MIG重复进行复位与初始化,记录该过程中MIG是否能在限定时间内完成初始化。

TCL脚本编程的DDR SDRAM初始化测试流程如图4所示。在开始DDR SDRAM初始化测试后,首先控制VIO驱动MIG复位信号mig_rst_n为0,以确保MIG处于复位状态。之后控制VIO驱动MIG复位信号mig_rst_n为1,MIG开始一次初始化过程。之后VIO监测的init_complete信号的值,如果在指定时间内检测到高电平,则视为初始化成功,反之则视为初始化失败。完成测试结果记录后,判断已测试次数是否已达到指定的测试次数,如果已满足则输出测试结果,反之则返回第一步继续进行测试。

3.1.5 读写测试脚本

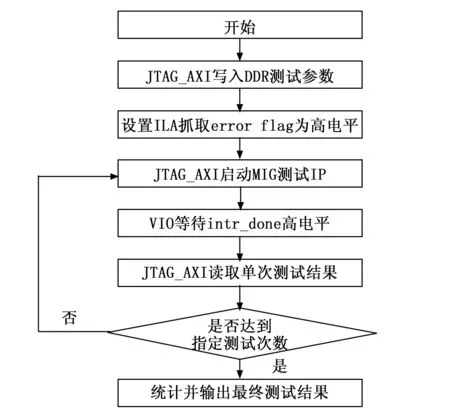

读写测试的原理是,将测试参数写入MIG Tester,控制MIG Tester开始读写测试,并将每次测试结果进行记录与统计。

TCL脚本控制的读写测试流程如图5所示。首先控制JTAG to AXI向MIG Tester写入读写测试的起止地址、写操作的pattern与读写的突发数等测试参数。随后设置ILA的触发信号为错误标志信号error_flag信号的高电平。写TestControl寄存器启动MIG Tester。通过VIO监控测试完成信号intr_done直到它变为高电平。至此一次测试完成,由JTAG to AXI读出测试结果并保存。随后判断测试次数是否以达到目标,若已达到则统计所有测试结果并输出,反之则再次启动测试。

图5 读写测试流程图

3.2 图形界面程序设计

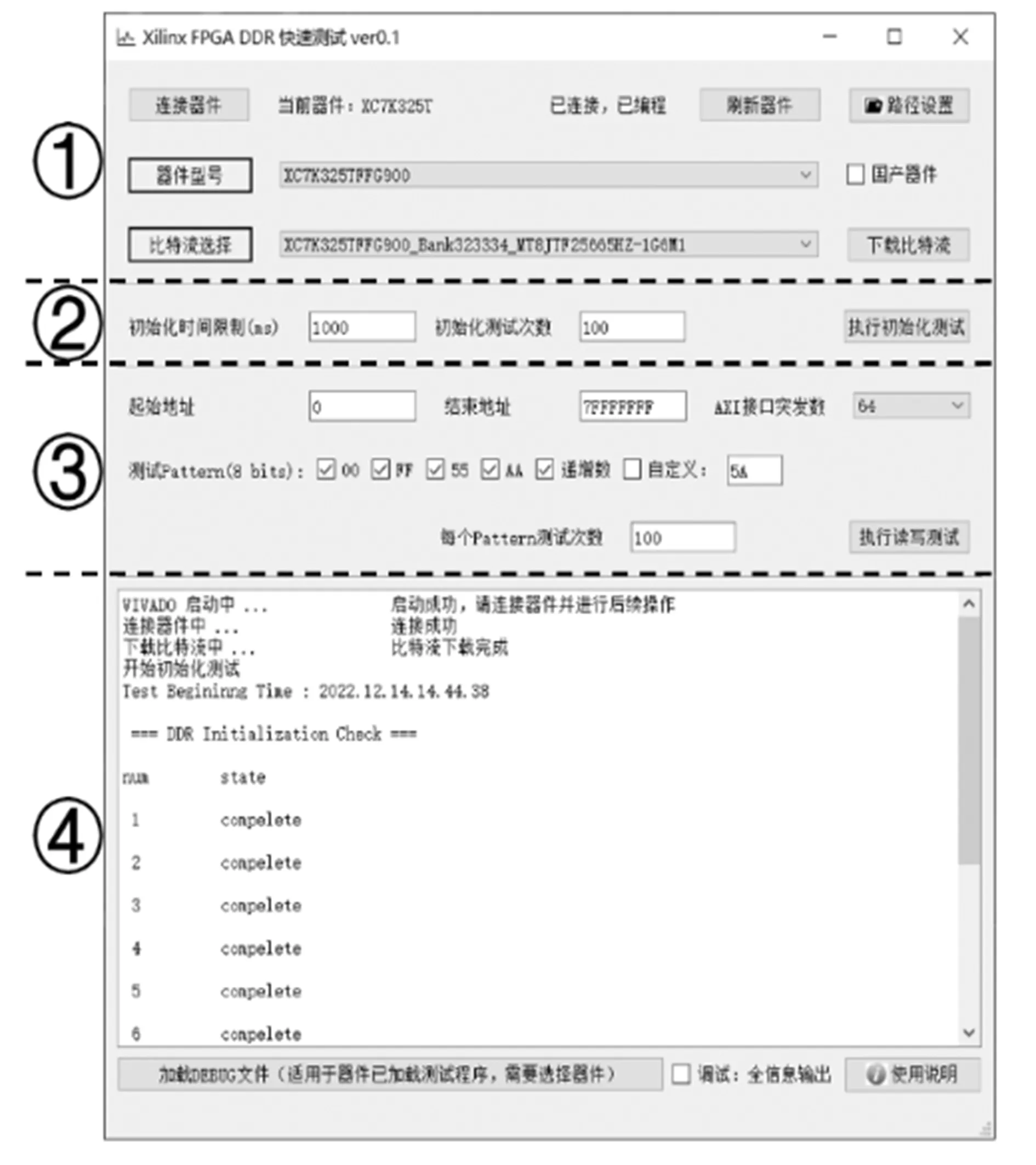

图形界面程序在PyQt5框架下进行开发。PyQt5衍生自C++的QT库,具有能够跨平台兼容多种环境,功能强大,开源免费等优势。图形界面程序通过创建子进程的方式运行命令行程序,并在命令行程序中打开TCL模式的Vivado。点击程序中的功能按钮即可执行对应的Vivado指令或者TCL脚本。图形界面程序的界面如图6所示,主要功能包括:

图6 应用程序界面

1)人机交互:操作人员可以根据测试需求,在图形界面程序中调整测试参数、执行测试任务和读取测试信息。

2)器件控制:程序可以通过JTAG接口完成连接FPGA器件、状态检测、下载比特流、控制调试核等操作。

3)统计结果:程序自动重复并统计测试结果,在测试循环完成后输出测试统计报告并保存为日志文件。

程序界面主要分为4个区域。区域1主要包括连接器件以及下载比特流文件功能。区域2包括初始化测试的参数设置与执行。区域3包括读写测试的参数设置与执行。区域4是一个文本框,输出文本信息。

首先需要在区域1中完成器件的连接与比特流文件的下载。程序启动后将自动运行Vivado子进程,并在文本框处提示“Vivado启动中”。待Vivado启动完成,文本框处打印“启动完成”信息,“连接器件”按钮变为可用。点击“连接器件”,Vivado进程将打开硬件管理器,并尝试连接FPGA器件。如果未检测到FPGA器件,则打印“连接失败”信息,如果检测到FPGA器件,则在“当前器件”标签处显示检测到的器件型号、连接状态与编程状态。“器件型号”下拉选项和“比特流选择”下拉选项会自动筛选出符合当前器件的选项。用户需要在这一步自行选择适用的比特流文件并点击“下载比特流”按钮。等待文本框提示“比特流下载完成”,即可在区域2或区域3中执行后续测试。

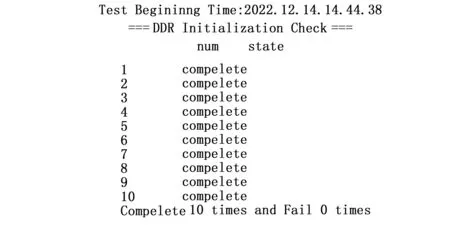

区域2中,初始化时间限制即是TCL脚本中判定初始化是否成功的界限,初始化测试次数是本次执行初始化测试的总测试数。执行测试后,测试结果打印在文本框中,并在完成一轮测试后生成日志文件。日志文件内容如图7所示,日志内容包括:测试日期、测试项目名、测试序号、初始化测试结果以及完成本轮次的测试后的统计数据。

图7 初始化测试结果输出

区域3中,软件将根据设置的起始地址、结束地址以及AXI总线突发数量等参数,计算出对应的配置参数,并写入到MIG Tester的配置寄存器中。可以勾选下方的测试pattern复选框来选定本次测试需要测试的pattern。勾选了自定义pattern的情况下需要将自定义的pattern填入后方的文本框内。设置好pattern测试次数后点击“执行读写测试”按钮,软件将依次执行每个选定pattern的测试。测试结果将打印在下方的文本框中,并在一轮测试完成后将生成日志文件。日志文件内容如图8所示,输出的内容包括:测试日期、测试项目名、测试序号、读写平均带宽、错误数据数量以及本轮次的测试的统计数据。

图8 读写测试结果输出

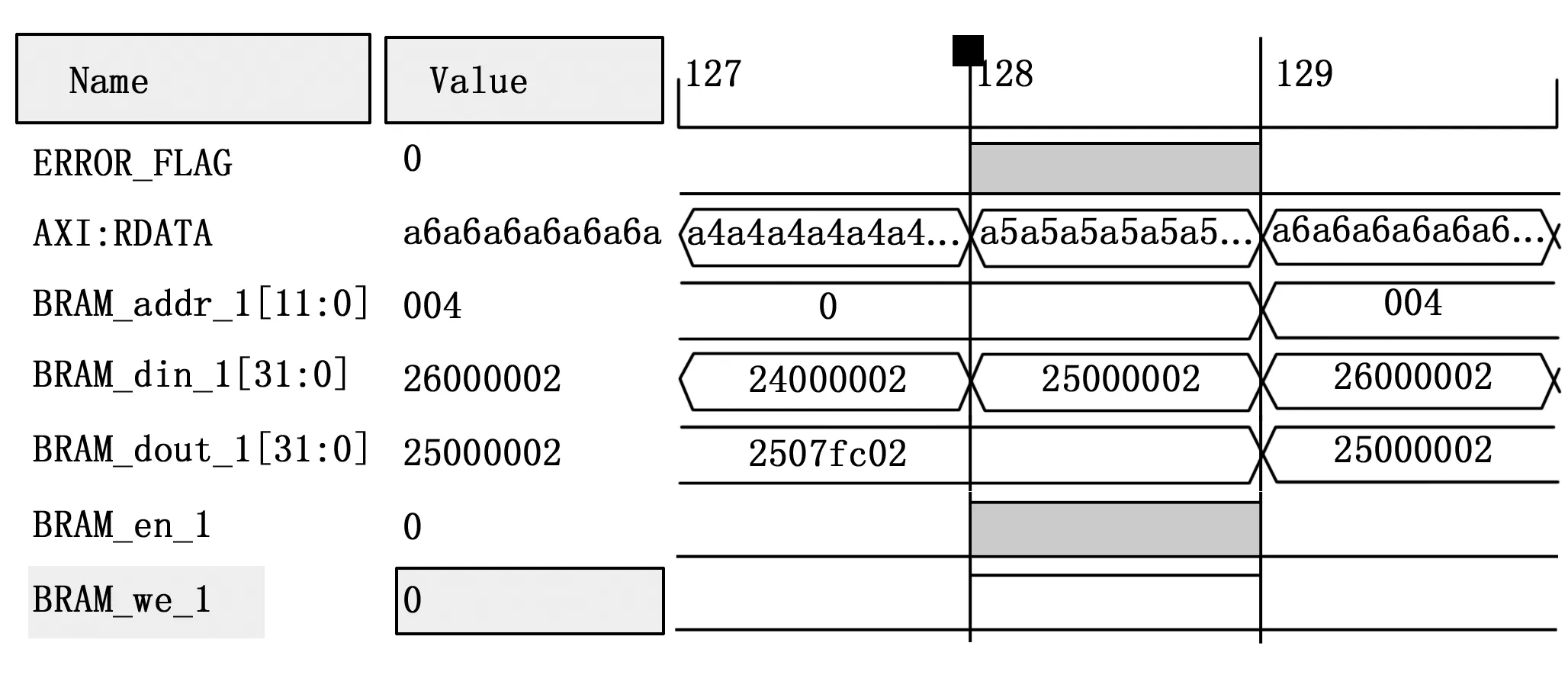

如果在读写测试过程中发生了读数据与预期数据不符的情况,ILA将抓取错误发生时AXI总线上的信号并保存到硬盘上。在需要分析信号时,可以在Vivado程序中使用read_hw_ila_data命令读取数据,并用display_hw_ila_data命令绘制信号波形图。如图9所示,图中标记的部分error_flag信号为“1”,表示该位置出现了读写错误。

图9 数据错误发生时的信号波形图

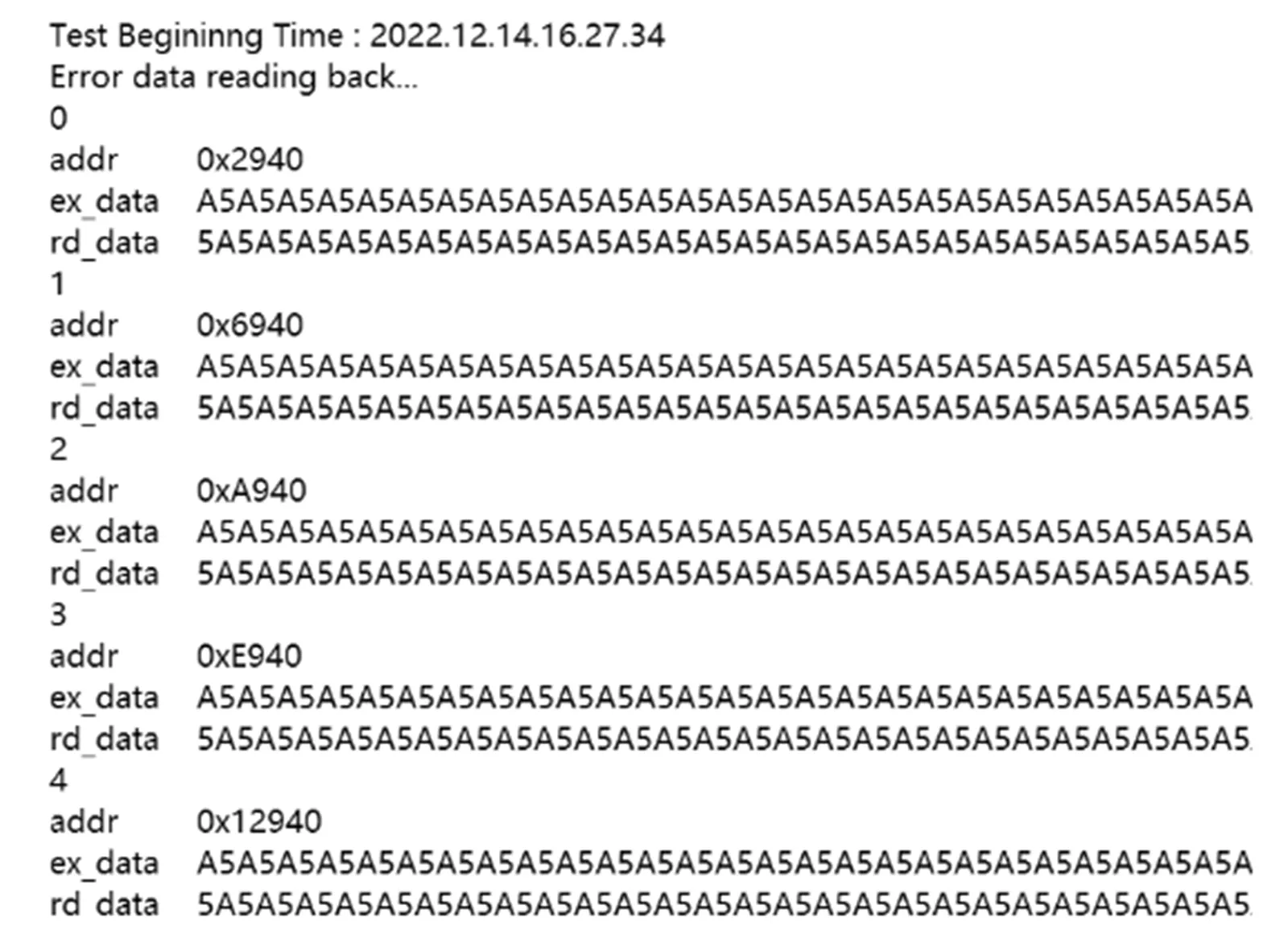

同时BRAM接口写使能,将错误数据对应的地址信息写入BRAM中。程序可以通过JTAG to AXI访问MIG中这些地址并读回数据,从而生成错误数据列表。如图10所示,addr是错误数据对应的地址。ex_data是期望数据,也就是读写功能正常情况下应读回的数据。rd_data则是实际读回的数据。操作人员可以根据该报告分析可能存在的问题。

图10 错误数据记录文件

4 实验结果与分析

4.1 MIG Tester功能验证

使用Vivado软件的仿真功能对MIG Tester进行功能验证。配置AXI Verification IP为从模式,连接至MIG Tester的AXI master接口,在仿真中关注AXI总线的读写事务以及相关信号的变化。

在单次读写测试中,AXI总线上先后发生的写事务与读事务。为了缩短仿真时间,测试的地址范围设置为0x0~0x63FFF。在通过控制接口启动测试后,MIG Tester先对整个测试地址范围顺序写入一次pattern,然后进入读取数据状态,并将读取的数据与预期数据进行校验。完成整个过程后,完成中断信号将被置“1”。

在AXI总线的写通道中,写地址awaddr在每次握手写入后增加突发传输所占的地址大小,实现对测试地址范围内所有地址的写入。当设置的pattern是递增数时,写数据wdata每写入一次数据后递增1。写突发结束计数器wlast_counter在wlast信号置位时计数加一,用于控制数据的突发传输。write_timer信号是写状态计时器,从测试进入写pattern过程开始计时,直到进入读数据状态停止计时。

在AXI总线的读通道中,读地址araddr在每次握手写入后增加突发传输所占的地址大小,实现对测试地址范围内所有地址的读取。读数据rdata是读回的数据。当设置的pattern是递增数,预期数据expected_data每写入一次数据后发生递增。错误标志信号error_flag的特征是在预期数据与读取数据rdata不同时置1,由于读取过程中预期数据与读取数据相符,所以错误标志保持为0。读突发结束计数器rlast_conter在每次rlast信号置位时计数加一,用于控制状态机的转换。read_timer是读状态计时器,从状态机进入读数据状态开始计时,直到进入测试完成状态停止计时。

然后人为插入错误数据验证数据校验模块功能是否正常。插入错误数据的方式如下:选择pattern为递增数,并且当写入数据为A5时,将其替换为5A。在读数据时,读回数据rdata为5A,与其对应的预期数据A5不符合,所以错误标志信号error_flag置“1”,且错误计数器加一。证明数据校验功能正常。

经过上述功能验证,可以确认测试IP核MIG Tester逻辑功能符合预期,可以将其用于DDR SDRAM的测试。

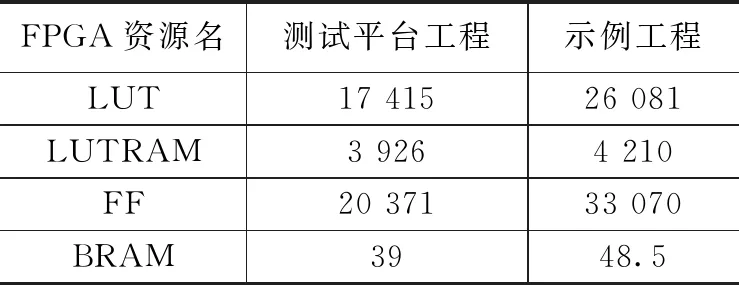

4.2 FPGA资源使用对比

FPGA测试平台工程设计完毕后,在软件Vivado2020.2默认设置下执行生成比特文件。作为对比,打开MIG的示例工程并生成比特文件。MIG的示例工程常作为DDR SDRAM的测试调试工程使用。对比测试平台工程与示例工程的资源使用数量,结果如表2所示。测试平台工程资源使用量对比示例工程显著减少。其中作为FPGA主要资源的查找表(LUT,look-up-table)的使用减少了33.22%,触发器(FF,Flip Flop)的使用减少了38.40%。

表2 FPGA资源使用数量对比

4.3 FPGA板卡测试

测试板卡使用的FPGA产自Xilinx公司,型号为xc7k325tffg900-2,使用的DDR SDRAM型号为MT8JTF2-5664HZ-1G6M1。

4.3.1 测试流程

DDR SDRAM测试基本流程如下:

1)设计FPGA工程,生成比特流文件与ltx文件(调试核信息文件),并拷贝到图形界面程序目录下的bitstream文件夹中。

2)使用仿真器将FPGA板卡连接至PC上位机并上电。打开图形界面程序,待启动完成后点击“连接器件”,等待连接完成,标签栏处出现FPGA器件名称与状态。

3)选择与FPGA对应的比特流,点击“下载比特流”,等待比特流下载完成,标签栏处显示“已连接,已编程”。

4)在文本框中设置测试参数,根据测试需求执行相应的测试。在测试完成后,将在程序目录下生成测试结果报告。

4.3.2 初始化测试

根据赛灵思官方手册提供的数据,设置初始化时间限制为1 000 ms。执行100次初始化测试。初始化测试结果如表3所示。在100次初始化测试中,DDR SDRAM的初始化均在1 000 ms以内完成。结果说明,测试板卡中的DDR SDRAM能够正常初始化。

表3 初始化测试结果

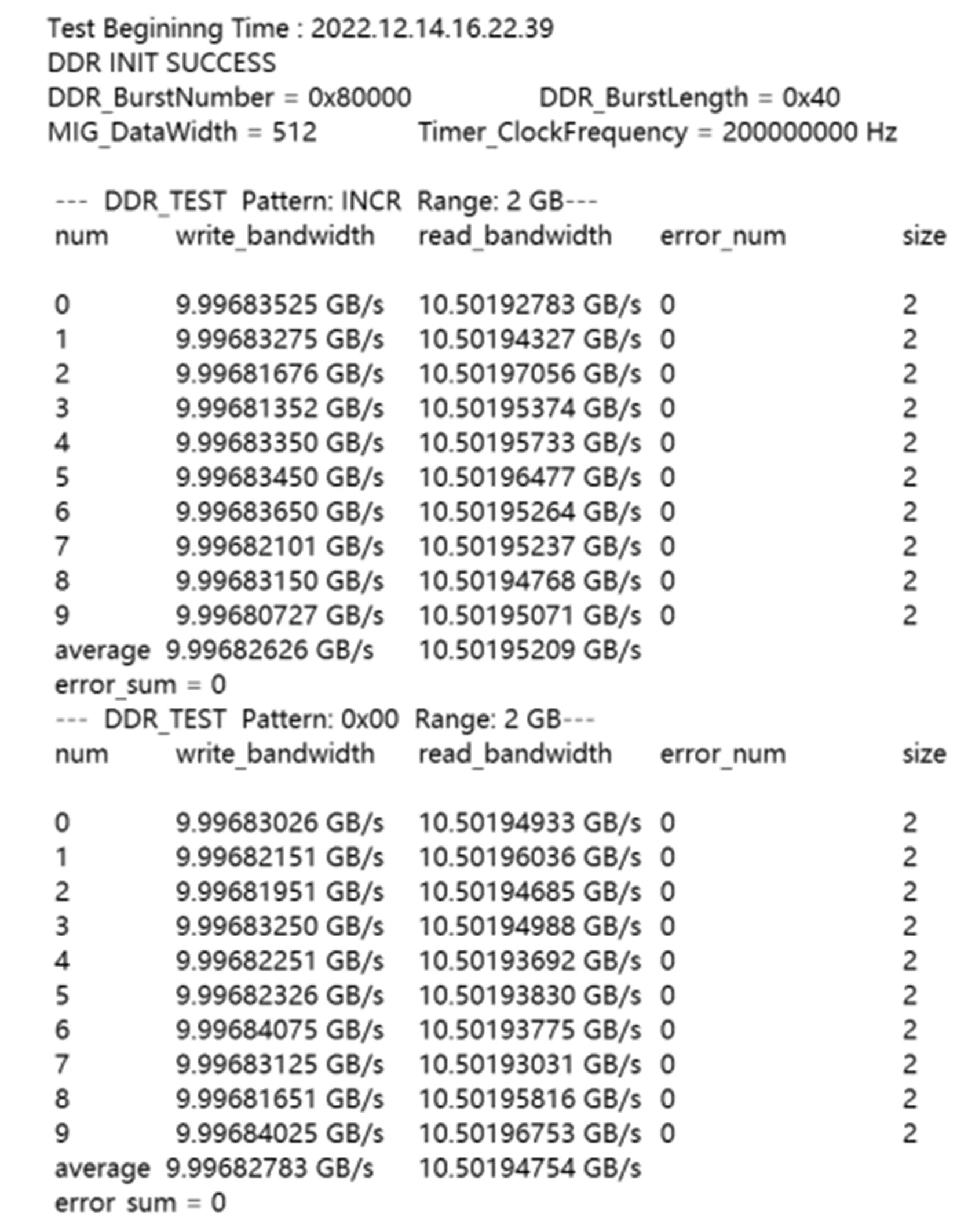

4.3.3 读写测试

设置读写测试起始地址为0,结束地址为0x7FFFF-FFF,即测试整个2 GB的地址空间。设置AXI总线突发数为64,测试Pattern栏目中勾选递增数00、FF、55、AA,每个pattern测试100次。数据读写测试测试结果如表4所示。写平均带宽和读平均带宽分别达到了理论带宽的83.9%和88.1%,且没有出现过读写数据校验错误。证明了在测试环境下DDR SDRAM读写数据功能正常,带宽性能良好。

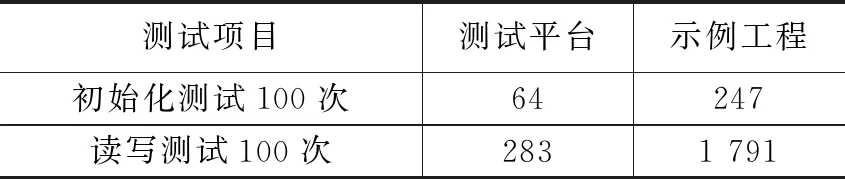

4.3.4 测试时长对比

表5是两类测试的测试平均时长对比。对于初始化测试,示例工程的测试方法如下:操作人员使用Vivado软件的硬件管理器控制VIO输出的复位信号失效,之后通过VIO观察MIG输出的初始化完成信号是否置“1”,据此判断MIG是否完成了初始化。在此过程中,操作人员需要不断重复上述过程。一方面存在操作人员操作或记录失误的可能性;另一方面手动操作效率低下,且无法准确判断初始化所用时长。对于读写测试,选用测试00、FF、55、AA与递增数物种pattern的情况进行对比。示例工程的测试方法如下:操作人员使用Vivado软件的硬件管理器控制VIO完成DDR SDRAM的初始化、设置读写地址与数据。同时设置ILA抓取数据校验错误信号为“1”时的波形。观察VIO中读写数量计数器,据此判断是否完成了整个地址空间的读写。

表5 测试时长对比sec s

由测试结果可见,在DDR SDRAM功能正常的情况下,使用测试平台测试DDR SDRAM功能所用时长要比使用示例工程缩短70%以上。

在读写测试期间发生了数据错误的情况下,测试平台的优势将进一步体现。测试平台会将完整的错误数据地址信息写入BRAM中。在单次测试结束后根据地址信息读回对应错误数据,生成完整的错误数据列表,对测试时长的影响也不明显。而使用示例工程测试时,只能通过ILA抓取错误数据发生时的波形。这种方式无法暂停数据读写测试,所以无法保证抓取的错误数据完整性。另一方面ILA需要操作人员手动抓取波形,增加了测试时长。

4.3.5 测试结论

相比以往的DDR SDRAM测试方案,本测试平台具有如下优势:

1)测试参数可配置。操作人员可以根据不同的测试需求设置相应的测试参数而无需重新生成比特流,节省准备时间。

2)自动执行测试流程并输出报告。程序将按照参数设置自动循环执行测试任务,并在测试任务完成后输出相应的测试日志与报告文件。在测试任务繁重时可以提高测试效率。

3)辅助错误分析。当数据读写出现错误时,程序将记录错误数据对应的地址信息,在当次测试结束后从对应地址读回错误数据并记录于测试日志中,给错误分析与设备调试提供便利。

4)使用FPGA资源降低。对于实验所用FPGA板卡,对比MIG的示例调试工程,本设计使用的查找表资源由26 081降低至17 415,所用触发器资源由33 070降低至20 371,这些主要资源的使用下降了30%以上。在长时间测试中FPGA器件的功耗更低,散热压力更小。

5)操作简单,学习门槛低。经图形界面程序封装之后,操作人员无需耗费精力学习其相关软硬件知识,仅需通过简单的设置参数与点击按钮即可完成测试过程。经过实践,使用测试平台的测试用时缩短了70%以上。

5 结束语

提出了一种基于FPGA的灵活度高、操作简易的DDR SDRAM测试平台。测试平台由FPGA板卡与PC上位机两个主要部分组成。经验证,测试平台能够正确测试DDR SDRAM的初始化过程、读写正确性与带宽等性能并自动生成测试报告。该测试平台规避了传统测试方法操作繁琐,耗时长,学习成本高等弊端。但在测试前仍需要设计相应的FPGA工程并生成比特流。如果在FPGA板卡设计之初能够复用FPGA中DDR SDRAM的管脚分配,即可避免重新生成比特流,该方案的便捷性将进一步提升。

测试平台仅对DDR SDRAM进行了测试,但该架构同样适用于其他可通过AXI总线访问的外部存储设备的测试,具有拓展应用范围的潜力。