TFT基板低功耗显示驱动方法研究

苗宗成, 张瑞寅, 贺泽民, 梁蓬霞

(1.西京学院 电子信息学院, 材料与能源科学技术研究院, 陕西 西安 710123;2.西北工业大学 光电与智能研究院, 陕西 西安 710072;3.京东方科技集团股份有限公司, 北京 100176)

1 引言

薄膜晶体管(Thin Film Transistor, TFT)低功耗驱动在移动设备和便携式电子产品中十分重要[1]。这些设备通常由电池供电,TFT驱动功耗越低,电池寿命就越长,意味着用户可以更长时间地使用设备、节省能源从而降低能源成本,并且可减少对环境的负面影响[2]。因此,TFT低功耗驱动的重要性不仅体现在个人便携式电子产品的使用中,也与整个社会和环境的可持续性息息相关。

在目前屏幕显示市场中,因TFT-LCD具有重量轻、薄、技术成熟、可靠性高、成本低等特点,一直占据显示技术的主导地位,并广泛应用于显示器、笔记本、PAD等电子显示产品中[3],从小型移动电子设备到大型显示器和数字电视都有它的身影。“甘瓜苦蒂,天下物无全美”,TFT-LCD虽然有着诸多的优点,但其也有缺点,如成本较高和耗电量相对较大。这些问题对未来便携设备的进一步发展非常不利[4]。随着近年来绿色环保性逐渐成为新的发展标准,产品低功耗的技术需求也越来越高,低功耗需求已成为产品的重要竞争力。为进一步降低TFT-LCD显示设备功耗,提升设备的续航水平,推动未来便携设备的进一步发展,近年来,学术界针对TFT基板低功耗的研究已经提出了很多应对方法,主要分为两种:一是在TFT基板结构上进行优化;二是对TFT基板的软硬件外设驱动进行优化。本文阐述了TFT-LCD低功耗技术及其应用背景,对其中的关键技术进行了分析与研究,总结了当前TFTLCD低功耗发展现状,并展望未来的TFT-LCD低功耗发展将会在新材料和技术、像素控制电路设计与新的集成电路技术、系统算法优化技术4方面实现突破。

2 TFT基板区域的优化

TFT基板作为显示器的主要用电设备,其耗电对其构成的显示设备功耗有很大的影响。TFT基板区域的功耗主要受到信号转换功耗、TFT负载(像素电容)半导体本身性能3方面的影响,因此对TFT基板进行优化从而达到低功耗的目的是非常有必要的。针对上述的几种影响TFT基板功耗的问题,有以下几种优化方法:实现静态随机储存器(Static random access memory,SRAM)嵌入像素控制电路阵列技术[5]、优化双速率驱动(Dual-rate driving, DRD)技术[6]、优化非晶铟-镓-锌氧化物(Amorphous indium-gallium-zinc oxide, a-IGZO)新型半导体的TFT阵列技术[7]等。根据这些技术设计出一种改进的驱动方案以实现TFT基板低功耗的目标。

2.1 优化SRAM模式的低功耗设计

在TFT基板工作中,信号转换操作通常需要使用一定的功率,因此对TFT基板的低功耗性能会产生影响。信号转换器在运行时,需要消耗一定的电力来执行转换、放大、缩放等处理操作,这可能导致电流的增加和功耗的提高。合理地处理信号转换,可以减少TFT基板的功耗。

传统TFT-LCD数字驱动电路通常采用脉宽调制(Pulse-width modulation,PWM)来表示n位数字输入。PWM可以分为两类:多脉冲PWM(Multiple-pulse,MP-PWM)和单脉冲PWM(Singlepulse,SP-PWM)。MP-PWM的典型代表是二进制编码的PWM(Binary-Coded,B-PWM),SP-PWM的典型代表是温度编码的PWM(Thermometer-Coded,TH-PWM)。与B-PWM相比,TH-PWM的输入、输出灰度特性十分稳定,显示效果较好[8]。但是由于TH-PWM在实际显示驱动电路中,会造成行-行扫描和列-行信号过渡次数的增加,一帧时间内增加的子帧数使得功耗大幅增加,并且随着像素驱动电压的增高,这种情况会变得更加严重。

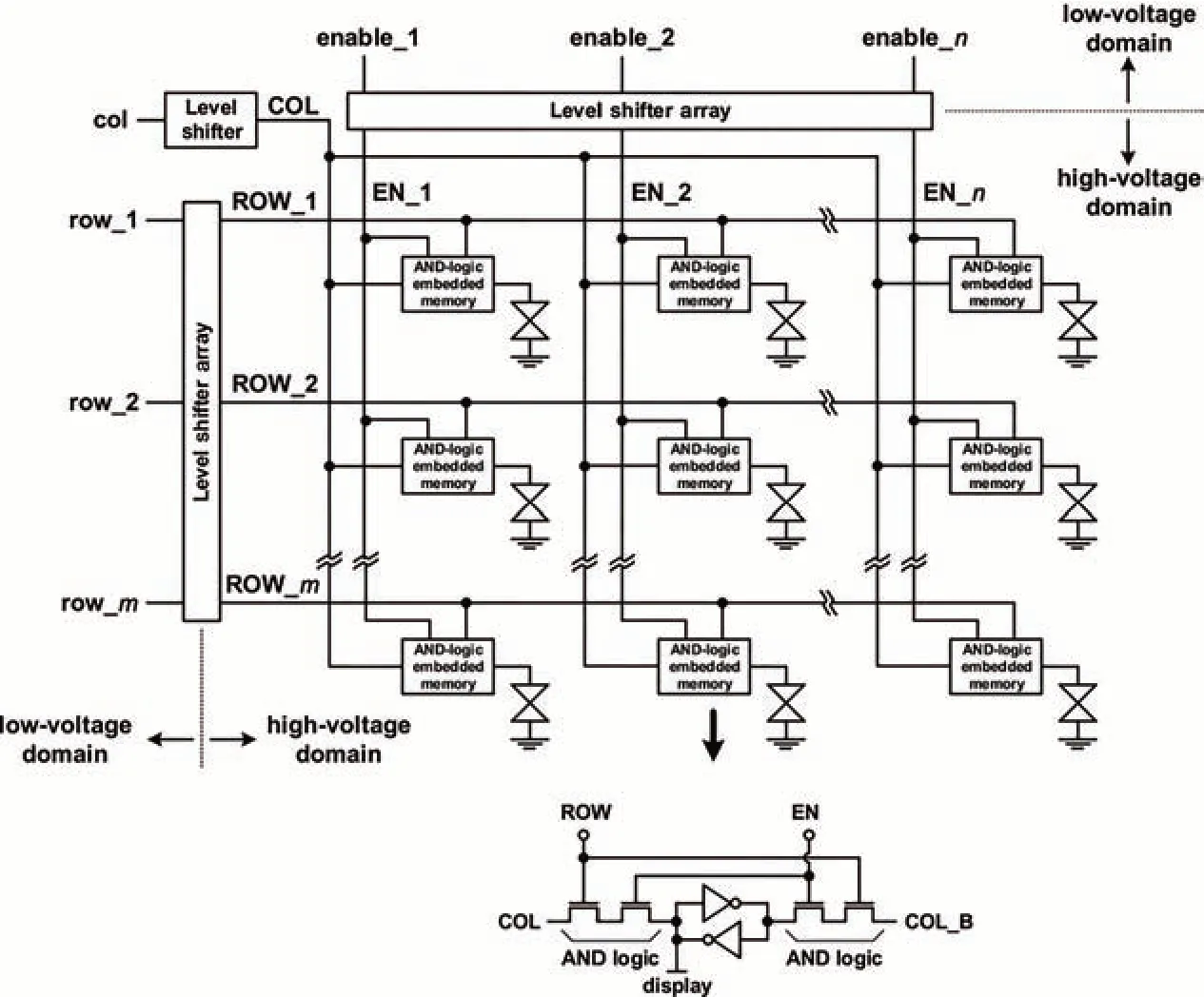

传统的数字像素阵列如图1所示。由于连接到像素阵列的行线和列线所需的电压高于产生这些信号的时序电路的电压,因此行线和列线需要使用电平移频器。每个像素存储器由一对背对背的数据存储逆变器和两个数据写入开关组成,如图1虚线框所示。随着行-行扫描的进行,列-行信号也随之改变以更新像素存储器中的值。每当像素的行信号为高时,列行驱动就向像素内存写入0或1。由于传统的平行列线相互独立运行,列行信号转换的数量与像素数据变化的幅度成正比,这意味着能耗的增加。

图1 传统数字像素阵列电路效果图[9]Fig.1 Traditional digital pixel array circuit renderings[9]

为在保持图像质量的同时解决高能耗问题,Je-Kwang Cho提出了一种数字像素驱动方法。驱动方案的像素阵列和电路如图2所示,与图1的主要不同之处是在电路阵列中嵌入了与门逻辑电路,以及添加了一个电平移位器,减少了列线信号过渡(Number of column-line signal transitions,NoCTR)的数量,进而减少了列线驱动器的功耗。

图2 数字像素阵列电路效果图[9]Fig.2 Digital pixel array circuit rendering[9]

在提出的新型驱动电路中使用TH-PWM时,像素存贮值不需要每次行-行访问都更新。这是因为生成TH-PWM波形所需的所有信息只是波形下降边缘的瞬间,每当输入值不为0时,它就会在帧时间开始时上升。例如,当3位输入值为4时,上升沿只需要在时间为0时更新像素内存,下降沿只需要在时间为4时更新像素内存。列线驱动器不需要重写SRAM像素存储器[9]。从而可以推导出,列线信号仅在时间为0才需要变高,并且在所有其他定时瞬间保持低电平,只需要有一个使能信号,决定何时以及是否需要将像素存储器值更新为列线值。

图3给出了使用所提出的驱动方法针对不同输入值产生3位TH-PWM波形的COL和使能信号波形效果。COL在整个帧时间内仅改变2次,大幅减少了列行信号转换的数量,并且使能信号只有在适当的定时瞬间才会变高。因为列行信号依赖于计时瞬间,其为每一列行分配一个使能信号,可以控制嵌入在每个像素中的AND逻辑。因此,列行信号转换的数量的变化不依赖于像素值的变化,极大弥补了TH-PWM的缺点,使其在数字驱动电路中达到了低功耗的目的[9]。

2.2 优化DRD模式的低功耗设计

当驱动器驱动TFT负载时,TFT负载的像素电容充放电所需的能量是耗费在TFT基板上的主要功耗之一。在TFT基板的设计中,合理地管理TFT负载的像素电容的充放电过程可以实现功耗最小化。

双速率驱动(Dual-rate driving, DRD)模式是为了在保持高分辨率的同时减少数据驱动器IC的数量而开发的一种驱动模式,其原理是使原本一条驱动线对应一个子像素变为一条驱动线对应多个子像素,这样可以减少电视面板的显示驱动芯片数量,一颗源驱动IC可以代替两颗源驱动IC进行工作,将驱动速度提升了一倍[10]。此方法又被称为双速率驱动。但此方法会将数据驱动器IC的输出电流增加,如果要保持图像的质量,将会导致功率消耗增加[11],不符合低功耗驱动要求。为了克服这个问题,Do-Sung Kim将DRD与低功耗数据寻址技术相结合,达到低成本、低功耗的目的。

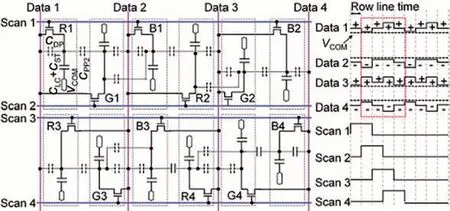

在大多数TFT-LCD上,面板的亮度主要受绿色子像素的影响[12]。因此,在给定的像素电压变化下,绿色子像素比其他两个彩色子像素更严重地影响亮度均匀性。Do-Sung Kim所提出的寻址技术与传统的数据寻址技术不同,该技术在对相邻子像素充电之后,再对所有绿色子像素进行充电,同时减小了相邻像素之间的寄生电容引起的像素电压变化,如图4所示。因此,绿色子像素电压的变化被最小化,并且由此显著地改善了亮度均匀性。

Do-Sung Kim通过使用数据寻址技术优化了子像素的充电序列,减少了由寄生电容引起的像素电压变化[13]。图5展示了所提出技术的像素阵列原理图以及在测试时的数据和扫描信号的时序图。测试信号采用每隔4行/行时重复数据信号一次,然后生成测试图,将数据电压设置为0灰、127灰、255灰3个级别。正、负数据电压分别为灰色级0的6.680 V和5.780 V,灰色级127的8.630 V和3.410 V,灰色级255的11.270 V和0.560 V。根据回推电压确定了5.650 V的通用电压(VCOM)。效果如图5所示,数据信号的极性在一帧时间内没有改变,即CDP的干扰没有得到补偿从而减小相同子颜色像素之间的亮度差异,提高图像质量,达到低功耗[12]。

图5 显示测试图形的数据和扫描信号的像素阵列示意图和时序图[12]Fig.5 Pixel array schematics and timing diagrams of data and scan signals for displaying test pattern using proposed technique[12]

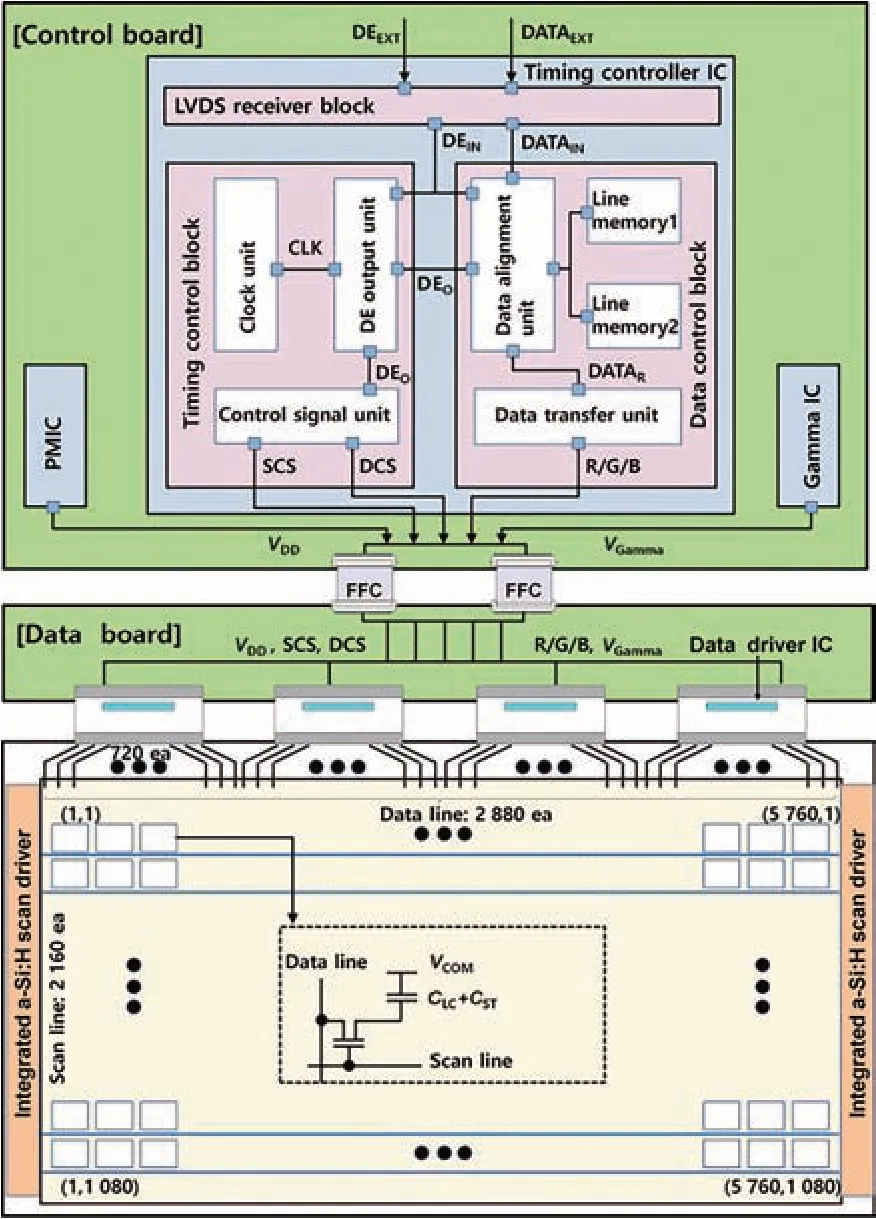

图6给出了用于验证所提出的数据寻址技术的测试板的框图。该测试板由控制板、数据板、4个源极驱动器IC和一个17 in(1 in=2.54 cm)8位全高清边缘场开关模式TFT-LCD面板组成。控制板包含定时控制器IC、电源管理IC和伽马IC。定时控制器IC由低压差分信号(LVDS)接收机模块、定时控制模块和数据控制模块组成。LVDS接收块从外部驱动系统接收外部视频数据(DATAEXT)和外部数据使能信号(DEEXT),并将内部视频数据(DATAIN)和内部数据使能信号(DEIN)发送到数据控制块和定时控制块。与传统的FHD面板相比,DRD将TFT-LCD面板的数据线数减少1/2至2 880条,扫描线数增加一倍至2 160条。

图6 测试板框图[11]Fig.6 Block diagram of test board[11]

在控制板中,两行/行时的数据经DEIN存储在行存储器1(LM1)和行存储器2(LM2)中。数据对准单元交替地读取存储在LM1和LM2中的数据,并通过数据使能信号(DEO)产生用于4行线的重排视频数据(DATAR),该信号的频率比DEIN增加了一倍。DEO由CLK和DE输出单元中的寄存器产生,DATAR被传送到数据传输单元,数据传输单元将DATAR转换成RGB数据包,并将RGB数据包传送到数据驱动IC。利用DEO,定时中的控制信号单元控制块分别为数据驱动器IC和扫描驱动器IC生成数据控制信号(DCSs)和扫描控制信号(SCSs)。DCSs包括数据开始信号、数据移位时钟和数据使能信号,而SCSs包括扫描开始信号和扫描复位信号。数据驱动器IC(VDD)的13 V电源电压和参考伽马电压(VGAMMA)分别使用PMIC和伽马IC产生。控制板的输出信号通过柔性扁平电缆(FFC)和数据板传输到源驱动IC和扫描驱动IC。

实验结果表明,基于DRD用于高图像质量和低功耗的点反转数据寻址技术,成功地在保持高质量图像的同时,达到了低功耗的目的,适用于有高图像质量和低功耗目的的TFT-LCD。

2.3 优化a-IGZO TFT基板的低功耗设计

对于LCD显示技术,不同类别的晶体管所产生的功耗也不同。随着从非晶硅(a-Si)到低温多晶硅(LTPS)再到IGZO(铟镓锌氧化物)的转变,晶体管的电子迁移率和电子缺陷密度不断提高,从而降低了液晶显示的功耗。因此,采用新型半导体技术的LCD显示器通常会比使用非晶硅TFT的LCD显示器具有更低的功耗,但是新型半导体技术的功耗仍然具有提升的空间,这给TFT的低功耗研究带来了新的思路。

半导体本身的特性对TFT基板的功耗有着重要影响,通过优化半导体性能,可以使TFT的功耗得到降低。近年来,非晶铟-镓-锌氧化物(a-IGZO)薄膜晶体管因其较高的迁移率、良好均匀性和低生产成本而被广泛用于高分辨率显示驱动面板和具有窄边框的小尺寸集成扫描驱动器[14],但其低功耗水平还有一定的提升空间。

常用的扫描驱动器由控制TFT、上拉和下拉TFT、用于自举上拉TFT的栅极电压的电容器(Cboot)以及时钟信号(CLK)总线线路组成[15-16]。上拉TFT的尺寸被设计成足以驱动面板的大扫描线负载。由于CLK总线线路连接于大型上拉TFT的漏极,因此CLK之间的寄生电容上拉TFT的总线和栅电极增加,将会导致CLK的电阻和电容(RC)延迟也增加[14]。为了补偿CLK增加的RC延迟,应该通过增加CLK总线的宽度来减小CLK总线的电阻,但是这会增加扫描驱动器的面积,同时CLK总线的大电容、大尺寸的上拉TFT也会导致扫描驱动器的功耗增加[17]。

为解决此问题,Do-Sung Kim提出了一种小面积和低功耗扫描驱动器。该驱动器使用具有双栅极的共面a-IGZO TFT,用于大尺寸和高分辨率显示器,同时保持自举电容器的额外面积。该方案中TFT像素块电路的底部栅极保护沟道区域不受背光入射光的影响。图7(a)和(b)分别显示了具有单栅极(传统TFT)和双栅极(所提出的TFT)的共面a-IGZO TFT的截面图。所提出的TFT通过增加双栅极TFT的导通电流来减小扫描驱动器的上拉TFT的尺寸,进而减小了CLK总线的电容。CLK总线的电容减小可以在保持CLK的RC延迟的同时增加CLK总线的电阻,从而可以减小CLK总线的宽度。

提出的TFT底栅保护沟道区域免受背光入射光的影响,通过增加双栅极TFT的导通电流可以减小扫描驱动器的上拉TFT的尺寸。传统的TFT没有CBOOT。CLK总线的电容减小可以在保持CLK的RC延迟的同时增加CLK总线的电阻,从而可以减小CLK总线的宽度[18]。此外,Cboot选择性地形成在底栅电极和源电极之间,如图7(b)所示。因此,在所建议的TFT结构中不需要用于Cboot的区域。缓冲层和栅极绝缘体层由二氧化硅制成。钝化层、a-IGZO层、栅绝缘层和缓冲层的厚度分别为400,40,300,500 nm。

为了验证所提出的TFT和传统TFT的电学性能,制作了沟道宽度(W)为7.0 μm,沟道长度(L)为4.5 μm的TFT,如图8(a)所示。图8(b)给出了所提出的TFTs和常规TFTs的测量传递曲线。所提出的TFT的底部和顶部栅极连接在一起,它们具有相同的栅源电压。在VGS=10 V和VDS=10 V时,所测得的电流、场效应迁移率、亚阈值斜率(SS)和阈值电压分别为28.5 μA和17.3 μA、11.0 cm2/(V·s)和7.2 cm2/(V·s)、130 mV/dec和130 mV/dec、0.24 V和0.10 V[15]。

图8 (a)所提出的TFTs和传统的TFTs的照片;(b)测量的转移曲线[15]。Fig.8 (a) Photographs and (b) measured transfer curves of the proposed TFTs and conventional TFTs[15]

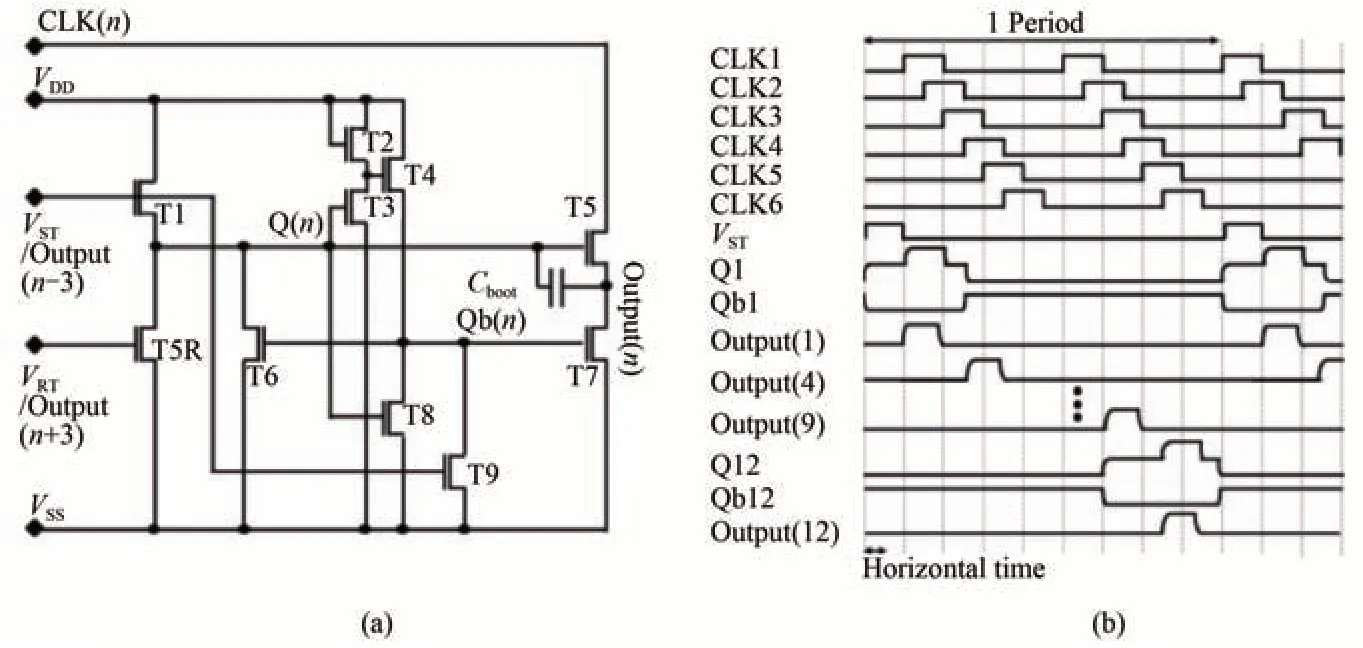

所提出的TFT扫描驱动器由12个阶段组成。图9为一级扫描驱动器的电路原理图和时序图。所提出的TFT应用于占据扫描驱动器大面积的上拉TFT(T5)和下拉TFT(T7)。扫描驱动器使用6个CLK和一个启动信号(VST)运行。在扫描驱动程序启动时,VST的电平变为高电平。然后,上拉TFT(T5)的栅极节点(Q)第一级变成VDD,而下拉TFT(T7)的栅极节点(Qb)同时通过T8和T9放电到VSS。当CLK变为高电平时,Q处的电压由Cboot自举,输出通过T5变为高电平。3次水平后,扫描驱动器第四级的输出通过T5R将Q处电压到VSS处的电压放电,并通过T4将Qb处的电压改变为VDD。

图9 (a)一级扫描驱动器的电路原理图和(b)时序图[15]Fig.9 (a) Circuit schematic and (b) timing diagram of one stage of the scan driver[15]

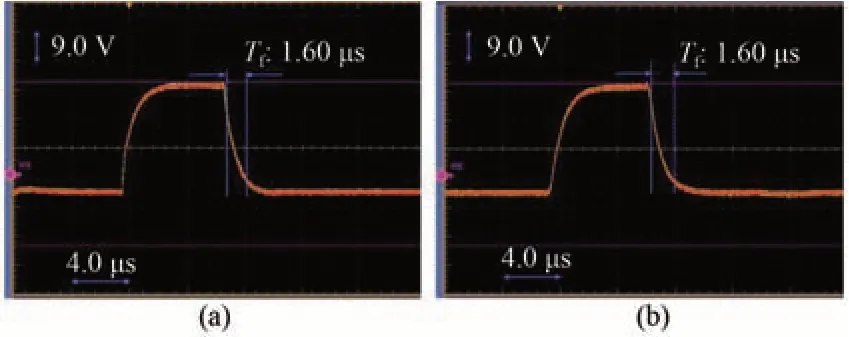

为了比较驱动器的功耗性能,对所提出的驱动器与传统驱动器电压进行了测量,结果如图10所示。传统和所提出的TFT的Tf被测量为1.60 μs。功耗是通过测量CLK总线、VDD和VSS线的电流计算的。传统和所提出的TFT的扫描驱动器的CLK总线线路、VDD和VSS线路的测量电流分别为91.9 mA、69.6 mA、12.1 mA和11.9 mA、38.4 mA、35.6 mA。使用传统和所提出的TFT的扫描驱动器的计算功耗分别为3.04 W和2.41 W[15]。

图10 (a)传统TFTs和(b)低功耗扫描驱动器的输出电压[15]Fig.10 Output voltage of scan driver with (a) conventional and (b) low power scanning driver[15]

经过验证,所提出的扫描驱动器具有比常规扫描驱动器小20%的面积,测量的两个扫描驱动器的下降时间同样是1.60 μs。利用所提出的TFT测量的扫描驱动器功耗为2.41 W,相对于传统TFT降低了20%,达到了降低功耗的目的。

本小节讨论到了新型半导体的优化技术。目前国内新型半导体的研究重点主要集中在氧化物半导体薄膜晶体管基板材料的设计与优化。国内研究者致力于开发具有低功耗特性的氧化物半导体材料。常见的材料包括氧化铟锡(ITO)、氧化锌(ZnO)、氧化铟镓锌(IGZO)等。通过调节材料的成分、掺杂以及晶体结构等方法,优化材料的导电性能和载流子迁移率,以降低材料本身的功耗。

国内氧化物半导体TFT基板的低功耗研究已经取得了一定进展,但仍面临一些挑战,如提高材料的导电性能和迁移率[17]、优化器件结构以及可实现的降低功耗技术应用[18]等。未来的研究可以继续深入探索这些方向以满足低功耗需求,并推动氧化物半导体TFT基板低功耗技术的发展。

3 TFT基板的外设驱动优化方法

TFT基板外设也是影响其功耗的重要因素。外设驱动功耗高会增加整个系统的功耗,降低设备的电池寿命。合适的外设驱动可以确保系统实现低功耗的操作,因此对外设驱动进行优化也是实现低功耗重要手段[19]。影响外设驱动的主要因素集中在从下3点:外设驱动工作时间、外设驱动工作效率和外设驱动电学性能。针对上述3个方面的影响因素,具有代表性的方法有:采用选择性扫描驱动器、采用伪多端口SRAM、采用斜停概念的TFT数字驱动电路、选择低功耗驱动IC等。

3.1 采用选择性扫描驱动器的低功耗设计

在TFT外设驱动的工作过程中,持续工作的时间越长,对TFT基板所需的能量就越多。因此在实际应用中如果能在保持显示效果的同时,减少TFT外设驱动工作的时间,将会使TFT基板的功耗大幅减少。

在多数TFT-LCD中,刷新所需电压在总功率中占到一定比例,尤其是高刷屏幕[19]。为节省功耗支出,Jae-Hee Jo等学者研究出一种新型选择性扫描驱动电路,该电路只能在选定区域中产生扫描信号,只刷新需要更新的区域而不刷新整个显示[20-21]。用于选择性驱动的附加区域仅占据单元阶段区域的14.5%。图11展示了所提出的选择性扫描驱动的概念。扫描信号仅在所选区域中产生。在不产生扫描信号的区域中,像素保存先前的帧数据。因为它们不需要通过在未选择区域的定时保持数据电压来对数据线和像素充电或放电[22],所以可以节省数据驱动器的功耗。

图11 传统驱动和选择性扫描驱动的比较示意图[22]Fig.11 Schematic diagram of conventional driving and proposed selective scan driving[22]

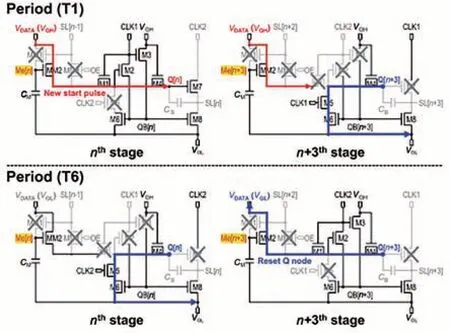

图12为所提出的新型驱动电路与时序图,其工作原理为:在产生开始脉冲(STP)之后,从第一级到最后一级依次产生扫描信号。OE在此期间保持为高(VGH),以便先前的输出信号可以通过MM3作为扫描驱动器单元的输入。前一输出信号导通当前级的晶体管MM1。在图12(b)中当sl[n-1]和sl[n+2]为高时,VDATE变为高电平。因此,高压(VGH)存储在ME[n]和ME[n+3]中。前者用于选择性扫描的开始,后者用于选择性扫描的结束。

图12 所提出的新型驱动电路的(a)电路图和(b)时序图[22]Fig.12 (a) Circuit diagram and(b) timing diagram proposed in Ref. [22]

图13示出了所提出的扫描驱动电路的操作流程图,在ME节点中存储VGH电压的两级的详细操作。与编程期间不同,在选择驱动期间没有STP。取而代之的是,在周期T1期间,在[n]和[n+3]这两个阶段中,通过MM2将VDATE作为新的开始施加脉冲。然而,VDATE的高电压不转移到Q[n+3],而是转移到Q[n],因为在周期T1期间只有CLK1为高。为此,高电压必须存储在时钟连接不同的两级的两个ME节点中。因此,所选扫描线的总数变为奇数。注意OE关闭MM3以防止输入节点被前一扫描线放电。在周期T6中,OE关断MM3,以防止最后的扫描信号(SL[n+4])在图12(b)中传播到下一级SL[n+5],也防止Q[n+3]节点通过MM3被放电。相反,Q[n+3]由VDATA通过MM2放电,如图12(a)所示。为此,VGH电压必须在编程期间存储在存储器节点me[n+3]中。如图12(b)所示。最后一条扫描线是SL[n+4],但高电压存储在ME[n+3]中以指定结束位置。

图13 扫描驱动电路的操作详细说明[22]Fig.13 Detailed operation of proposed scan driver circuit[22]

所提出的电路只能在选定区域中产生扫描信号。通过减少不必要的刷新,可以节省浪费的功率。并且在扫描驱动器电路中添加了一个额外的存储单元以及3个晶体管和一个电容器(3T1C)用于选择性驱动。OE确定扫描驱动器单元的输入端是否连接到前一级。VDATE既用于编程,也用于任意选择的区域。存储单元的输出连接到扫描驱动器单元的输入节点。附加区域仅占单元级区域的14.5%[21],并且还与其他类型的扫描驱动器兼容。此类型的驱动方式可以相对减少能耗支出,在需要进行刷新的区域才需要功耗,而不刷新的区域保持原来的功耗即可。

只有当施加扫描脉冲时才更新数据电压,并且在周期的其余时间内保持恒定,这样随着所选线的数量减少可以显著降低动态功率。结果表明,当选择50%和25%的扫描线时,数据刷新的动态功耗分别降低了25%和37.5%[22]。因此,所提出的电路主要降低了不必要的数据刷新所需的动态功率。

3.2 采用伪多端口SRAM电路驱动的低功耗设计

外设驱动工作效率也是影响TFT功耗的重要因素之一。如果外设驱动器工作效率较低,会导致信号传递不稳定,不仅会影响显示效果,还会增加电路延迟和数据传输时间,增加功耗。因此,要想达到低功耗的需求,提高外设驱动的工作效率也是一种很好的解决方案。

在液晶显示器和有机发光二极管(OLED)显示器的驱动电路中,引入各种数字信号处理(DSP)算法,如色彩增强[23-25]、阳光可读性[26]、动态背光控制[27]和显示数据压缩[28],可以很好地增强显示质量和降低功耗。其中许多算法需要一个n×n滤波器。滤波器的实现需要一个存储元件来临时保留n行或n-1行的显示数据。要存储的显示数据的实际行数取决于存储元件的设计方法,但是随着技术的不断进步,静态随机存储器SRAM的单元数量不能够得到满足,常常需要定制。Hing-Mo Lam等学者提出了用于显示驱动IC中图像处理的N×N滤波器,采用预读机制、字线和列选择信号转发等技术,利用单端口6T SRAM电路构造伪多端口存储阵列,以一个基于3×3滤波器的应用为例进行了研究。对于其他尺寸的滤波器,如5×5或7×7,操作相同,唯一的区别是内存数组的大小。与传统的数据存储实现方式相比,所提出的线路缓冲器的布局面积和有功功耗分别减少了50.3%和47%,但访问速度略有下降[29]。

在此基础上所提出的电路综合了单端口SRAM和双端口SRAM两种方法的优点,用于滤波器数据的暂存。该方案采用单口6T SRAM电路,只存储两行显示数据。伪多端口存储器设计利用了滤波器预定顺序操作的特性。预读机制(或读/写位置对齐)、字线和列选择信号转发是实现该设计的关键技术,并且只需要一个存储块来存储这两行显示数据。

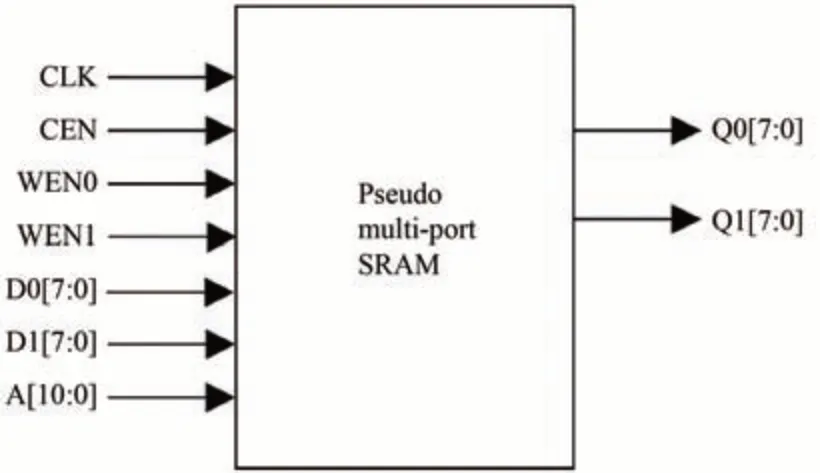

图14显示了所提出的伪多端口存储器设计的输入/输出接口。存储器电路实际上是一个4端口存储器阵列,能够在4个不同的物理位置进行4次读/写操作。3×3过滤器应用程序只允许3个端口写一个数据和读两个数据。

图14 伪多端口存储电路的I/O接口和符号,用于3×3滤波器的应用[29]。Fig. 14 I/O interface and the symbol of the proposed pseudo multi-port memory circuit for the 3×3 filter application[29]

CLK、CEN、WEN0和WEN1分别是时钟输入、芯片使能、行缓冲器1的写使能和行缓冲器2的写使能,A[10∶0]为11位输入地址,D0[7∶0]和D1[7∶0]分别是行缓冲器1和行缓冲器2的8位输入数据,Q0[7∶0]和Q1[7∶0]分别是行缓冲器1和行缓冲器2的输出数据。所有输入信号都在CLK信号的上升沿捕获,CEN为‘0’。

图15给出了所提出的伪多端口存储器设计的框图。存储器电路由4组存储器阵列组成,从Bank0到Bank3。控制器和行解码器位于存储器阵列的中间。每个存储体具有写使能WEx、列选择XY_L[7∶0]或XY_R[7∶0]、字线WLR[119∶0]或WLL[119∶0]、数据输入DINx[7∶0]和数据输出Qx[7∶0]的输入/输出信号,其中的小写字母“x”代表BANK号码。

为了支持3×3过滤器的应用,BANK0和BANK2被配置为分别存储LineBuffer1的奇偶数据,BANK1和BANK3被配置为存储行缓冲器2的偶数和奇数数据。因此,行缓冲器1的输入数据D0[7∶0]连接到BANK0和BANK2,行缓冲器2的输入数据D1[7∶0]连接到BANK1和BNAK3。当写地址到达行的最后位置时,例如ADDR[3∶0]=15,信号WLL_ADV_EN接通,将存储器电路右半部分的解码字线转发到存储器电路左半部分的下一行的字线[28]。即当WLL_ADV_EN为高时,WLR[0]被转发到WLL[1],WLR[1]被转发到WLL[2],…,WLR[119]被转发到WLL[0]。

图16展示了所提出的伪多端口存储器电路的地址译码电路,包括预解码器、行解码器、列解码器和列选择信号转发电路。与传统的SRAM电路设计相比,列选择信号转发电路由8个2∶1 MUXs组成,这是支持所提出的伪多端口存储器设计所需的额外电路。当ADDR[0]为“1”且写位置位于BANK2或BANK3时,存储器电路右半部分的列选择信号XY_R[X]将被转发到存储器电路左半部分的下一列XY_L[X+1]。

经验证,该方法的版图面积分别减少了50.3%和30.2%[29]。与传统的双端口8T和信号端口6T存储电路相比,3×3滤波运算的有源功耗分别降低了47%和30.8%,但访问速度略有下降(7.5%和7%)[29]。当性能不是最关键的问题时,所提出的伪多端口SRAM电路是n×n滤波应用中临时存储的理想选择。

3.3 采用斜停概念的TFT数字驱动电路的低功耗设计

TFT的功耗与驱动电路电学性能有着密切关系,电学性能的好坏会直接影响TFT的功耗。因此,需要在这些因素之间取得平衡来实现低功耗的设计。

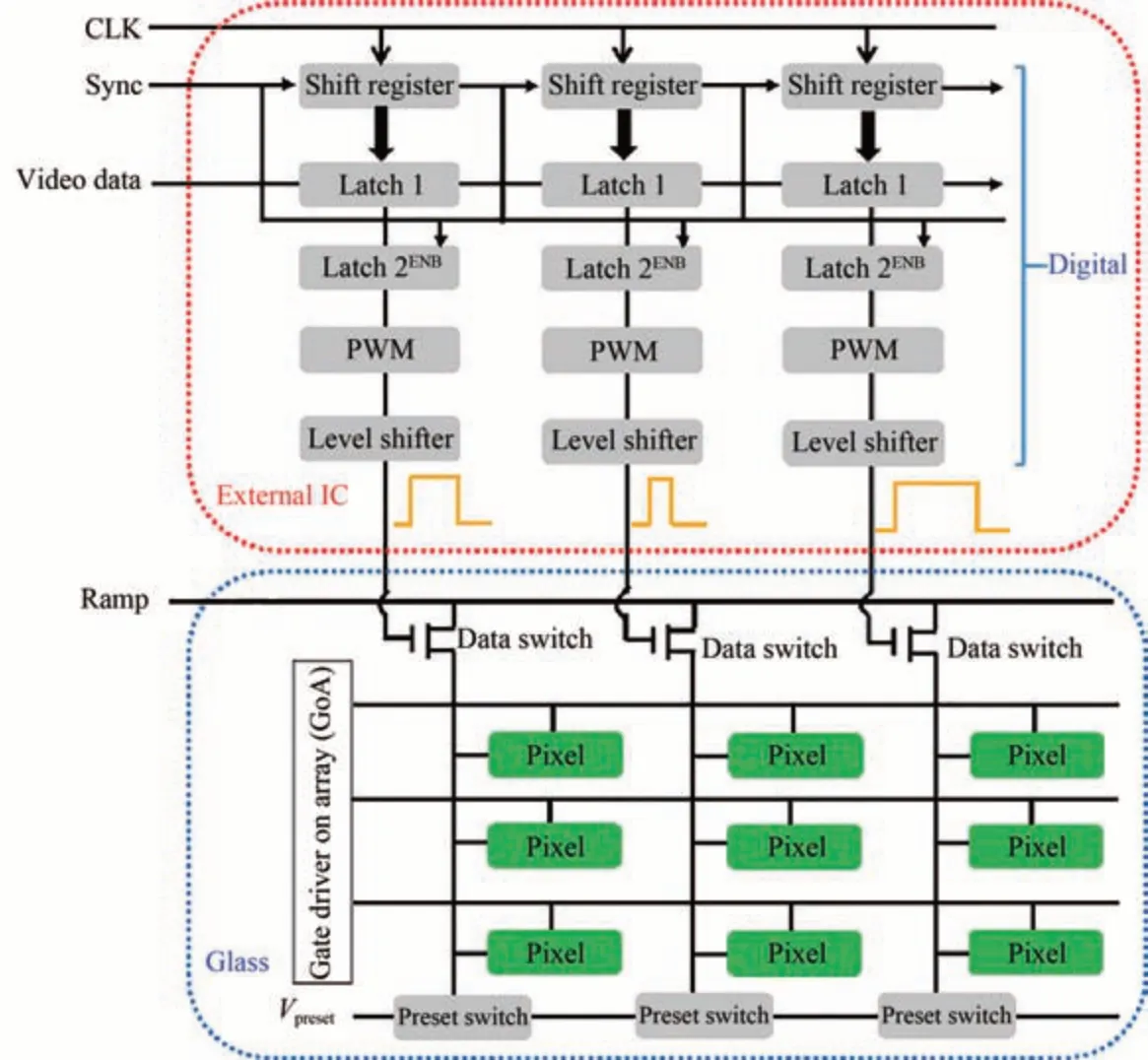

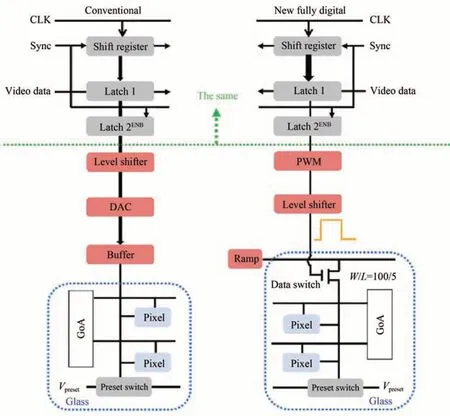

传统优化源驱动器的常用方法为提高源驱动器的效率、减小的模区面积和提高缓冲器的转换速率[30-31]。图17展示了传统的TFT-LCD系统框图。在传统的系统框图中,LCD源驱动的基本配置并没有发生很大的变化,其功能模块在集成电路(IC)中或者在玻璃基板上实现[32-35]。在实现视频数据的接收、分配和存储的数字机制的基础上,继续使用DAC和单位增益放大器将数字数据信号转换为像素的驱动电压[36-40]。这样的混合信号配置使得源驱动程序设计更加复杂和困难[41-42]。通过改变配置为全数字化,可以带来易于编程、高可靠性和降低成本等优点。

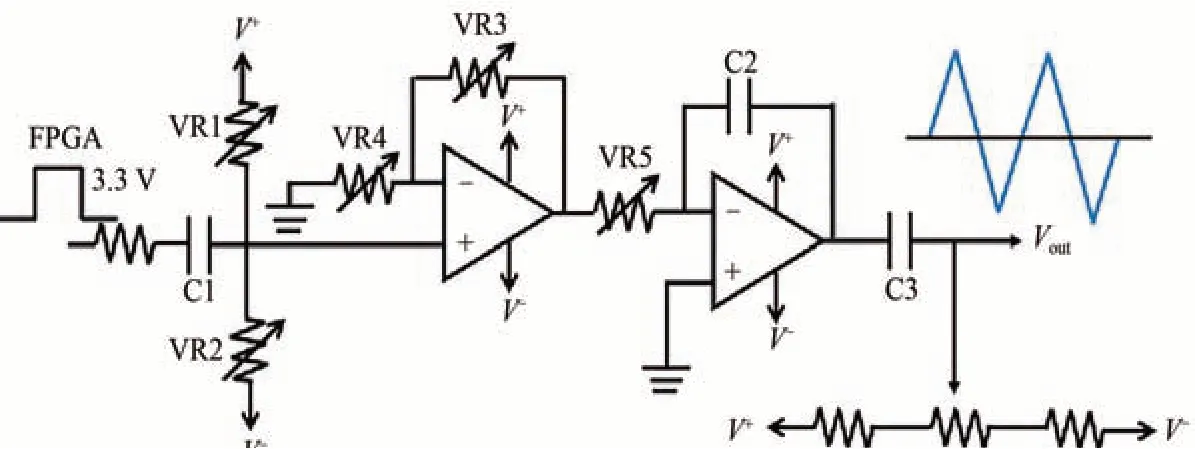

Ya-Hsiang Tai提出了一种全数字驱动方法,利用带斜坡的脉宽调制(PWM)的概念代替DAC和缓冲器。斜坡波电路原理图如图18所示,其中:V+固定在12 V,V-固定在-12 V,VR1~VR6为100 kΩ可变电阻,C_1~C_3为1 μF的电容。其主要作用是将FPGA产生的时序信号转换成±4 V、占空比为50%的斜坡信号。为了便于实施实验,将其在外部源驱动器中实现,并不将电路集成到玻璃上。它可以去除模拟部分,因此设计可以相对简单和快速。此外,还可以减少驱动器本身耗散的功率,避免发热问题。

图18 斜坡波电路原理图[36]Fig.18 Schematics of ramp wave circuit[36]

图19所展示的是新型全数字驱动方法框图。在外部集成电路中,S/R、Latch 1和Latch 2的部件与传统驱动方法相同。不同的部分是脉宽调制(PWM)电路,它将存储在锁存器2中的视频数据转换成数字域的脉宽信号,因此也需要电平移位器来提供足够的摆动电压控制玻璃上的数据开关。系统需要增加一个共同的斜坡电压源。对于每条数据线,通过预置开关将其电压预置为初始电压,这与传统方法中电荷中和的操作完全相同。斜坡电压从预设值开始,通过数据开关对数据线和所选行上的像素进行充电。通过控制脉冲的宽度,在适当的时间关闭数据开关,可将目标电压设置为所选像素。在这种配置中,外部集成电路是完全数字化的。

图19 全数字驱动方法框图[36]Fig.19 Block diagram of new fully digital driving method[36]

在所提出的驱动方法中,外部电容器以逐步方式向负载提供电荷,并且电荷返回到电容器,而不是放电到地。驱动电路框图如图20所示。

图20 传统和全数字驱动电路中一个数据驱动通道的框图[36]Fig.20 Block diagrams for one data driving channel in conventional and new fully digital driving circuits[36]

经过实验验证,计算出两种方法在每个数据通道各块的功耗。在比较中省略了两种驱动方法中相同的部分,如移位寄存器和锁存器[36]。在传统的驱动电路中,一个数据通道的DAC和Buffer的静态功率分别为2 μW和20 μW[42]。对于有16个电平移位器的8位数据驱动器,电平移位器的动态功率计算为22 μW,而静态功率可以忽略,因为这个值太小。至于全数字驱动方法,静态功率是可以忽略的。相应地,用于产生数字脉冲的PWM和用于控制玻璃上数据开关的电平移位器的动态功率估计小于3 μW和12 μW[35]。可以看出,由于全数字化配置,功率得到了明显降低。

在±4 V和76.8 kHz的行线运行下驱动20 pF的数据总线负载,需要另一个大约6 μW的动态功率。在传统的驱动方法中,该功率由缓冲器消耗,其热量需要在集成电路中处理[43]。相反,在新方法中,该功率由外部斜坡电压源提供,加热问题可以单独处理。这样可以进一步降低集成电路的面积,从而降低集成电路的成本。

4 总结与展望

本文回顾了近年来对TFT低功耗驱动的研究方法,总结了目前所面临的研究困境与挑战。目前对低功耗驱动的研究大多集中在驱动芯片设计、优化驱动控制电路、设计新型光栅结构和改进像素电路等方面,并在这些方面都取得了一定的成就与突破,达到了低功耗的目的。但是仍然存在一些瓶颈和难点,主要包括以下几个方面:(1)驱动芯片集成度不够高。目前的驱动芯片具备的功能较为单一,需要多个驱动芯片共同合作完成驱动任务,无法高度集成。随着以TFT为基板的显示设备的发展,现有的驱动芯片将无法满足未来屏幕的发展,这导致目前所有搭载驱动芯片的驱动板体积无法缩小,功耗无法继续降低。(2)功耗优势受制于当前的制造工艺技术。目前的TFT低功耗驱动优化研究虽然能够从某种程度上降低功耗,但是受制于当前工艺技术[44],如薄膜晶体管技术,低功耗的驱动方案对薄膜晶体管质量要求过高,目前的薄膜晶体管在实际生产过程中容易产生缺陷,影响晶体管的性能和可靠性,这需要更高的工艺技术水平和更为复杂的设计思路,对未来的科研人员也是一种挑战。

综合当前TFT低功耗驱动的研究现状,未来可能会在以下几个方面突破:(1)引入新材料和技术。新材料和新技术的不断发展可能会使TFT驱动能效得到进一步的提升,例如本文所提到的采用a-IGZO材料的TFT基板低功耗设计方案;(2)像素控制电路设计技术。高效的像素结构与控制方法会使功耗大幅降低,同时还能提升图像质量与缩短响应时间。本文中Ya-Hsiang Tai等学者提出的采用斜停概念的TFT数字驱动电路方案,在达到低功耗目的的同时,也为许多学者提供了探索数字波直接驱动TFT基板显示器件的方向。(3)新的集成电路技术[45]。新的集成电路技术将会使TFT低功耗驱动IC实现突破,为TFT驱动器的低功耗设计提供更多的解决方案,如三维堆叠技术[46-50]和混合集成电路技术[51-54]可以提高驱动IC的能效和可靠性,对未来的低功耗驱动研究提供了更多的可行性方案。(4)系统算法优化技术。随着近年来的算法在各个领域的发展,将其应用于优化电路的控制策略来降低功耗也是非常可行的技术之一,可以从动态电压和频率调节、能量管理技术、电源管理和休眠模式、数据压缩和传输优化4个方面进行考虑,通过使用这些优化策略并与其他相应的技术相结合,可以有效降低TFT的功耗,为未来超低功耗的发展提供可行性方案。