一种高可靠性三相全桥IGBT 驱动电路的设计

邢鑫怡,程 心,王柯凡,金超

(合肥工业大学 微电子学院,合肥 230601)

绝缘栅双极型晶体管(insulated gate bipolar transistor,IGBT)是一种复合功率半导体器件。从结构上看,IGBT 相当于由一个金属-氧化物半导体场效应晶体管(metal-oxide-semiconductor field-effect transistor,MOSFET)和一个双极结型晶体管(bipolar junction transistor,BJT)共同组成,所以它集合了这两种器件的优点,具有高输入阻抗、低导通压降,成为发展最为迅速的新一代电力电子器件。IGBT 器件被广泛应用于高功率大电流领域中特别是在600 V以上的高压电路系统中,在汽车电子、消费电子、新能源等领域都得到广泛的应用[1-3]。

文献[4]提出了一种可同时驱动高侧和低侧开关电源装置的高压栅极驱动模块,有效降低了驱动模块的总体积;文献[5]设计了一种基于SOI 工艺的功率MOSFET 的栅极驱动电路,其最高输出电压可达400 V;文献[6]设计了一款1200 V/600 A 半桥结构的大功率SiC 模块;文献[7-8]主要介绍了温度对栅极驱动器的影响以及过流检测功能的设计。在高压功率驱动电路中,电平位移电路是其核心部分;文献[9]提出了一种具有高抗噪性的电平位移电路,应用于600 V 高压半桥驱动电路中;文献[10]提出了一种新的具有多金属环的电平位移电路,降低了高侧栅驱动器的输入端的电压差。但在实际应用中,高压电路中由于寄生效应的存在,会产生电压偏移现象,从而使电平位移电路产生错误触发。

本文基于X-FAB 1.0 μm SOI 工艺,设计一种高可靠性的三相全桥IGBT 驱动电路,提出了一种可以对输入信号的错误状态进行判断的死区时间产生电路,避免因高、低侧信号同时输入有效电平所造成的错误;采用一种将浮动电源和浮动地进行隔离的新型高压电平位移电路,并具有欠压检测、过流检测、错误逻辑控制等保护电路,在满足驱动能力要求的同时提升驱动电路的安全性与可靠性。

1 IGBT 的开关特性

从结构上来看,IGBT 的输入端为MOSFET 的栅极,因此开启信号施加到MOSFET 的栅极上。与MOSFET 类似,IGBT 作为一个压控器件,其开启是通过电压而不是电流进行的,但IGBT 器件开启的速度随栅极电压的增加而加快。由于BJT 是被基极电流控制的器件,所以其开启速度显然慢于压控器件IGBT 的开启速度。但正因为IGBT 的导通需要BJT 和MOSFET 均进入工作区,所以IGBT 的开启速度会略慢于MOSFET。在高频状态下,器件导通和关断产生的动态电流会变得很大,进而会对整个系统产生显著影响。

2 IGBT 驱动电路及关键模块设计

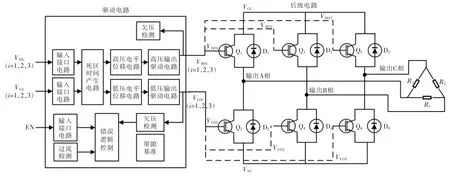

本文设计的IGBT 驱动电路系统框图,如图1所示。三相全桥由3 个单相半桥IGBT 器件形成,每个支路有2 个带有反向并联二极管的IGBT 组成,产生A、B、C 三相输出用于驱动后面的电路。

图1 三相全桥IGBT 驱动电路系统框图Fig.1 Block diagram of three-phase IGBT driver circuit

图1 中,IGBT 驱动电路的输入信号由3 个高侧输入信号VHI1、VHI2、VHI3和3 个低侧输入信号VLI1、VLI2、VLI3组成,分别用于控制三相半桥上下桥臂的通断。高低侧输入信号首先需要经过接口电路的处理,将3.3 V 或5 V 的输入信号转化为0~5 V 的方波并进行滤波整形,然后通过死区时间产生电路产生一个防止上下桥臂同时导通的死区时间,最后分别经过电平位移电路和输出驱动电路,形成高低侧的输出电压信号,输入到相应的IGBT 器件。此外,本设计中还包括相应的保护电路,在欠压、过流或发生短路状态下迅速对整个驱动电路采取有效保护措施。驱动电路的关键模块设计如下。

2.1 死区时间产生电路

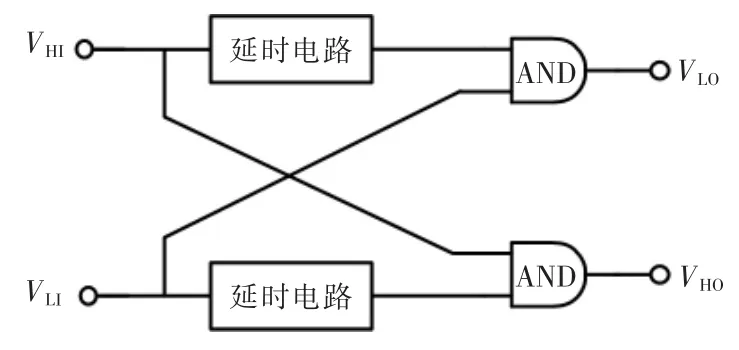

死区时间定义为上下桥臂的2 路输入信号同时关闭,即都处于低电平的时间。因此,为了避免由于延迟效应造成的上下桥臂直通现象,本文的死区时间产生电路用于产生一个稳定的死区时间,提高功率驱动芯片的稳定性,其核心为设计一个延时电路。传统的死区时间产生电路如图2 所示,通过延时电路产生延时时间,再通过逻辑门运算叠加到输出信号形成死区时间。这种结构在实际情况中存在着一定的风险,它仅适用于高低侧两路输入信号相位相反的情况,一旦由于随机因素出现高低侧输入信号同为高电平的情况,该电路很容易判断失误,产生两路同向的信号驱动后级IGBT 器件[11]。

图2 传统的死区时间产生电路结构图Fig.2 Traditional diagram of dead time generation circuit

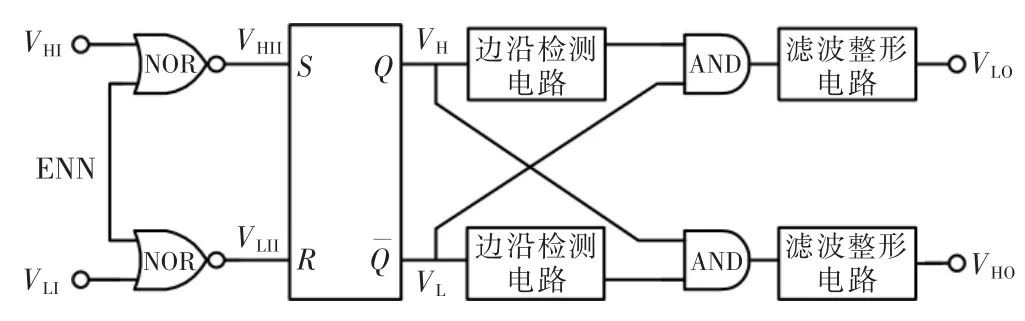

本文所设计的死区时间产生电路的结构如图3所示。电路原理为由输入级滤波电路处理过的高侧信号VHI和低侧信号VLI一起输入到死区时间产生电路中,ENN 是由保护电路和使能电路经过逻辑门运算产生的综合使能信号,低电平有效,高电平代表着芯片使能信号EN=0 或芯片发生欠压、过流等错误。高低侧输入信号VHI、VLI分别和ENN 经过或非门运算产生VHII和VLII,或非门的作用是当使能信号ENN 无效时,高低侧支路输出均为0。为了防止高低侧输入信号VHI和VLI出现同时为高电平的错误状况,本设计中采用一种改进的RS 触发器来对VHII和VLII信号进行逻辑判断。

图3 死区时间产生电路结构图Fig.3 Diagram of dead time generation circuit

在实际电路中由于穿通电流的存在可能出现VHII和VLII同为高电平的情况,极易发生上下桥臂直通的危险,因此本文设计了一种改进的RS 触发器,如图4 所示。输入端S 和R 分别经过一个反相器再输入到或非门RS 触发器中。当S=1、R=1 时,经过反相器后,不管Q 的状态如何,RS 触发器将会继续保持该状态,因此可以避免输入同为“1”时输出也同时为“1”的错误发生。当S=0、R=0时,经过反相器后,RS 触发器此时处于不定态,取决于哪个信号跳变更快,但输入同为“0”时,电路不存在短路的风险。

图4 改进的RS 触发器Fig.4 Improved RS trigger

2.2 高压电平位移电路

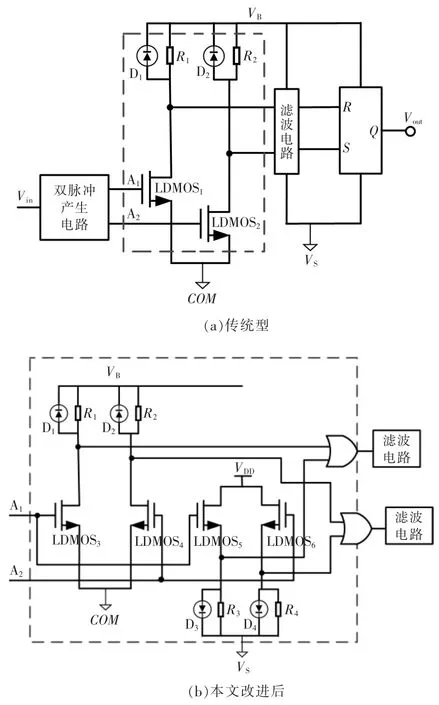

高压电平位移电路的作用是实现15 V~615 V的高压电平位移功能。实现电源电压和地转换为浮动电源和浮动地的电平转换,才能有效驱动后级IGBT 功率器件的正常通断。传统的双脉冲电平位移电路如图5(a)所示,双脉冲产生电路将输入信号转化为两路窄脉冲信号,分别与其上升沿和下降沿相对应,有效降低系统的功耗。通过高压功率管LDMOS,漏极电压转换为比浮动电源VB低的输出。下一级再将高压信号转化以高端浮动地信号VS为参考的脉冲,经过RS 触发器再将窄脉冲还原回正常的高压驱动信号,则整个过程完成了从0~15 V 到600~615 V 的电平位移,从而达到驱动IGBT 功率器件的能力。

图5 高压电平位移电路Fig.5 High voltage level shift circuit

本设计基于传统的双脉冲电平位移电路进行了改进,图5(b)为针对图5(a)虚线部分改进后的电路结构。这种结构采用了4 个LDMOS 高压功率器件,分别进行浮动地的电平转换和浮动电源的电平转换。当信号转化为与上升沿和下降沿相对应的两路脉冲后,当窄脉冲A1来临时,LDMOS3和LDMOS5管导通,LDMOS4和LDMOS6管截止,输出一个相对于VB的低电平信号,VS为浮动地信号,其电压变化范围为0~600 V,当脉冲来临时VS也处于0~600 V的上升沿位置,则LDMOS5的源端电压大于LDMOS3的漏端电压,随后信号经过或门转化为跟随浮动电平变化的电压。最后滤波电容和RS 触发器将脉冲信号恢复为方波的高压驱动信号。可以看出传统的电平位移电路,高压地信号VS与低压地信号COM并没有完全隔离,有可能会产生信号偏移,改进后的电平位移电路有效隔离了高低压两路地信号,减少了寄生效应产生的串扰,增强了电平位移电路的可靠性。

3 仿真结果与分析

本文基于X-FAB 1.0 μm SOI 工艺,用Cadence软件对三相全桥IGBT 驱动电路进行设计与仿真。

不含RS 触发器的传统死区结构的仿真波形,如图6 所示。可以看出,在t1~t2时间段内,当VHI与VLI均为“1”时,高低侧输入VHO和VLO同时为高电平,导致上下桥臂的IGBT 全导通、发生短路。

图6 传统死区结构功能仿真Fig.6 Simulation results of traditional dead time generation circuit

验证高侧输入信号与低侧输入信号为同为“1”时,本文中死区时间产生电路的功能仿真,如图7所示。可知,在t1~t2时间段内,输入信号VHI与VLI均为5 V,此时RS 触发器的两个输入端均为“1”,由RS 触发器的工作原理可知,RS 触发器保持原工作状态,因此VH 信号仍为低电平,最终死区时间产生电路的高低输入VHO和VLO避免了同时为高电平的情况,证明了本文所设计的死区产生电路能够保证驱动芯片在输入信号发生错误的状态下仍能正常工作。

图7 高低侧错误输入时死区时间产生模块功能仿真Fig.7 Simulation results of dead time generation circuit with high and low side error input

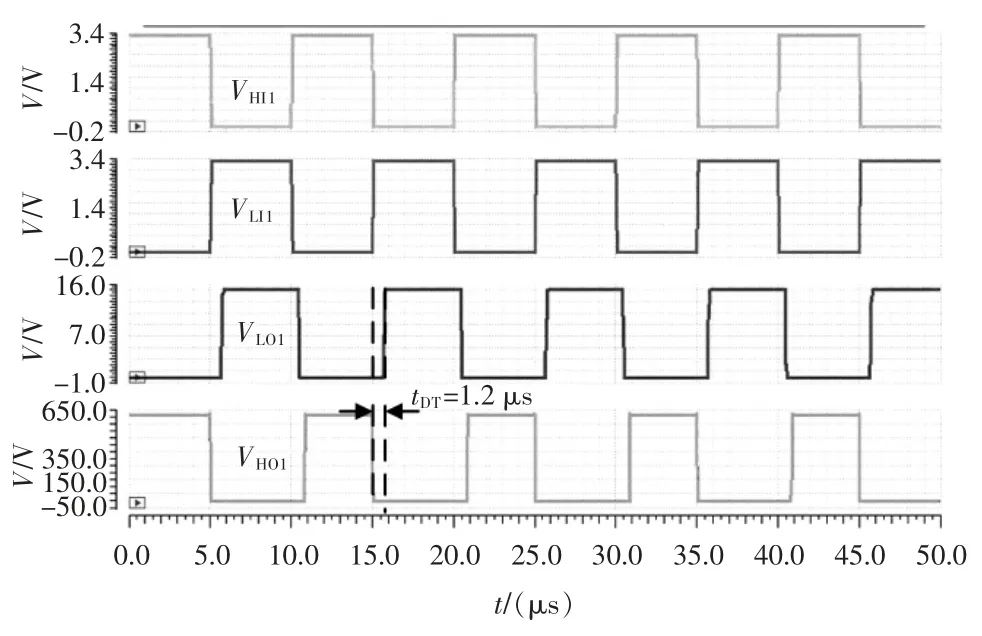

驱动电路整体仿真结果如图8 所示。可知,低侧输出信号VLO1的幅值为0~15 V,高侧输出信号VHO1的幅值为0~615 V,VLO1与VHO1之间存在着1.2 μs的死区时间,驱动芯片可以完成3.3 V 输入信号的逻辑转换,功能正常。

图8 驱动电路整体仿真波形图Fig.8 System-level simulation results of driver circuit

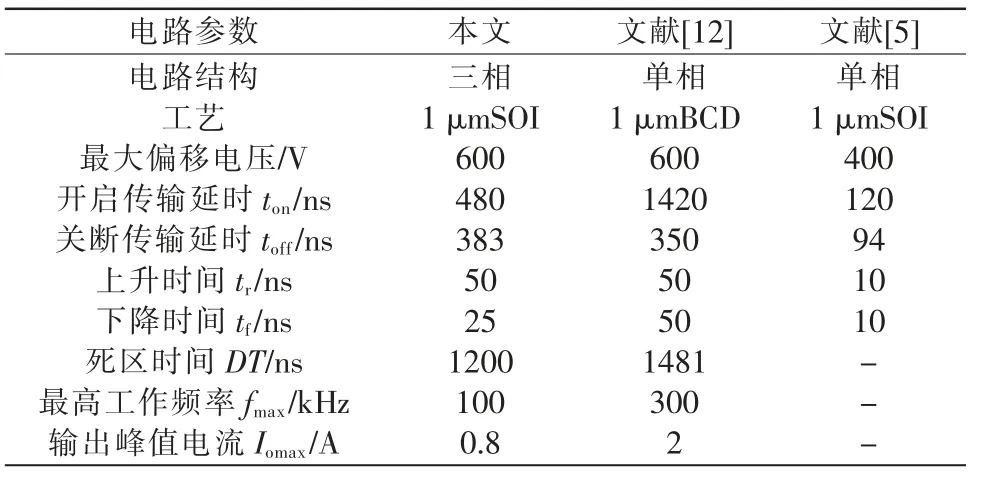

三相全桥驱动芯片控制部分各项参数如表1所示,表中所列出的各项指标参数均满足设计要求。

表1 驱动电路仿真参数Tab.1 Simulation parameters for driver circuit

本文驱动电路与现有文献结构的性能参数比较如表2 所示。可以看出,本文结构可应用于三相功率驱动系统中,应用面更为广泛。同时可高效实现600 V 高压电路的驱动,开启时间和关断时间相较于其他驱动电路有显著提高,驱动能力良好,综合性能高。

表2 几种IGBT 驱动电路仿真参数对比Tab.2 Comparison of performance parameters of several IGBT driver circuits

4 结语

本文基于X-FAB 1.0 μm 高压SOI 工艺,设计了一种适用于600 V 高压下的三相全桥驱动电路:设计了一种可以对输入信号的错误状态进行判断的死区时间产生电路,避免因高、低侧信号同时输入有效电平所造成的错误;并且提出一种将浮动电源和浮动地进行隔离的新型高压电平位移电路,可以减小高低压地电位之间的串扰,有效地提高了驱动电路的可靠性,三路高侧输出信号电压可达615 V,三路低侧信号输出电压为0~15 V,最大驱动电流达到0.8 A,仿真结果表明具有良好的驱动能力。仿真结果显示,各项参数均满足设计指标要求。