集成电路ESD的防护关键技术研究

许嘉航

(苏州大学,浙江 苏州 215006)

1 ESD现象的成因

1.1 外部原因

人体与环境之间的摩擦或电位差可能导致人体带有静电电荷,这些电荷接触或靠近集成电路时可能发生静电放电,导致电荷的传递及能量释放。干燥空气、低湿度及静电敏感材料的使用都有助于积累静电电荷,这些环境条件令集成电路更易受到静电放电的影响,增加ESD事件的风险。在集成电路的制造、测试、封装及处理过程中,各种设备及工具之间的摩擦可能产生静电电荷,当这些设备或工具接触到集成电路时,可能导致静电放电的发生。外部电源或电磁场的存在可能会对集成电路产生干扰,引发静电放电现象。

1.2 内部原因

集成电路工作过程中会产生各种吸引力,物质间或触碰外界时也有可能产生大量的电荷。电荷中的电量较大,若系统设备不能在短时间内进行中和,则有可能导致电荷数量增加,致使集成电路形成高压环境,产生静电放电现象[1]。

2 ESD失效模式及其机理

2.1 失效模式

ESD突发式失效模式是指集成电路中器件性能出现恶化,导致集成电路工作过程中的几个参数同时失效,造成运行故障,对器件造成不同程度的损害。突发性完全失效模式是由于集成电路短路或开路导致电参数发生较严重的漂移现象[2]。

ESD潜在式失效模式是因无法立即发现的损坏引起的,损坏可能很小,测试期间不会影响设备性能,但随着时间的推移,损坏可能导致设备出现故障且难以识别或修复。这是因为潜在式失效模式产生的微小损伤随着放电次数的增加损伤逐渐累积,导致阈值电压降低,最终损坏器件。

2.2 失效机理

ESD产生的电流在硅熔化中会产生热量,迅速增加温度功耗,导致硅表面融化,电路的电阻显著降低,通常电阻可降低约30倍,导致通过融化区域的电流增大。反馈效应会导致无休止的热失控,因为静电放电行为会产生结点反向偏置,从而出现雪崩击穿行为,令氧化层进入硅能量势垒之间,导致表面的阀值电压出现漂移现象,在很大程度上影响场效应晶体管的阈值电压VT的结果数据,包括双极性晶体管与二级管的击穿电压等也会受到影响[3]。

3 防护器件

电阻是用于防护ESD的主要器件,又称为无源器件,能够很好地控制静电及放电问题。系统中产生的电流大小在N型线电阻与其他电阻之间没有明显差异,故通常选择使用N型线电阻。当集成电路正常运行而电场强度减弱时,需考虑电流与电场强度之间的关系。

二极管PN结作为一种电压钳位器件,具有运行时能够回智的特点,通常用于集成电路中,可表现出良好的使用效果。但二极管有击穿电压性能且不具备较好的防护能力,需考虑使用。

集成电路包含NPN晶体管,也称为NPN型BJT。NPN晶体管是在正偏及反偏情况下使用PN结的器件,当电流正向流过NPN结时,BJT中的一个PN结正偏产生载流子,这些载流子以相反方向流过反偏PN结,有助于保护NPN结免受损坏,因为在反向偏置PN结中,载流子被吸引到结的带相反电荷的区域,在耗尽区产生强电场,从而防止大多数载流子穿过结,故NPN管具有高击穿电压的特性可以承受高水平的电流而不会损坏,适用于ESD防护。

目前,集成电路中的晶体管多采用MOSFET,可以起到ESD防护作用。MOSFET在集成电路中通常采用堆叠结构,包括多个串联的MOSFET器件,这种结构可以增加耐压能力,通过均衡及分散ESD电流将其分摊到各个器件上,减少单个器件受到过高电压的可能性。MOSFET的脆弱电荷注入区域采用特殊设计,可提高对ESD的抵抗能力,这些区域通常具有更高的掺杂浓度,以增加电荷分布及电流扩散,减少ESD事件对器件的影响。MOSFET中的反向PN结在ESD事件中扮演着重要角色,通过合理设计反向PN结,如使用低掺杂、大面积及多个级联结构,提高器件的耐压能力,吸收并分散ESD电荷。MOSFET的设计考虑了ESD事件中的电流控制,通过引入合适的电流路径及电流限制机制,如采用ESD保护电路及电流限制器,控制ESD电流的流向及幅度,减少对集成电路的损伤。

4 ESD防护技术及其应用

4.1 ESD防护技术

SCR防护。SCR结构主要由两种电阻及两个寄生三极管共同组成,这有助于提高防护效果,避免对集成电路的运行产生影响。应用可控硅晶闸管开展集成电路ESD防护时,这种器件一般被视为两端器件,故被连接于集成电路中。为了充分发挥SCR在ESD中的防护作用,晶闸管的阴极与P-well相互连接,阳极与N-well相互连接。此器件与双极型晶体管的P、N极相互连接,通过触发可控硅的方式保护集成电路。

基于全芯片的防护技术。在VDD与VSS轨之间运用Power clamp技术能够产生很好的防护效果。防护电路被分为动态电路与静态电路。动态电路通过全芯片防护技术处理实现静电防护。静态防护电路是提供一个电流较为固定的电路,当IC中电源电压大于触发电压时,Power Clamp保护电路导通,以电流形式将静电引出释放。SCR电路在二极管作用下触发,通常将其与二极管串联,在全芯片防护技术的支持下,Power Clamp防护电路的静电放电防护能力很强。

由ESD产生的集成电路损伤通常表现为热失效形式与电失效形式。当芯片的引脚承载ESD电流时,如果电流强度超过可接受范围,将导致芯片内部热量聚集。由于芯片内部空间有限,热量积聚问题较为严重,将导致局部区域温度迅速升高,芯片烧毁。热失效导致烧毁的区域主要包括互联线、扩散电阻及多晶硅电阻。电失效的区域通常是由于缺乏充分的保护电路或保护电路未能正常发挥作用,导致芯片内部电路承受ESD带来的高电压。

4.2 防护技术的应用

移动设备容易受到ESD的影响,在设备的输入/输出接口及电源线路中应用SCR防护,可防止因插拔连接器时产生的ESD对设备造成损害。汽车中的电子系统对ESD非常敏感,在汽车的电控单元(ECU)、传感器及线束中采用SCR防护与全芯片防护,可防止由ESD引起的电子故障。在工业自动化系统中,各种传感器、执行器及控制器都需要进行ESD防护。在设备的输入/输出接口及信号线路上使用SCR防护器件,可保护设备免受ESD的影响。医疗设备对ESD的防护要求非常高,因为ESD可能对患者安全及设备性能产生严重的影响。在医疗设备的输入/输出接口及电源线路中使用SCR防护器件,可防止ESD对设备造成损害。全芯片防护可以提供更为全面的防护措施,确保设备的可靠性及安全性。

4.3 ESD防护电路的设计

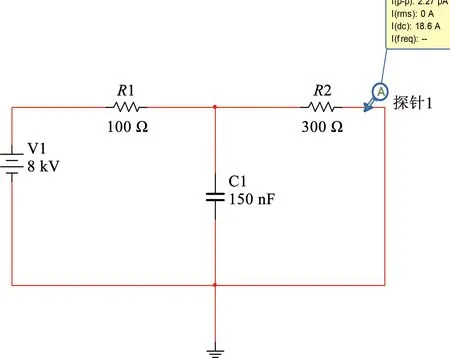

应用Multisim软件对ESD防护电路进行仿真分析。图1为ESD发生器等效电路结构,由于静电的电位非常高,根据IEC 61000-4-2标准将静电电位设定为8 kV。

图1 ESD发生器等效电路

从图2可以看到,若ESD发生器与IC之间缺乏有效的处理,18 A电流将会流入被保护电路,造成严重的后果。可使用一个电阻RL来代替被保护电路,以保护集成电路。

图2 ESD影响的最简化模拟

图3借鉴了传统的Π形滤波器,可去除高频噪声及瞬态信号,提供更干净的电源供应,故使用滤波电路可减少ESD放电对设备的影响。基于传统Π形滤波器在前后两翼各并联了一个双向齐纳二极管,仿真结果表明,经过改进的Π形滤波器的双向齐纳二极管具有钳位作用,流经滤波器的电流降至56 mA,流过的ESD电压有所改善,但是56 mA对于集成电路来说仍是一个不小的干扰项,需对ESD防护电路进行进一步改善。

图3 ESD初步防护仿真

MOSFET可应用于ESD防护电路中,故利用IC启动所需的VCC作为图4中Q1的启动直流偏置电压。根据MOSFET的电学特性,Q1此时已经进入截止区,其特性是随着电压的增大,MOSFET的SD间沟道夹断,电流以ΔI趋近于0的速度极缓慢地变化,以达到稳流目的。从电流计读数可以看到,流入被保护电路等效电阻RL的电流仅为19 uA,说明ESD电流对集成电路的影响得到了明显的削弱。

图4 ESD防护电路的进一步完善

5 结束语

ESD防护技术不断迭代更新,需科学、合理地设计应用该技术,保持集成电路的优良性能,延长其使用寿命。有针对性地设计ESD防护电路,改良集成电路,严格检测其防护效果,不断优化电路结构,加入新式器件,使用电学性能更好的材料,实现ESD防护技术的全面升级。