一种低功耗时钟树综合的寄存器聚类方法

唐俊龙 ,卢英龙 ,戴超雄 ,邹望辉 ,李振涛

(1.长沙理工大学 物理与电子科学学院,湖南 长沙 410114;2.湖南毂梁微电子有限公司,湖南 长沙 410003)

随着VLSI 技术中集成度越来越高,时钟频率越来越快,功率消耗已经成为现代IC 设计中的一个关键问题.动态功耗是指在对负载电容充放电过程中的功率耗散,占总功率消耗的最大部分,而在所有的电路元件中,时钟网络是动态功耗的主要贡献者,通常要消耗整个芯片功率预算的40%[1].因此,在数字集成电路的物理设计中,低功耗时钟树的设计具有重要意义.时钟树的负载电容由互连电容、寄存器电容和缓冲器电容组成.大部分的时钟树电容(大约80%)都在叶级,包括所有的寄存器和连接它们的导线以及驱动缓冲器[2].文献[3]对八个ISPD'10 基准电路的时钟树电容进行了简单的统计,缓冲器的电容是时钟树总电容的主要贡献者,减少叶级缓冲器电容能有效减少时钟树负载电容.

聚类算法可以把寄存器聚成几个组群,并为每个组群分配一个时钟缓冲器,因此寄存器聚类方法能有效降低叶级缓冲器的电容.为了有效减少时钟网络的功耗和时钟偏移,提出了一种高效的寄存器聚类方法.在满足叶级缓冲器的最大负载电容和最大扇出约束的条件下,将距离范围内的寄存器聚集成组群,生成时钟树的叶级拓扑结构.将这种高效的寄存器聚类方法集成到传统的CTS 流程中的实验结果表明,该方法有效减少了时钟网络的功耗和时钟偏移.

1 寄存器聚类方法的问题描述

在时钟树综合过程中,将寄存器聚成一个个组群的难点在于避免由寄存器分组所引起的时钟信号偏移和延迟[4].文献[5]通过计算寄存器的时序可行域,将寄存器移动到时序可行域重叠部分,在降低功耗的前提下,减小对时序的影响.然而,芯片上不仅存在时钟网,还存在信号网,寄存器的移动往往会对信号网布线长度产生影响,造成物理设计过程中出现布线拥堵的问题.文献[6]在分析近阈值电压下时钟树设计问题的基础上,提出了时序驱动且负载均衡的寄存器分组方案,增强了时钟树时序的稳定性,但该方法没有考虑到时钟树的功率耗散.文献[7-8]提出了一种最小线长聚类算法,用于低功率时钟树合成,基于曼哈顿距离求出最小树拓朴结构,然后设置阈值,确立合理的组群数目和缓冲器插入位置,最后通过经典的K-means 聚类算法迭代出最小线长的组群,但没有讨论每个组群之间负载不均衡对时钟偏移的影响.

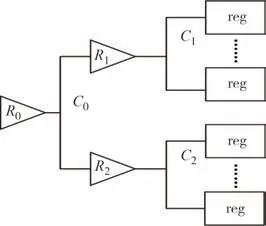

图1 表示了简单的时钟网络,其中R0表示时钟源驱动器的等效电阻,R1和R2表示两个寄存器群组的叶级缓冲器的等效电阻,R1=R2;Ci代表不同分支上的负载电容.

图1 时钟网络Fig.1 Clock network

根据 Elmore延迟公式计算不同路径的延迟如公式(1)和公式(2)所示[9];计算不同分支路径的时钟偏差(skew)S,如公式(3)所示.

由公式(3)可知组群之间负载电容的差值直接影响时钟偏移,所以在寄存器分组中,平衡不同组群之间的负载是十分必要的[10].

对于一个给定的布局,寄存器的电容是确定的.整个时钟树的缓冲器电容由几个因素决定,包括缓冲器驱动的负载电容、时钟树综合流程优化期间的时钟偏移和最大转换时间约束等[11].在传统的时钟树综合过程中,为了调整寄存器的延迟,减少时钟偏移,避免违反转换时间约束,通常需要插入大量的缓冲器到时钟树的叶层.高质量的寄存器聚类方法可以以最佳方式聚集寄存器,减少叶层的缓冲器插入数量,同时减少互连线电容,将局部时钟偏移限制在小范围内的同时,有效降低时钟网络的功耗[12].寄存器聚类问题通常可以描述为:

输入:寄存器集合Uregister={r1,r2,r3,…,rn},每个寄存器ri包括寄存器名和坐标位置(xri,yri).

输出:负载均衡的组群的集合Ucluster={c1,c2,c3,…,cm},每个组群ci包括组群内寄存器数、寄存器名和组群的中心cei,cei的坐标(xci,yci)计算公式如公式(4)、公式(5)所示.

2 寄存器聚类方法的设计

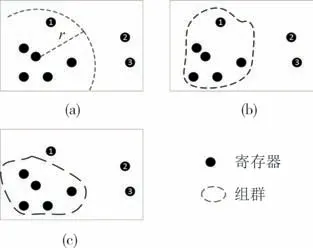

文中提出一种简单、高效的寄存器聚类方法.关键思想是在满足叶级缓冲器最大负载电容和最大扇出的同时,通过设置最大距离,限制组群半径,为每个组群定义合理的范围,使得距离组群中心较远的寄存器在聚类过程中不加入该组群内.避免了组群内布线过长,造成的叶级互连线电容过大的问题[13].寄存器分组示意图如图2所示.

图2 寄存器分组示意图Fig.2 Register grouping schematic

图2(a)表示以组群中心为圆心,半径r为所设定的距离阈值,虚线半圆为组群的聚类范围;图2(b)中,将满足距离约束,同时满足组群负载和扇出约束的寄存器加入组群内,不满足距离约束的寄存器2和3 不加入该组群,在下一次遍历时加入新的组群;图2(c)表示在满足距离约束,而不满足组群扇出或负载约束时,选取距离中心最远的寄存器1 去除该组群,在下一次遍历时加入新的组群.

组群内的电容作为一个重要约束可以直接影响到时钟信号的转换时间.保证时钟转换时间满足寄存器时钟端口的约束条件,有利于时序收敛,确保寄存器对数据通路正确采样[14].叶级缓冲器直接将时钟信号驱动到组群内的寄存器,为了保证组群内寄存器接收到满足转换时间约束的时钟信号,叶级缓冲器的最大负载电容与组群内的电容之和应满足约束条件式(9),单个组群内的负载电容之和Ccluster可以用公式(10)表示[15].

式中:Crn是寄存器时钟端口的本征输入电容;D表示组群的直径,定义为组群内最远的两个寄存器之间的曼哈顿距离;N是组群内的寄存器数量;α、β为自定义参数,用以调整组群内寄存器电容与互连线电容比重关系,文中定义α、β均等于1.Cmax为所选时钟单元的最大负载电容,可直接从工艺库时钟缓冲器参数说明中读取出来[16].

本文设计的寄存器聚类方法,另外两个重要的约束是组群的半径和组群内最大寄存器数目.组群半径定义为寄存器与所在组群中心之间的最大距离dmax,如公式(11)所示,根据定义,dmax等于D/2.结合公式(10),组群内最大寄存器数目Nmax如公式(12)所示.

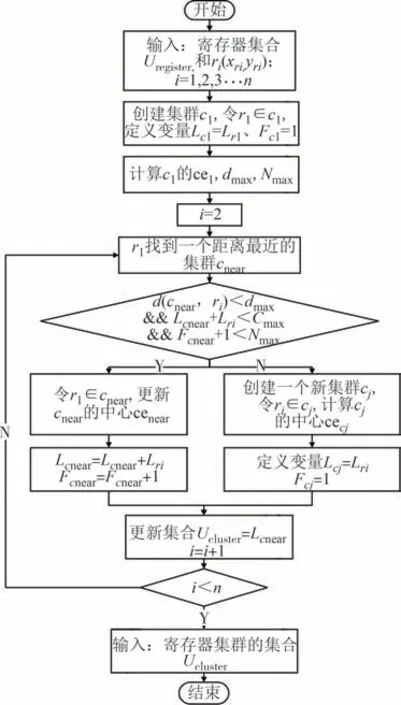

公式(11)中,W和L分别是布局的宽度和长度,S是布局上障碍物的总面积,Nall是寄存器的总数.公式(12)中,Cmax是所选时钟单元的最大负载电容,Crn是寄存器时钟端口的本征输入电容,N是组群内的寄存器数量,α、β为定义参数.算法流程图如图3所示.

图3 寄存器聚类方法流程图Fig.3 Flow chart of register clustering method

首先,该算法通过添加r1来生成第一个组群c1,定义此时组群的负载Lc1,组群的扇出为Fc1,计算c1的中心,组群半径dmax和最大扇出Nmax.然后,对所有剩余的寄存器进行遍历.对于每个寄存器ri,找到距离最近的组群cnear,且ri与cnear必须满足最大距离约束、缓冲器最大负载约束和最大扇出约束,如果存在一个cnear满足条件,则 将ri加入cnear,更新cnear的中心、扇出和组群内的电容.如果没有组群满足约束条件,则创建一个新的组群cj,定义cj的中心,、扇出和负载,然后加入组群集合Ucluster中,最后更新Ucluster.

3 实验结果与分析

本文研究的低功耗时钟树设计基于寄存器分组进行时钟树拓扑结构的构建,降低时钟网络功耗的同时,尽可能地减小寄存器分组对时钟树时序性能带来的影响.提出的寄存器聚类方法实验环境在Linux 操作系统下,使用C 语言实现,在相同的环境下,实现文献[7]所描叙的寄存器聚类方法.作为一个给寄存器分组的过程,将两种方法分别集成到传统的CTS 流程中,基于110 nm 物理工艺库GRACE11 LP,在被广泛应用于时钟树综合结果验证的 ISCAS89 基准电路上进行仿真验证[17],对比集成两种不同寄存器聚类方法的时钟树综合结果,并对不同情况下时钟树的功率耗散和时序性能进行对比分析.

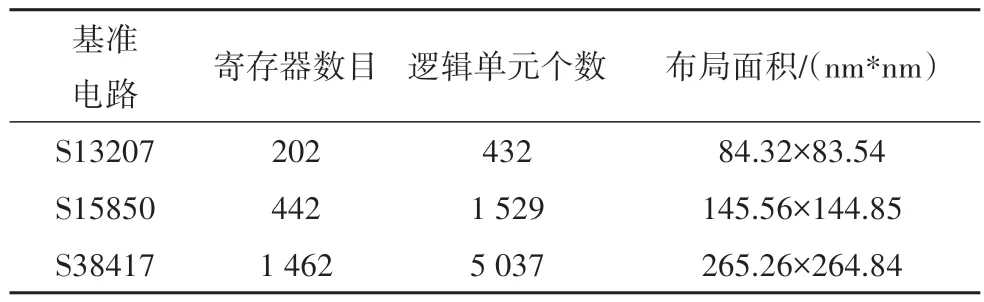

实验从ISCAS89 基准电路中选择了S13207、S15850、S38417 三个规模不同的单时钟同步电路结构,通过Design Compiler 逻辑综合工具,将电路的硬件描述语言形式翻译、优化并映射成对应的电路网表形式,然后通过Innovus 后端布局布线工具,实现所选用电路的时钟树综合等后端物理设计,将电路网表实现成可用于掩膜制造的 GDSⅡ版图.本次实验,定义时钟信号clk_period 为5 ns,input_delay 和output_delay 为0.1 ns,选用电路综合和布局后的信息如表1所示.

表1 基准电路信息Tab.1 Benchmark circuit information

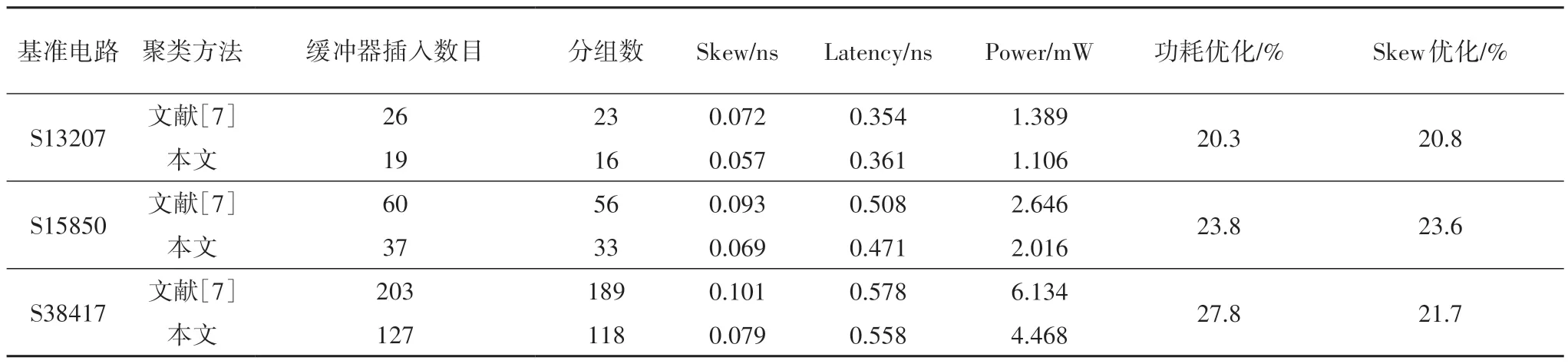

在Innovus 下采用集成两种不同寄存器聚类方法的时钟树设计流程,对表1 中三个基准电路进行时钟树综合,然后调用 StarRC 和 Prime Time,分别进行寄生参数提取和静态时序分析,分析不同情况下生成的时钟树的功率耗散和时序性能,如表2 所示,其中skew 表示全局最大时钟偏移(global skew),latency 代表最长路径延时,power 表示时钟网络的功耗.

表2 时钟树综合结果对比Tab.2 Comparison of comprehensive results of clock trees

表2 中,对比集成了文献[7]方法的时钟树综合结果,文中提出的寄存器聚类方法在基准电路S13207、S15850 和S38417 上,时钟网络的功耗分别降低了20.3%、23.8%和27.8%,时钟偏移分别减少了20.8%、23.6%和21.7%.最大延迟的偏差基本维持在50 ps的范围内,除在规模相对较小的S13207基准电路上有小幅度增加以外,其余两个基准电路下 latency 均有所优化.实验数据表明,本文研究设计的寄存器聚类方法,通过对时钟汇点进行更为有效的分组,合理增加并均衡了组群内的寄存器数目,减少了中心缓冲器的插入数目,在不影响时钟网络最大延时的条件下,有效减少了时钟网络的功率耗散和时钟偏移.

图4 和图5 显示了Innovus 图形界面下,文献[7]寄存器聚类方法和文中寄存器聚类方法在基准电路S38417 上生成的时钟树叶级拓扑结构,图中的每个树状拓扑结构都代表一个组群.

图4 文献[7]聚类方法分组结果Fig.4 Results of the clustering method grouping in the literature [7]

图5 文中聚类方法分组结果Fig.5 Results of clustering method grouping in the text

4 结论

高性能集成电路芯片设计中,时钟网络功耗在芯片总功耗中的占比较高,为了优化时钟网络功耗,本文提出了一种简单、高效的寄存器聚类方法.在满足叶级缓冲器最大负载电容和最大扇出约束的条件下,通过设置距离阈值控制组群的半径,将有限范围内的寄存器聚集成组生成时钟树叶级拓扑结构.基于110 nm物理工艺库GRACE11LP,将该方法集成到ISCAS89 基准电路三个不同规模的单时钟同步电路的时钟树综合流程中进行仿真验证,并与文献[7]对比,时钟网络的功耗分别降低了20.3%、23.8%和27.8%,时钟偏移分别减少了20.8%、23.6%和21.7%.仿真实验结果表明:该寄存器聚类方法在不影响时钟树最大延时的情况下,有效减少了时钟网络20%以上的功率耗散和20%以上的时钟偏移.

——以冶金企业为例