一种搭载FPGA 和AD9361 的软件无线电平台实现方法

禹永植,夏泽宇,刘宇

哈尔滨工程大学 信息与通信工程学院,黑龙江 哈尔滨 150001

随着电子技术的快速发展,无线通信技术也得到了不断的发展和进步,人们对无线通信的要求也来越高。传统射频收发器硬件架构使用低噪声功率放大器、混频器、可变增益放大器、数模/模数转换器、正交调制器和射频频率综合器等大量的分立器件,导致测控设备种类繁多、体积庞大,缺少统一的技术规范,设备管理和维护十分复杂,并且在有新的设计需求时,设备无法重复利用,更新的代价极大。因而小型化、低能耗、多功能、高集成度的无线通信系统成为了未来发展趋势[1]。为了满足这些要求,许多新的方案不断被提出,其中就包括软件无线电技术。软件无线电技术是将通信系统中射频前端电路实现为软件可控制、硬件可配置和高度芯片化的硬件平台,可利用更改配置的方式进行多种模式的通信,能够适用于各种通信方案及通信频带。

软件无线电技术的概念是由美国Joseph Mitola 博士提出的,目的是解决战争中的互联互通问题。1992 年,美国军方制定并推进了“Speakeasy”项目,目的是为实现电台之间不同通信协议下的数据交互。此项目获得阶段性成功后,陆续推进了“Speakeasy”项目第二、三期以及联合战术无线电系统(joint tactical radio system,JTRS)计划,把可编程通信领域的发展推向了新的阶段。经过了30 年的发展,软件无线电技术已获得了长足的进步,不仅应用于军事领域,也逐渐应用于日常生活的各个领域中。自高性能射频收发芯片AD9361 推出后,其便经常被用于以软件无线电概念为基础的通信平台中,其中国内的典型应用是姜浩等[2]设计的现场可编程门阵列(field programmable gate arrays,FPGA)+AD9361的软件无线电平台以及方良[3]设计的Zedboard开发板+AD9361 的视频传输系统,这2 个平台均使用AD9361 完成信息数据的无线收发来满足具体的应用需求,证明了AD9361 芯片具有良好的传输性能。

综上所述,针对如今无线通信系统对设备的体积、能耗以及系统功能多样性和集成度的要求[4],本文提出了一种搭载FPGA(KINTEX-7)和AD9361 芯片的软件无线电平台设计方案。此平台以FPGA 为系统主控制器,能够完成外部数据的基带处理过程,同时搭建MicroBlaze 嵌入式软核[5]作为处理器对AD9361 进行寄存器配置,使用手动增益控制(manual gain control,MGC)方式对收发通道进行发射功率、接收增益以及频点的控制,并经过多次更改参数进行收发测试。观测结果表明,该平台的通信性能够满足高集成度、多功能性的无线通信系统的应用需求。

1 AD9361 介绍

AD9361 是ADI 公司产出的一款高性能射频捷变收发芯片,芯片内部集成了各2 路接收器和发射器,它们彼此之间相互独立,每一路接收器或发射器都含有I、Q 这2 个独立通道,每个I 路或Q 路通道都是1 个直接变频系统,使用同一个频率合成器进行正交混频。对于发射器,其本机振荡器的工作频率为47 MHz~6.0 GHz;对于接收器,其本机振荡器的工作频率为70 MHz~6.0 GHz[6],AD9361 芯片发射器和接收器的工作频率范围涵盖了大部分常用通信频段,具有优秀的集成性能和通用性能[7]。AD9361 收发通道支持的带宽为200 kHz~56 MHz,并且具有较强的可编程性,可以根据具体工程配置芯片的工作频点和通道带宽[8−9]。

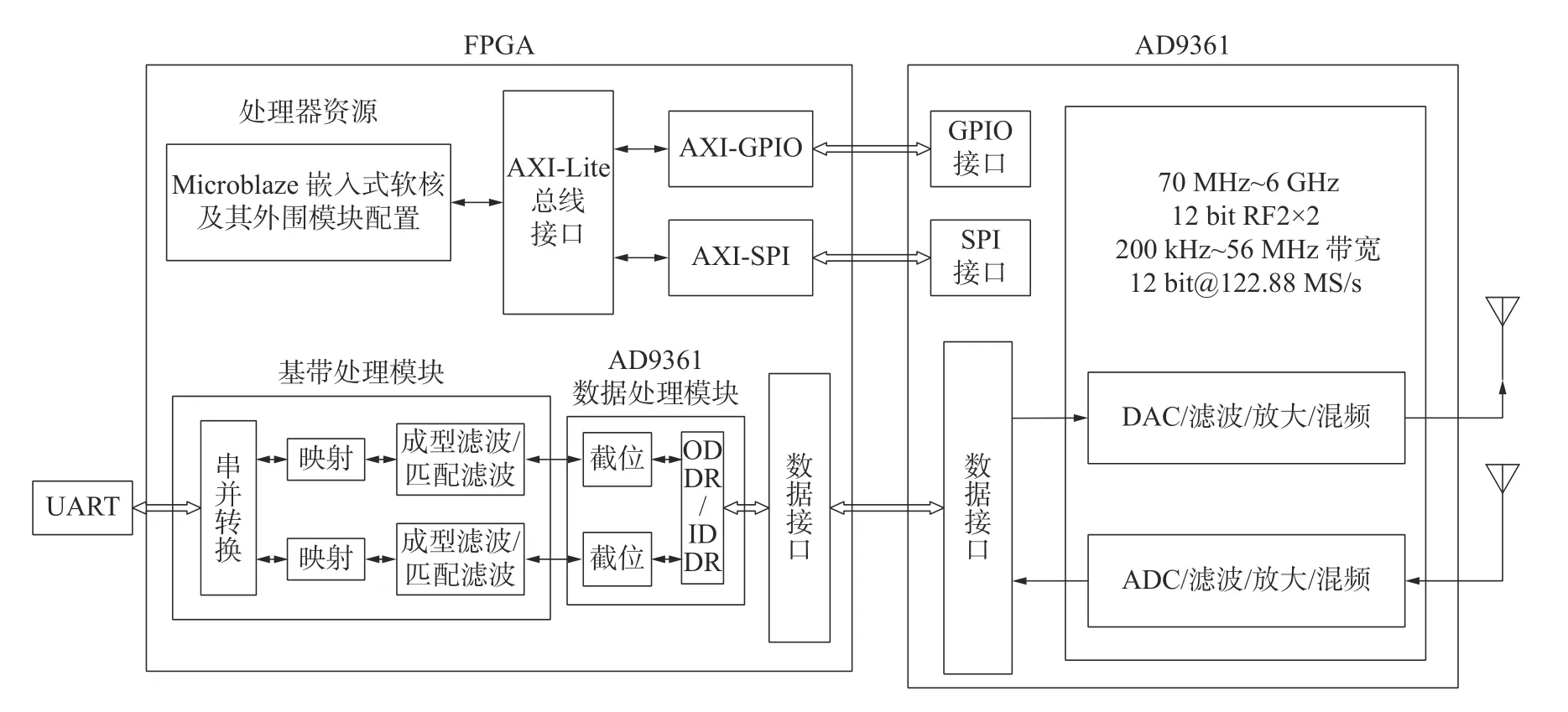

AD9361 芯片内部集成的发射子系统和接收子系统均具有自动增益控制功能[10],对于发射子系统,2 个独立的发射通道都具有数字滤波的功能,数字信号经有限冲击响应(finite impulse response,FIR)滤波、插值滤波后,送入芯片内部集成的12 位数模转换器(digital to analog converter,DAC),完成数字信号的模拟化,最终完成正交上变频并将I、Q 这2 路数据合并为1 路进行发射。对于接收通道,在对接收信号进行带通滤波及正交下变频等处理后,芯片内部集成的12 位模数转换器(analog to digital converter,ADC)将接收的模拟信号数字化,随后将信号通过抽取滤波和FIR 滤波后提供至基带处理模块[11],AD9361 内部数据处理如图1 所示。此外,AD9361 芯片具有手动增益控制功能,可对发射通道的发射衰减和接收通道的接收增益进行调节,开发者和使用者可借助此功能对通信系统的信噪比进行调整。

图1 AD9361 内部数据处理框图

2 搭载KINTEX-7 和AD9361 的软件无线电平台设计

本文基于KINTEX-7 和AD9361 实现通用软件无线电平台的设计,其中KINTEX-7 作为主控芯片,通过嵌入式微处理器MicroBlaze IP 核在FPGA 内部实现微处理器的构建,使FPGA 具有执行相应汇编和C 语言指令的功能,能够对AD9361 芯片进行各种收发通道参数的设置,并且能够实现AD9361 芯片与FPGA 基带数据处理模块之间的数据互通,实现了高集成度、高灵活性、可移植性强、多功能的无线通信设备的设计,软件无线电平台的系统框架如图2 所示。此软件无线电平台的设计指标如下:基带数据传输速率为200 Kb/s~10 Mb/s,可调谐通道带宽为200 kHz~56 MHz,通信频点可调工作范围为200 MHz~5 GHz,发射衰减支持范围为20~50 dB,接收增益支持范围为30~76 dB。

图2 软件无线电平台系统框架

软件无线电平台具有软件、硬件可编程性以及I/O 接口的可编程性,基于C 语言完成软件无线电平台正常工作所需的参数配置,并且能够使用高级可扩展接口(advanced extensible interface,AXI)总线完成MicroBlaze 软核处理器[12−13]和FPGA 之间的数据交互和逻辑功能互联[14]。

AD9361 芯片的数字接口有3 种,分别是串行外设接口(serial peripheral interface,SPI)、通用输入输出(general purpose inputoutput,GPIO)接口和高速数字接口,其中SPI 接口用于传输控制信息,GPIO 接口用于读取AD9361 的工作状态并对AD9361进行状态控制,高速数字接口用于和FPGA 之间传输基带数据。使用FPGA 的逻辑资源将GPIO、SPI 等各个功能模块组装成带有AXI 总线的知识产权(intellectual property,IP)核,并通过FPGA 的I/O 接口完成与AD9361 射频芯片之间信息数据的交互。

在发送阶段,数据源使用串口传输的方式在FPGA 的驱动下注入到基带处理模块,基带处理模块根据相应需求将数据进行串并转换、映射以及成型滤波等一系列操作,生成的基带信号通过高速数字接口传输至AD9361 芯片,AD9361 内部集成的DAC 将基带处理模块输出的信号转换为模拟信号,随后进行滤波、放大等操作,最后与预设频点对应的载波信号进行混频,将混频后的信号合并成1 路,通过天线进行发射。在接收阶段,外部天线接收的无线数据通过AD9361 内部集成的ADC 转换为数字信号,经混频、滤波、放大等操作后,将数字信号送入基带处理模块,基带处理模块对信号进行映射、并串转换,还原出信息数据。

3 开发流程

搭载KINTEX-7 和AD9361 的通用软件无线电平台的开发分为软件部分和硬件部分,2 部分分别使用C 语言和Verilog 语言进行设计和开发,并使用FPGA 作为主控芯片,进行软硬件部分的集成,最终完成软件无线电平台整个系统的搭建并进行仿真验证与逻辑优化,设计流程如图3所示。

图3 平台设计流程

软件无线电平台的软件部分主要由FPGA 内部集成的嵌入式软核MicroBalze 来完成,通过配置MicroBlaze IP 核完成软件部分处理平台的搭建,使用AD9361 Evaluation Software 2.1.3 软件生成AD9361 配置文件,并通过此嵌入式软核执行配置文件中相应的C 语言指令,完成对AD9361射频芯片的状态控制和参数配置。

软件无线电平台硬件开发的部分主要是对FPGA 芯片逻辑资源的使用,包括MicroBlaze 外围各IP 核的配置、基带数字信号处理模块的设计和开发以及AD9361 数据处理模块的设计和配置。根据FPGA 型号(KINTEX-7)对应的硬件资源对GPIO、SPI 和通用异步收发器(universal asynchronous receiver/transm-itter,UART)等Xilinx的IP 核进行开发,并根据AD9361 的接口类型将逻辑资源封装成带AXI 总线的功能IP。其中,带AXI 总线的GPIO 核完成AD9361 的状态控制,SPI 核完成寄存器配置,UART IP 核预留,用于后续功能的开发。由于AD9361 芯片的数据接口位宽为12 bit,因此在本平台的开发过程中,在FPGA 内部搭建AD9361 数字处理模块对数据进行截位处理,将数字基带处理模块输出的16 bit数据截取低12 bit,随后进行速率转换并输出至AD9361 完成软件无线电平台的射频功能。

4 功能验证

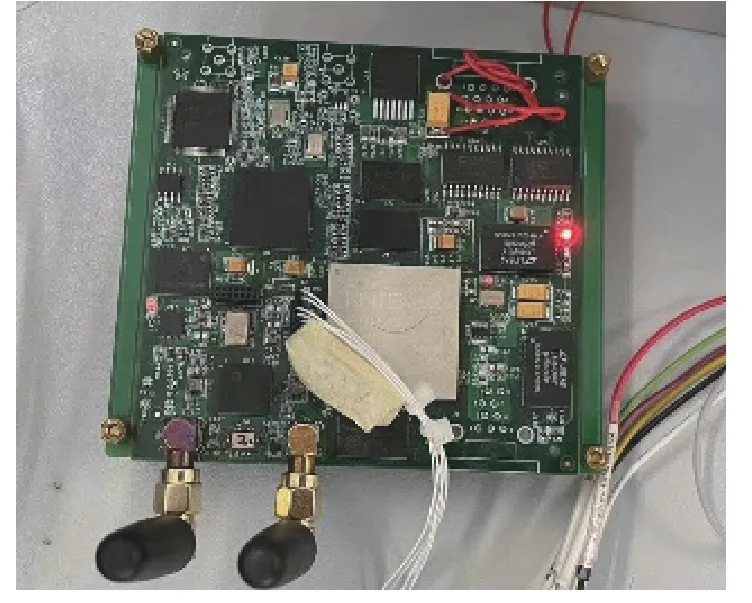

搭载KINTEX7 和AD9361 的通用软件无线电平台在方案设计上采用软硬件部分各自开发、协同调试的方式。在功能测试和验证过程中,可将平台的软件部分和硬件部分看作2 个独立设计,修改其中一个部分不会影响另外一个部分的正常工作,仅是改变了系统的基带处理类型或参数配置状况。例如,需要更改信息数据的处理方式时,仅需要修改硬件部分基带处理模块的编译文件,将需求的调制框架添加到系统中即可,无需更改其他模块的设计与处理流程;若需要更改AD9361 的参数配置状况,仅需修改软件开发套件(software development kit,SDK)平台下的配置文件,通过C 语言的编译即可达到更改AD9361 收发通道参数的目标,无需更改FPGA 逻辑资源的设计与使用。由于本设计软件、硬件部分的独立性和复用性,使得无线电平台具有高度的可编程性,在根据需要更改调制方式或参数配置时更加灵活、易操作,能够适应各种应用场景,图4 为搭载FPGA 和AD9361 的通用软件无线电平台。

图4 软件无线电平台

数字调制技术是现代通信的重要方法,其中相移键控(phase shift keying,PSK)将不同的码元用不同的载波相位来表示,是一种用相位表达信息的调制方式[15]。而正交相移键控(quadrature phase shift keying,QPSK)是多进制调制技术中比较常用的,它将每2 个信息比特组合成一个码元,可以看作是I、Q 这2 路正交的BPSK 调制信号相加之后得到的,在相同传输速率下,QPSK 调制系统的频带利用率更高。QPSK 信号可表示为

式中:g(t)为码元的时域信号波形,Ts为码元宽度,ωc为调制载波角频率, φn为第n个码元的基带信号代表的相位。若I、Q 这2 路正交信号分别表示为则有:

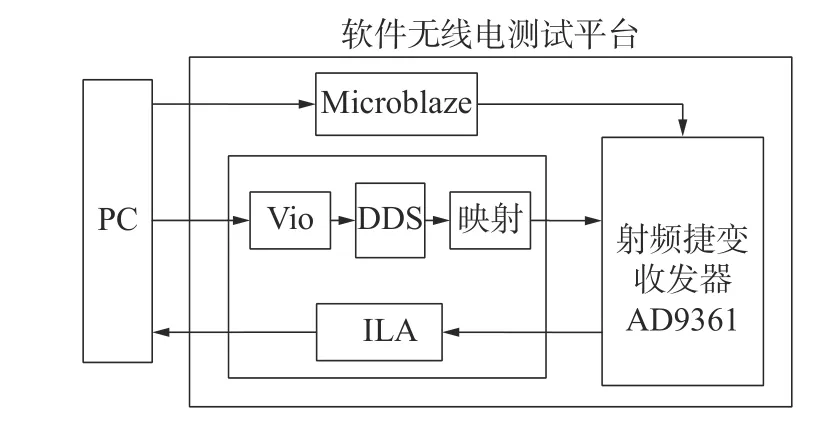

本文为验证软件无线电平台的功能是否满足设计要求,搭建功能验证平台框架。在PC 端使用AD9361 Evaluation Software 2.1.3 软件对AD9361进行硬件配置,选取类型为典型的LTE 5 MHz 标准,增益控制类型为MGC,生成配置文件,使用MicroBlaze 软核执行相应的指令,完成AD9361 的寄存器配置。同时,在PC 端通过Vivado 平台完成基带处理模块的设计及程序编译,使用Vio IP 核配置虚拟IO 接口进行频率控制字的写入,并通过DDS IP 核[16]产生载波信号。在本文功能验证过程中使用QPSK 调制方式生成I、Q 这2 路正交波形,经截位、速率转换处理后输出至AD9361 芯片,完成调制信号的自回环收发测试,并使用Vivado 平台的集成逻辑分析仪(integrated logic analyzer,ILA)抓取接收信号,并在PC 端进行信号的观测。功能验证平台框架如图5 所示。

图5 功能验证框架

在功能验证流程中,系统的参数初始值设置如下。DDS 频率控制字:028F[H];基带通信标准:LTE 5 MHz;基带传输速率:7.68 MHz;通信频点:200 MHz;发射衰减:30 dB;接收增益:50 dB。

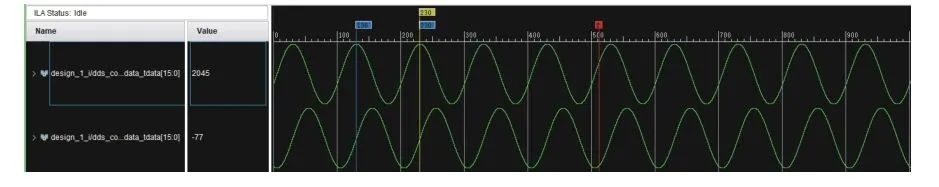

图6为数字基带处理部分输出的I、Q 这2 路波形信号观测图,图7 为经AD9361 发射并接收的信号波形观测图。

图6 输出波形

图7 接收波形

由信号观测图可以看出,本文设计的软件无线电平台具有良好的收发性能,接收信号的波形平滑,无明显毛刺出现,且峰值和谷值处无畸变,能够满足系统要求。为进一步验证系统性能,对不同工作频点进行多次收发测试,测试结果如表1所示。

表1 不同频点下的测试结果

AD9361 射频收发芯片收发通道的数据接口位宽均为12 bit,因此能够表示的数值范围为−2 048~2 047。根据测试结果可以看出,相对于发射信号,接收数据波形的峰值有所下降,这会对调制信号的解调产生负面影响。

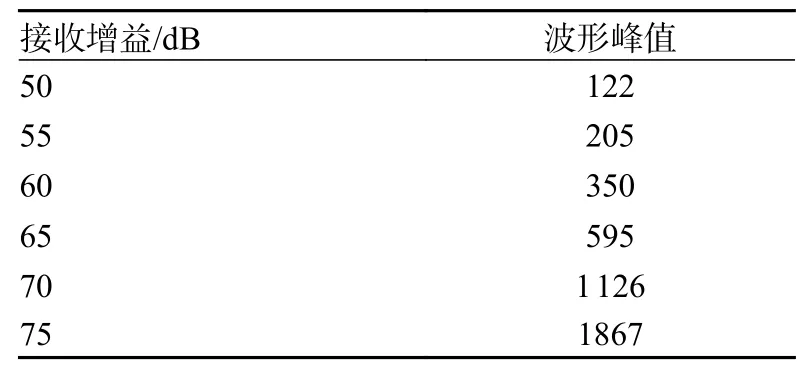

针对接收信号的峰值性能较差的问题,使用MGC 的方式更改收发通道参数进行测试。以3.5 GHz 频点为例,在发射衰减为30 dB、接收增益为50 dB 的参数下,接收信号波形的峰值性能较差。现固定发射衰减,更改接收增益的大小并观测结果,如表2 所示。

表2 3.5 GHz 频点下不同接收增益的测试结果

固定通信频点为3.5 GHz、发射衰减为30 dB的条件下,图8 为不同接收增益下的接收波形。能够看出,通过增大接收增益,接收信号的峰值有较大增加,在75 dB 下峰值能达到1867,达到发射通道信号峰值的90%以上,对系统传输性能有较大提高。

图8 通信频点3.5 GHz 时不同接收增益下的接收信号波形

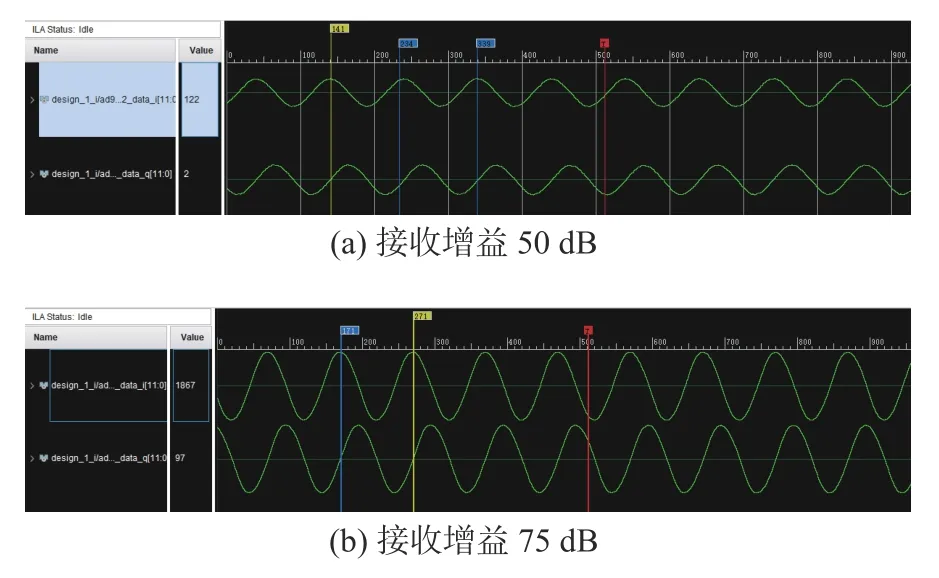

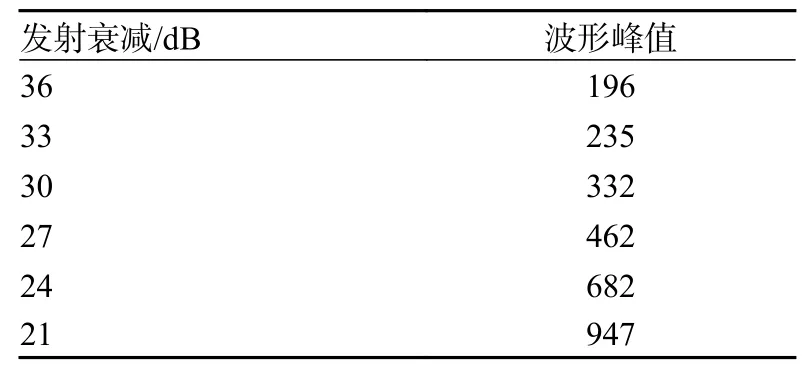

同样,以4.5 GHz 频点为例,在发射衰减为36 dB、接收增益为65 dB 的参数下,接收信号波形的峰值性能较差。固定接收增益,更改发射衰减数值并观测接收结果,如表3 所示。

表3 4.5 GHz 频点下不同发射衰减的测试结果

固定通信频点为4.5 GHz、接收增益为65 dB,图9 为不同发射衰减下的接收信号波形。能够看出,通过减小发射衰减,接收信号的峰值有较大增加,在发射衰减为21 dB 下,接收信号峰值能达到947。

图9 通信频点4.5 GHz 时不同发射衰减下的接收信号波形

综上,通过更改系统的收发通道参数,使得接收信号波形的峰值性有了较大改善,更加有利于接收数据的后续解调、译码等操作。

5 结束语

本文提出了一种搭载KINTEX-7 和AD9361的通用软件无线电平台的设计方法并进行了功能验证。该平台采用软硬件部分各自开发、协同调试的方式,使用MicroBlaze 嵌入式软核完成对AD9361 的状态控制和参数配置,并通过对FPGA内部逻辑资源的开发完成基带数据的处理,有效地减小了系统的电路体积。相较于传统的通信设备,本平台具有多功能、高灵活性等优势。此外,本文在功能测试阶段,通过MGC 方式调整收发通道的参数,进一步提高了通信性能,并为此平台后续的开发提供了数据支持。