基于PXIe总线的数字示波器现场高效校准系统

宋佳玲,李 建,高岩晶,郭伟民

基于PXIe总线的数字示波器现场高效校准系统

宋佳玲,李 建,高岩晶,郭伟民

(中国工程物理研究院计量测试中心,绵阳,621000)

为提高数字示波器现场校准效率,提出一种可并行校准5台1GHz及以下带宽的数字示波器的软硬件实现方法。按照GJB7691-2012对计量标准装置的要求,每个数字示波器校准通道均需具备直流电压、时标、稳幅正弦波和快沿脉冲4种基本信号输出功能和电阻测量功能。4种信号输出功能及电阻测量功能的模块设计、与被校数字示波器之间的通路设计以及并行校准软件设计是实现现场高效校准的重点。对校准装置的软硬件总体方案进行设计,对装置的主要功能模块实现方法以及并行校准软件设计方法进行了详细描述,设计并行按需校准、并行校准和串行校准试验,试验结果表明此方法可快速、高效地实现数字示波器的并行校准。

数字示波器;并行校准;开关拓扑;现场高效

0 引 言

数字示波器是应用最广泛的时域测量仪器[1]。在一些大型物理诊断平台或大型综合测试控制台中,示波器的4个采集通道通常不能满足测试需求,于是将数十甚至上百台数字示波器通过局域网组成数字示波器阵列测试系统,完成对大型试验装置众多电参数和物理参数的直接或间接的多通道准确测量,为物理诊断测试提供可靠、必要的依据。

目前的计量装置基本可以完成一定带宽范围内(20 GHz)数字示波器的全项目计量,但均采用单一逐台逐通道方式,即串行、单路的工作模式。此类计量装置可以由多台具备不同信号输出功能的分立设备组成,也可以由单台或少量集成度较高的综合多功能校准设备组成。从标准配置成本、使用便捷性和计量发展趋势看,后者是首选。国外主要产品有美国Fluke公司的5820A、9500B等多功能校准仪、美国泰克公司早期的TM504、CG5011等插件式或多功能集成校准设备。中国主要产品有江苏南锋公司的NF4608A、NF4609A、国营南华厂的SO3、SO6、NH4602(可程控)、中国计量院华电公司研制的POC-2(可程控)多功能校准仪以及中国航天科工集团有限公司研制的BM1302-1示波器校准仪等装置。

目前,美国Fluke公司生产的9500B多功能校准仪是指标最高、功能最全的多功能校准设备,集成度高,单台设备配接不同的有源探头可方便地完成 6.4 GHz带宽以下各类型数字示波器的计量,是国内外各计量机构在脉冲计量方面的主流配置[2],但是9500B受限于其内部的硬件结构,5个信号输出通道的主功能信号无法并行同步输出,计量过程仅能采取单通道逐一计量的方式进行,已经成为进一步提高多通道数据采集类设备计量效率的瓶颈问题,Fluke 9500B的计量保障能力和效率已不能满足成百上千采集通道的数字示波器阵列的需求。

为实现数字示波器阵列并行高效校准,本文提出一种基于PXIe总线的数字示波器阵列并行校准装置设计方案,该校准装置可对1 GHz及以下最多5台数字示波器同时进行校准,并且具有体积小、质量轻、集成度高、方便外出携带和现场移动、计量保障针对性强和计量效率高等优点。

1 软硬件总体设计方案

在一些大型示波器阵列测试系统中,需要现场开展原位校准的数字示波器数量多达100台,考虑数字示波器现场校准装置设备体积、质量、功耗以及实现的技术难度等因素,对5个数字示波器共25个校准通道,包括20个测量通道和5个外触发通道的并行校准装置的软硬件结构进行总体设计。

为完成数字示波器现场校准,依据规程要求[3],主要的校准项目包括直流增益和直流偏置、上升时间和时基、频带宽度和触发灵敏度、输入电阻等[4-5]。从实现上述校准项目的功能看,为满足校准装置有限信号及通路适应数字示波器阵列大量通道不同特性的要求,整个硬件系统应包含直流电压、时标、稳幅正弦波和快沿脉冲等4种基本信号的输出功能以及电阻测量功能,因此数字示波器校准装置必须具备直流电源模块、快沿脉冲信号模块和时标信号发生器模块、稳幅正弦信号发生器模块信号输出功能和数字多用表模块。

在各模块集成方面,由于PXIe系统具有抗干扰性强、高性能和可扩展性强等优点,在工业自动化测试领域应用非常广泛。可通过采用PXIe总线集成板卡的方式实现设备的模块化设计,通过集成板卡的不同功能方便地实现独立功能板卡的性能提升、功能和通道扩展以及仪器的系列化设计和生产。

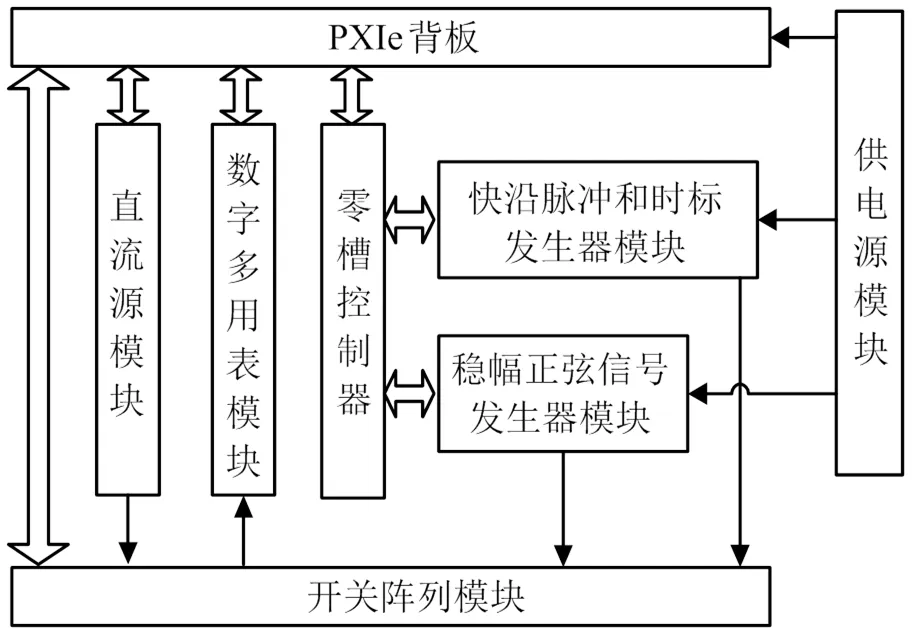

本装置采用PXIe总线技术进行设计,以装置小型化、集成化为目标,进行硬件系统总体结构设计。为保证信号的并行输出功能,将零槽控制器、5个直流电源模块、数字多用表模块和程控开关阵列模块集成至PXI、PXIe混合背板,考虑各模块的独立和可维护性,将快沿模块、稳幅正弦波模块通过串口与主机进行通信,最终将所有模块集成到一个带有12英寸液晶显示屏的定制机箱中。示波器阵列标准装置结构见图1。

图1 示波器阵列校准装置结构示意

在数字示波器校准过程中,直流增益和直流偏置项目校准点多、耗时长,为提升效率采用5路并行校准,硬件设计时通过5路直流源模块实现。外触发功能需要2路并行的稳幅正弦波信号进行校准,硬件设计为2路并行输出的稳幅正弦信号发生器模块,同时兼顾装置体积和质量。其余功能模块均为单路设计。

根据图1所示硬件系统框架,软件系统主要包括操作系统、数据库系统、各硬件模块驱动程序和数字示波器阵列自动校准软件系统4个部分。各硬件模块驱动程序为校准系统软件调用和仪器设置功能提供软件接口,并通过PXI总线协议完成硬件资源的分配和控制,数字示波器自动校准软件系统采用LabVIEW语言环境开发,采用并行校准技术实现数字示波器阵列的高效校准。

2 主要功能模块设计

2.1 功能模块指标设计

从实现上述功能的硬件装置看,示波器校准装置必须具备直流电源模块、快沿脉冲信号模块、时标信号发生器模块、稳幅正弦信号发生器模块和数字多用表模块测量输入电阻功能[6-7]。由于市面上已具有模块化的直流电源模块[8]、时标信号发生器模块和数字多用表模块产品,可直接在装置中进行集成。本文主要针对稳幅正弦波信号发生器模块和快沿脉冲信号输出模块进行具体设计,为满足1 GHz以下数字示波器校准功能,各模块设计指标如表1所示。

表1 数字示波器阵列校准装置功能模块技术指标

Tab.1 Technical specifications of functional modules of digital oscilloscope array calibration device

模块功能技术指标校准项目 直流信号输出1MΩ负载时±(3mV~100V),50Ω负载时±(3mV~5V),最大允许误差:±(0.2%+50μV)直流增益、直流偏置 正弦波信号输出频率1MHz~1GHz,5mV~5V,50Ω输出,平坦度优于±0.3dB频带宽度 快沿脉冲信号输出上升时间80~150ps,幅度6mV~3V触发灵敏度 时标信号输出周期1ms/10ms/100ms,最大允许误差:±1×10-6时基 电阻测量电阻:40Ω~2MΩ;最大允许误差:±0.15%输入电阻

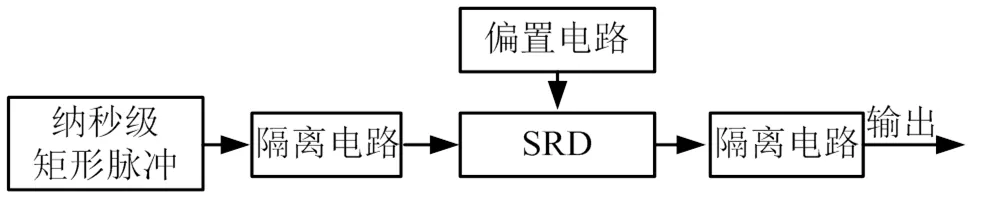

在快沿脉冲信号输出模块中,主要解决在纳秒级矩形脉冲基础上的脉冲整形技术,从而达到150 ps脉冲上升时间的设计指标要求。脉冲整形原理如图2所示,两个隔离电路阻止直流偏置电流进入输入和输出端。由于阶跃恢复二极管(Step Recovery Diode,SRD)具有大的存储时间和极小的暂态时间,根据其特性,只有当SRD的阻抗开始增加时,输出信号才开始上升,SRD截止时,输出信号便开始跟踪输入信号。因此,输出信号的上升时间减小后的值约等于SRD的暂态时间,从而达到整形目的。

图2 脉冲整形原理

在正弦波信号输出模块中,主要解决稳幅正弦信号产生技术。该技术的难点在于正弦信号的稳幅控制,在1 MHz~1 GHz内达到±0.5 dB的平坦度设计指标。通过稳幅电路控制和校准修正相结合的方法实现。综合考虑模块的功能和特点,对整个功能模块进行模块化设计,系统可以分为4个部分,由控制单元、时基、频率合成单元和幅度控制单元组成,如图3所示。

图3 稳幅正弦信号发生器模块原理

2.2 并行输出结构设计

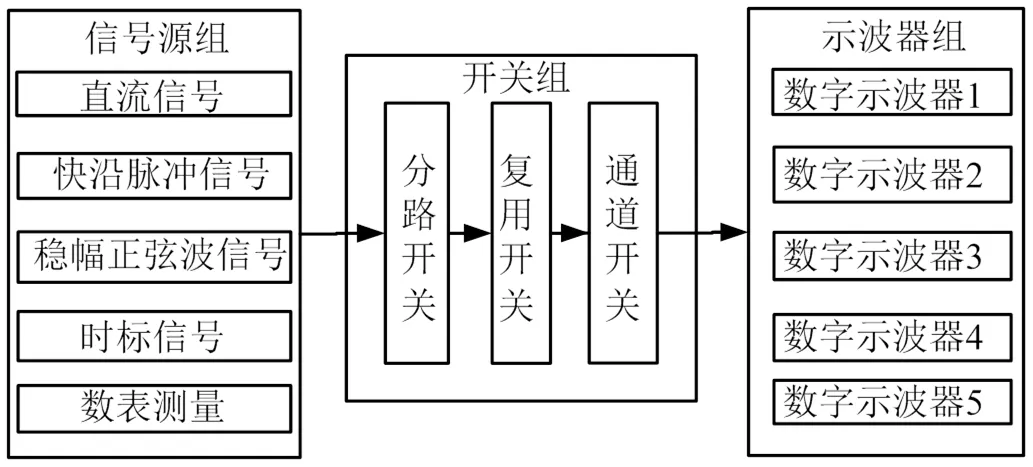

考虑示波器现场校准装置体积、质量、功耗以及实现的技术难度等综合因素,为实现5个数字示波器的并行校准功能,在计量装置内除了对信号源组进行设计外,还需对信号源组与被校数字示波器组之间的路由关系进行研究,即矩阵互联开关组的拓扑结构设计方法。其目标是实现信号源组,包括直流信号、快沿脉冲信号、时标信号、稳幅正弦波信号以及数表测量功能,通过矩阵开关组均能与所有被校示波器通道进行连接,实现自由切换。

经充分调研,选用5张射频开关卡实现上述功能。通过PXIe总线接口对射频开关卡进行控制,每张卡上有3个射频多路复用开关,采用“分-总-分”3层结构形式:第1层将信号通过分路开关分成5路;第2层将不同种信号汇总至一个开关;第3层将汇总后的信号分配至数字示波器的不同通道。标准装置信号源组与示波器组的路由结构如图4所示。

图4 数字示波器并行校准开关结构示意

3 并行校准软件设计

并行校准是指校准系统能同时完成多项校准任务的一种技术[9],包括一次同时对多个被测对象(Multiple Objects under Test,UUT)进行校准,或者同时运行一个UUT的多项校准任务,本文特指前者。区别于常规的串行校准,即在同一时刻只能对一个UUT进行校准,不同的UUT需要依次完成校准。以示波器为例,并行校准时各被校准示波器同设置、同采集、同读数。

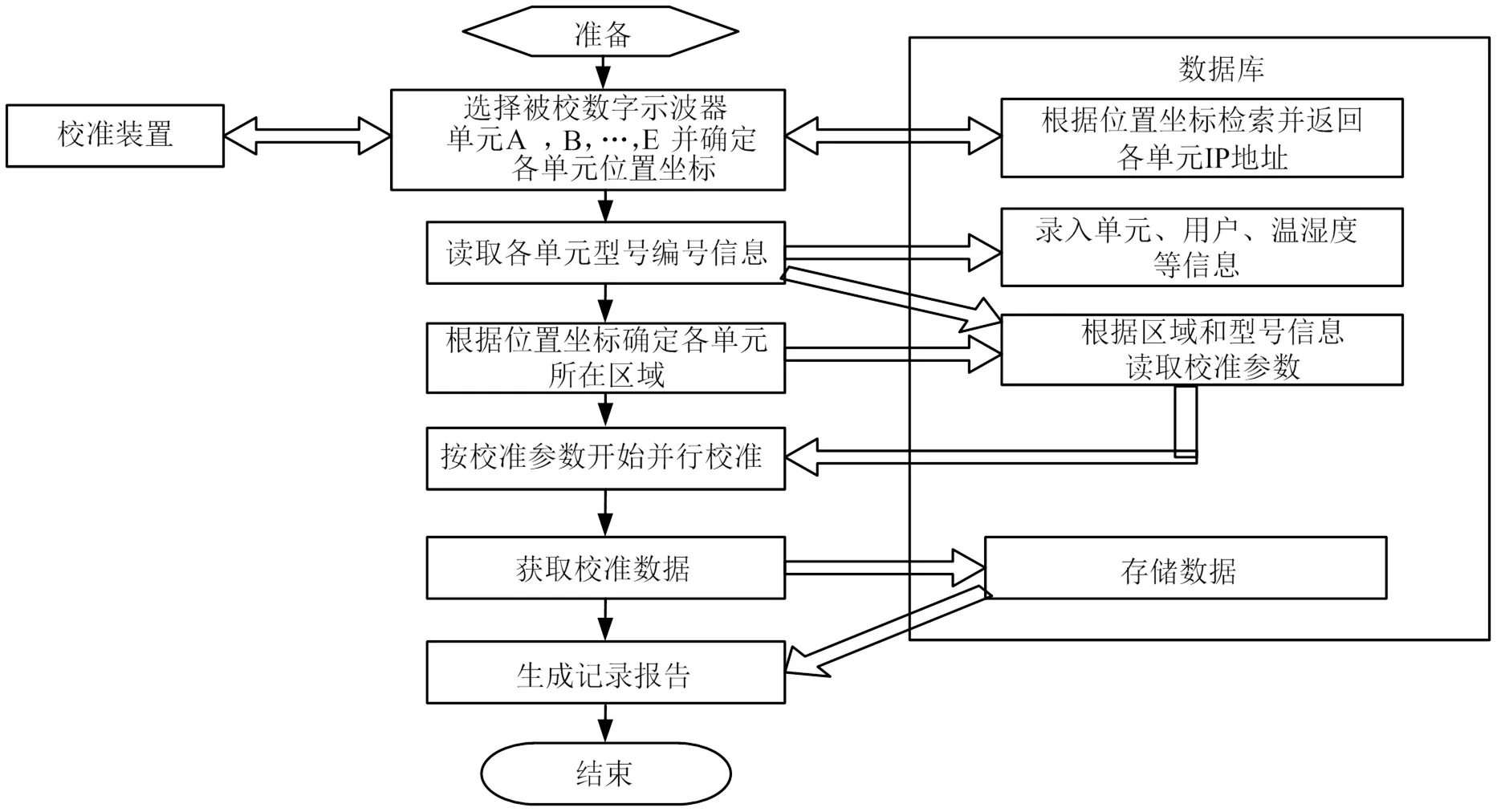

图5为数字示波器并行校准软件流程。校准装置在使用时与被校数字示波器连接,直流电压、快沿、稳幅正弦波、时标信号和电阻测量功能由对应的模块发出后,经过机箱内射频开关路由,通过线缆与被校准数字示波器连接,在控制器上运行数字示波器并行校准软件,各项目校准点及技术指标存储在系统数据库中,通过读取数据库的方式实现按需校准过程。由于环境温度对直流小电压信号的影响比较明显,因此在每次校准前,均需要对直流电压信号完成自校准保证信号指标满足要求。开关和线缆对稳幅正弦波和电阻测量功能的影响相对固定,可采用预修正的方式,在每个溯源周期内采用固定的修正值即可。

图5 数字示波器并行校准软件流程

数字示波器阵列并行校准的具体步骤为:

a)步骤1:校准装置与被校数字示波器预热。打开校准装置和被校准数字示波器开关,控制预热时间,对装置进行预热。预热完成后,数字示波器进行自检。

b)步骤2:直流电压信号自校准。预热完成后,依次将校准装置的5路示波器输出端的通道1连接至机箱背板上自校准端口,运行自校准程序,完成标准装置直流电压信号自校准,补偿环境对直流小电压信号的影响,保证线缆输出终端的直流电压信号满足技术指标要求。

c)步骤3:校准装置与被校数字示波器连接。在数字示波器阵列中选择待校准数字示波器,最多选择 5台,将数字示波器与校准装置信号输出端进行对应连接。

d)步骤4:校准装置对数字示波器校准。直流电压信号自校准完成后,按照选择的待校准数字示波器,在示波器阵列校准软件上进行设置,读取每台示波器的IP地址,确保校准装置与被校数字示波器通信正常。运行数字示波器阵列校准软件,读取数据库文件获得每台数字示波器的校准项目和校准点,依次按照校准项目和对应的校准点对5台数字示波器进行校准。

e)步骤5:校准完成后,保存校准结果,生成相应的原始记录与校准证书。关闭校准装置或继续对数字示波器阵列其他数字示波器进行校准。

4 校准装置功能及指标验证

4.1 校准装置功能验证

为验证数字示波器阵列校准装置功能,在试验现场选取5台具有代表性的DPO4054B作为验证对象。DPO4054B是典型的4通道500 MHz数字示波器,且同时具备高低阻功能,具备一定的代表性。选择数字示波器阵列一区的5个DPO4054B数字示波器单元为校准对象执行并行校准,和以往的顺序串行校准进行用时比较。设计如下2组试验:

a)第1组,并行、全项目校准和串行、全项目校准对比试验,以考核并行校准的效率提升;

b)第2组,并行、按需校准和串行、全项目校准对比试验,以考核并行、按需校准的综合效率提升。

试验结果显示2组试验的计量结果均符合被校数字示波器单元的技术指标要求,校准用时见表2,表2中计时为校准运行时间,不含校准前准备工作,如预热和数字示波器自校准时间。

表2 五单元并行和串行校准用时统计表

Tab.2 Five unit parallel and serial calibration time statistics

校准项目统计项目并行按需校准并行全项目校准串行全项目校准 直流增益校准校准用时/min1.719.618.5×5 校准点数8×5100×5100×5 直流偏置校准校准用时/min2.913.713.3×5 校准点数24×5120×5120×5 频带宽度校准校准用时/min5.023.67.8×5 校准点数8×540×540×5 触发灵敏度校准校准用时/min4.79.03.0×5 校准点数8×520×520×5 其他校准项目校准用时/min13.543.38.6×5 校准点数19×561×561×5 总用时/min27.8109.251.2×5 总校准点数69×5341×5341×5

如表2所示,对比并行、全项目校准和串行、全项目校准用时可以看出,以每5台数字示波器为一组对象,并行校准效率为串行校准的2.3倍。对数字示波器阵列一区的DPO4054B数字示波器而言,按需校准比全项目校准点数减少了80%,结合并行校准的实现,综合校准效率是原来的8.1倍,极大地缩短了校准用时。

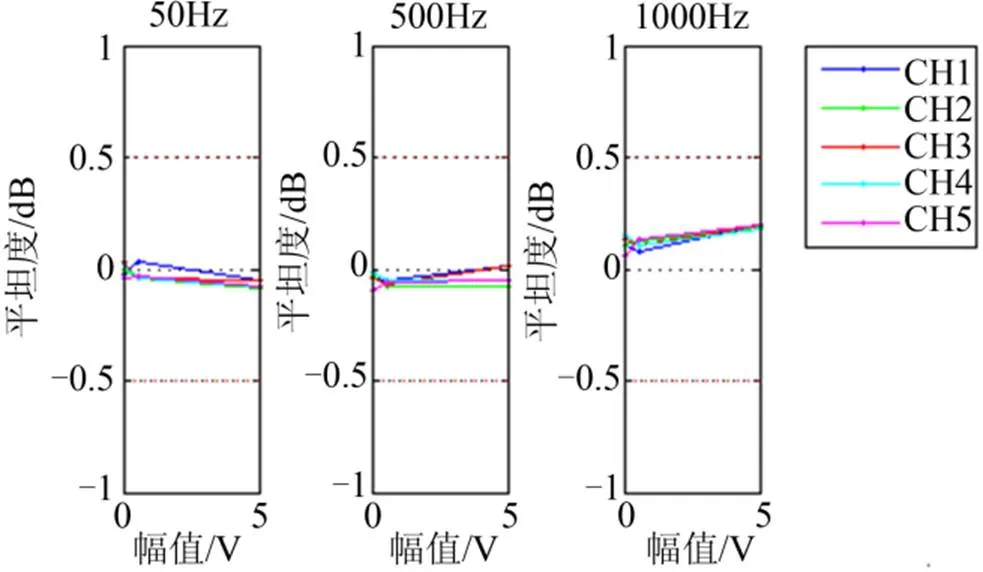

4.2 校准装置指标验证

采用检定(校准)法验证校准装置的主要指标,经试验,对该装置4种基本信号输出和电阻测量功能均进行了有效溯源,确认合格。稳幅正弦波信号的试验结果如图6所示。图6中,红色虚线为误差限,各通道实际校准结果均在误差限范围内,稳幅正弦波信号满足技术指标要求。

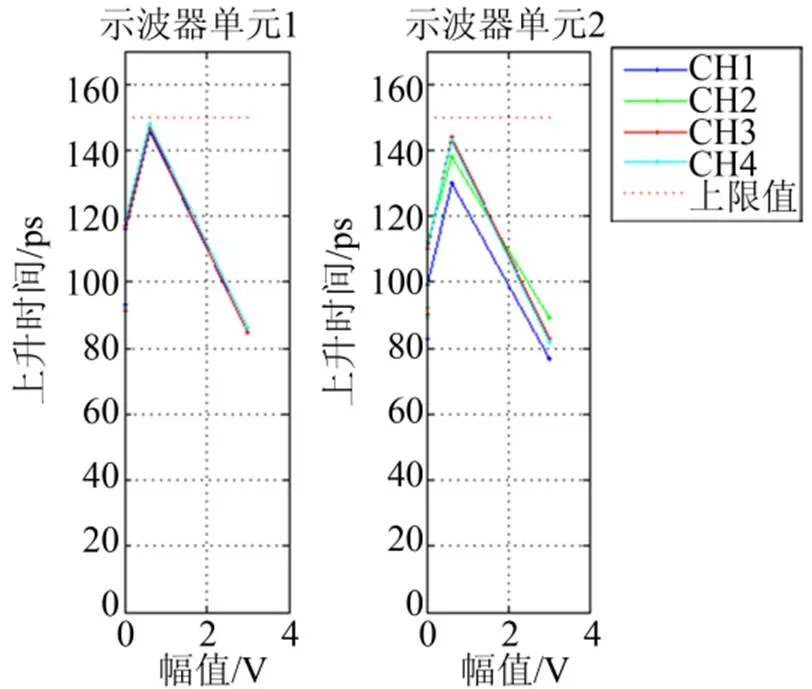

快沿信号的试验结果如图7所示。图7中,红色虚线为误差限,各通道实际校准结果均在误差限范围内,快沿信号的试验结果满足技术指标要求。

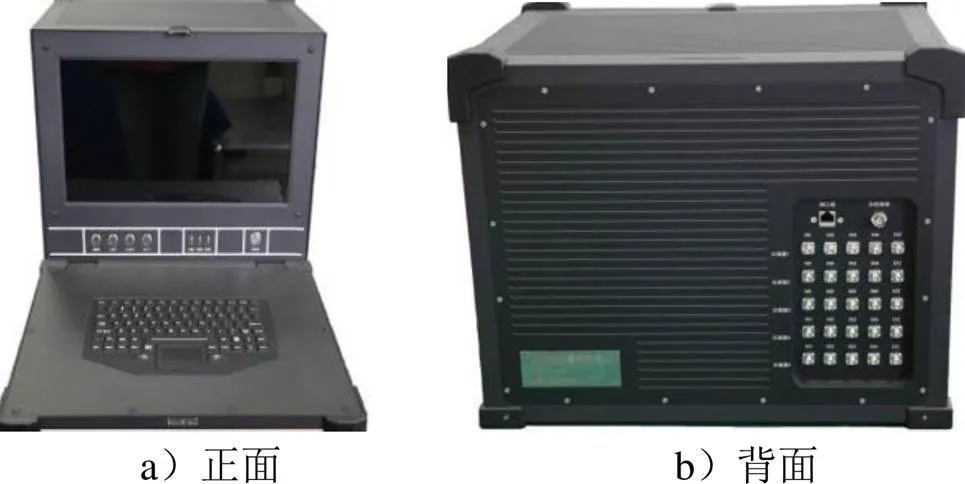

目前实验室已建立数字示波器阵列现场校准装置工作标准,装置如图8所示,经重复性、稳定性考核验证后,该装置可满足现场1 GHz以下数字示波器阵列并行校准的技术指标要求。

图6 校准装置稳幅正弦波信号试验结果

图7 校准装置快沿信号试验结果

图8 示波器阵列校准装置

5 结束语

本文针对数字示波器快速高效的校准需求,对数字示波器并行校准装置的软硬件设计方法进行了研究。首先,研究示波器阵列校准装置的总体结构设计,采用PXIe总线实现控制器、直流板卡以及数表卡之间的通信,为保障模块独立性采用串口实现控制器与快沿模块、稳幅正弦波模块的通信;其次,研究不同功能模块的具体实现方式,为保证5种信号与被校示波器之间的连接,研究了开关拓扑结构的设计方法,采用分-总-分三级开关实现了5种信号与被校示波器各通道之间的自由切换;最后,通过设计试验对校准装置的功能和性能进行了考核,经验证,通过开关切换,5个示波器共25个通道均可与不同的功能模块连接,实现了5个示波器的并行校准功能,并行按需校准比串行校准效率提升了8.1倍,本装置可完成数字示波器阵列的现场高效校准。

[1] 孙续. 电子示波器在挑战中发展[J]. 国外电子测量技术, 2009(3): 1-4.

SUN Xu. The development of electronic oscilloscope in the challenge[J]. Foreign Electronic Measurement Technology, 2009(3): 1-4.

[2] 冯慧娟, 匡志锋. 9500B示波器校准仪的功能与应用[J]. 硅谷, 2014, 7(24): 78, 232.

FENG Huijuan, KUANG Zhifeng. Function and application of 9500B oscilloscope calibrator[J]. Silicon Valley, 2014, 7(24): 78, 232.

[3] 邓晓莉, 郭伟民, 马红梅, 等. GJB 7691-2012数字示波器检定规程[S]. 北京: 总装备部军标出版发行部, 2012.

DENG Xiaoli, GUO Weimin, MA Hongmei, et al. GJB 7691-2012 Verification regulation of digital oscilloscopes[S]. Beijing: Military Standard Publishing and Distribution Department of General Equipment Department, 2012.

[4] 卢燕涛, 郁月华, 朱江淼, 等. 基于GPIB的数字存储示波器自动校准系统设计与实现[J]. 仪器仪表学报, 2007(S1): 93-95, 107.

LU Yantao, YU Yuehua, ZHU Jiangmiao, et al. Design and realization for digital store oscilloscope automatic cali brati on system based on GPIB interface[J]. Chinese Journal of Scientific Instrument, 2007(S1): 93-95, 107.

[5] 刘文刚, 常志方, 韩保, 等. 基于LabVIEW的数字示波器自动校准系统研究[J]. 通信世界, 2015(5): 97-98.

LIU Wengang, CHANG Zhifang, HAN Bao, et al. Research on automatic calibration system of digital oscilloscope based on LabVIEW[J]. Telecom World, 2015(5): 97-98.

[6] 方雪梅, 张晓博, 陈耀明, 等. 基于虚拟仪器技术的示波器校准仪设计[J].计量技术, 2005(11): 37-39.

FANG Xuemei, ZHANG Xiaobo, CHEN Yaoming, et al. Design of oscilloscope calibrator based on virtual instrument technology[J]. Metrology Science and Technology, 2005(11): 37-39.

[7] 梁志国, 孟晓风. 数字存储示波器的校准思想及技术述评[J]. 测控技术, 2007(26): 71-75.

LIANG Zhiguo, MENG Xiaofeng. Review on both the thought and technique of the calibration of digital storage ascilloscopes[J]. Measurement & Control Technology, 2007(26): 71-75.

[8] 范旭东, 张伟. 数字示波器直流增益计量检定探讨[J]. 计量与测试技术, 2021, 48(4): 94-95, 97.

FAN Xudong, ZHANG Wei. Disscussion on DC Gain measurement of digital oscilloscope[J]. Metrology & Measurement Technique, 2021, 48(4): 94-95, 97.

[9] 孔德仁, 何云峰, 狄长安. 仪表总线技术及应用[M]. 北京: 国防工业出版社, 2005.

KONG Deren, HE Yunfeng, DI Changan. Instrument bus technology and application[M]. Beijing: National Defense Industry Press, 2005.

Digital Oscilloscope Parallel Calibration System based on PXIe Bus

SONG Jialing, LI Jian, GAO Yanjing, GUO Weimin

(Centre of Metrology and Measurement, China Academy of Engineering Physics, Mianyang, 621000)

In order to improve the calibration efficiency of digital oscilloscopes, a software and hardware implementation method for parallel calibration of five digital oscilloscopes below 1GHz is proposed. According to the requirements of GJB 7691-2012 "verification regulation of digital oscilloscopes", each calibration channel of oscilloscopes should have four basic signal output functions: DC, time scale, amplitude stabilized sine wave, fast edge pulse and resistance measurements function. The module design of the four signal output functions and resistance measurement functions, the path design with the calibrated digital oscilloscope and the parallel calibration software design are the key points to realize the on-site efficient calibration. Firstly, the overall software and hardware scheme of the calibration device is designed. Secondly, the implementation methods of the main functional modules of the device and the design methods of the parallel calibration software are described in detail. Finally, through the design of parallel on-demand calibration, parallel calibration and serial calibration experiments, the experimental results show that this method can quickly and efficiently realize the parallel calibration of digital oscilloscopes.

digital oscilloscopes; parallel calibration; switch topology; field efficiency calibration

2097-1974(2023)02-0131-06

10.7654/j.issn.2097-1974.20230226

2022-08-22;

2023-03-16

TP311.52

A

宋佳玲(1990-),女,工程师,主要研究方向为计量测试技术。

李 建(1994-),男,工程师,主要研究方向为计量测试技术。

高岩晶(1983-),男,高级工程师,主要研究方向为计量测试技术。

郭伟民(1970-),男,高级工程师,主要研究方向为计量测试技术。