面向未来运载火箭的新一代综合电子平台设计与研究

王苑瑾,张 隽,2,段 然,2,韩翔宇,柳 柱

面向未来运载火箭的新一代综合电子平台设计与研究

王苑瑾1,张 隽1,2,段 然1,2,韩翔宇1,柳 柱1

(1. 北京航天自动控制研究所,北京,100854;2. 宇航智能控制技术国家重点实验室,北京,100854)

为满足运载火箭电气系统中智能控制、任务迁移与恢复、大数据量实时通信等需求,对多核处理器与SoPC协同控制架构、接口模块分类与设计、实时分区操作系统及双通道星型冗余拓扑等关键技术进行研究,提出了一种基于实时分区操作系统的综合电子平台方案并进行工程实现。通过演示验证试验,对综合电子平台中的功能模块、总线拓扑与通信、任务隔离、迁移与恢复等功能进行验证。目前该方案已应用于运载火箭综合电子产品中,为后续技术的深入研究与优化奠定了基础。

运载火箭;多核处理器与SoPC协同控制架构;接口模块分类与设计;实时分区操作系统;综合电子平台

0 引 言

运载火箭电气系统功能愈发复杂,对全系统资源优化设计、自主智能化的需求愈发迫切[1]。相比于传统运载火箭电气系统,未来运载火箭电气系统具有智能计算、任务迁移与恢复、大数据量高速通信、健康管理等功能需求[2],对运载火箭电气系统硬件与软件架构、总线传输带宽与拓扑等提出了更高要求,因此需要采用先进电气设计理念对全系统软硬件资源进行优化设计。

综合电子系统是目前国内外航天电气系统领域发展的趋势,具有高度综合化、标准化、模块化等特点。综合电子系统是一种基于高性能处理器的分布式实时计算系统,通过高速总线、标准接口实现传感器、子系统等信息交互,实现功能高度集成、软硬件资源共享,不仅缩小了软硬件规模、提高系统可靠性与维修性,还提升了系统模块化与标准化水平。

国外综合电子系统发展迅速,NASA在2010年研制的Orion电子系统采用综合电子架构,核心计算机与数据处理单元构成基本信息传输与处理设备,采用高速实时以太网实现数据交互。法国研制Avionics4000综合电子系统,具有供配电、数据管理等功能[3]。欧空局下一代运载火箭计划也提出了航天运载器综合电子系统架构,将传统电子设备抽象为一个模块化的信息处理单元,多个模块之间通过总线实现互联,构成各个分系统[4]。

中国运载火箭的电气系统普遍采用了主从式1553B总线的“惯性测量设备+计算机+各类控制器”分布式架构,以高可靠性要求为牵引,形成各具特点的冗余系统[5]。为了充分利用硬件资源,研究人员提出了系统集成和一体化设计的思想,但还未能实现系统集成设计[6]。

目前中国电气系统总线协议兼容性、站点数、通信距离、传输速度等方面均无法满足运载火箭大数据量实时传输需求[7]。处理器性能及架构也有待提高,以满足运载火箭智能控制算法、实时分区操作系统、任务迁移与恢复等功能需求。控制系统软件无操作系统或采用基于优先级的抢占式实时操作系统,内存均为静态分配,软件系统安全性、可靠性较差[8]。

借鉴国外综合电子系统的设计思路,并针对未来运载火箭电气系统需求进行研究与分析,本文提出了一种基于实时分区操作系统的综合电子平台方案并进行工程实现。对多核处理器与可编程片上系统(System-on-a-Programmable-Chip,SoPC)协同控制架构、接口模块分类与设计、实时分区操作系统、双通道星型冗余高速总线拓扑等技术进行分析与研究。通过演示验证试验,验证了综合电子平台的硬件模块、总线拓扑与高速通信、任务隔离、迁移与恢复等功能性能指标,对运载火箭的综合电子平台进行了探索和实践,为后续研究奠定了基础。

1 综合电子平台架构设计

1.1 综合电子平台功能分析

为满足运载火箭智能化、系统化、模块化要求,对电气系统应用需求、功能性能指标进行归类分析,优化硬件软件资源配置,实现具有标准化接口的综合电子系统。对系统中各功能项进行统计与分析,并转换为各个硬件与软件需求,如表1所示。

表1 功能项及需求

Tab.1 Function items and requirements

功能项硬件软件需求功能模块 惯组数据处理处理器与FPGA资源信息处理模块 智能控制算法处理器与FPGA资源信息处理模块 卫星导航算法处理器与FPGA资源信息处理模块 高速数据通信FPGA资源、总线协议与拓扑接口模块 遥测数据处理处理器与FPGA资源信息处理模块 传感器数据处理处理器与FPGA资源信息处理模块 时序输出及测试FPGA资源、控制及测试资源接口模块 模拟量测试FPGA资源、控制及测试资源接口模块 供配电及测试FPGA资源、控制及测试资源接口模块 故障隔离与重构处理器资源及分区操作系统信息处理模块

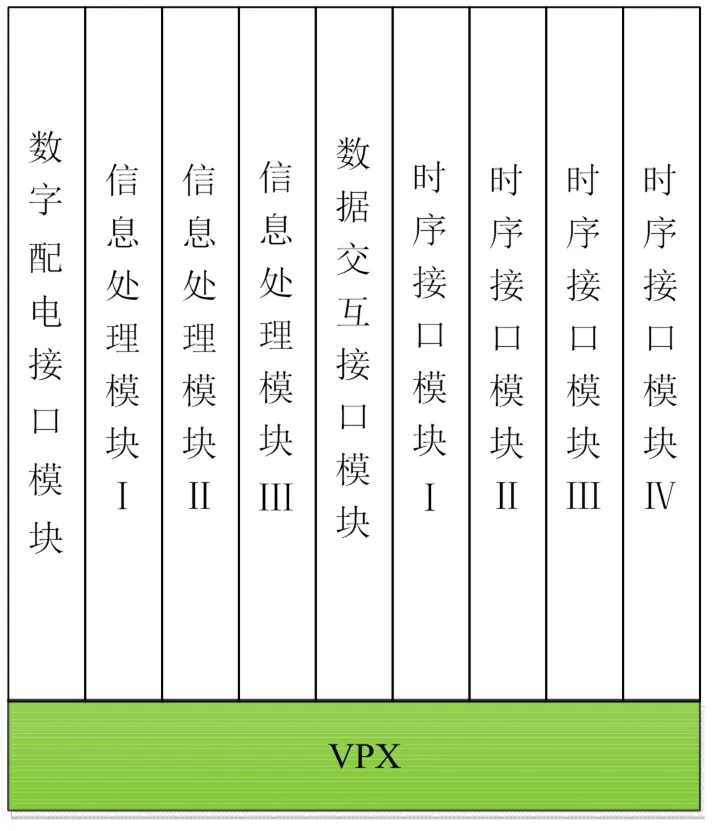

1.2 综合电子平台硬件方案

对表1进行分析,将控制系统应用需求映射至硬件功能模块,同时考虑最优化的软硬件资源配置,本文所述综合电子平台设计两类模块,即信息处理模块及接口模块,其中接口模块根据功能分为数字配电接口模块、数据交互接口模块、时序接口模块。综合电子平台模块组成如图1所示。

图1 综合电子平台模块组成

综合电子平台中各模块的主要功能包括如下4个方面:

a)3个信息处理模块对应处理器与FPGA资源,可以实现分区操作系统、数据处理、智能控制算法、卫星导航算法、故障隔离与重构、高速数据通信等功能;

b)数字配电接口模块对应FPGA资源、控制及测试硬件资源,实现配电指令解析,完成对各功能模块、系统内其他设备配电功能;

c)数据交互接口模块对应FPGA资源,实现数据转发功能,保证各个功能模块之间、模块与外部设备之间的高速通信功能;

d)时序接口模块对应FPGA资源、控制及测试硬件资源,实现时序指令接收与解析,完成控制与回采测试功能。

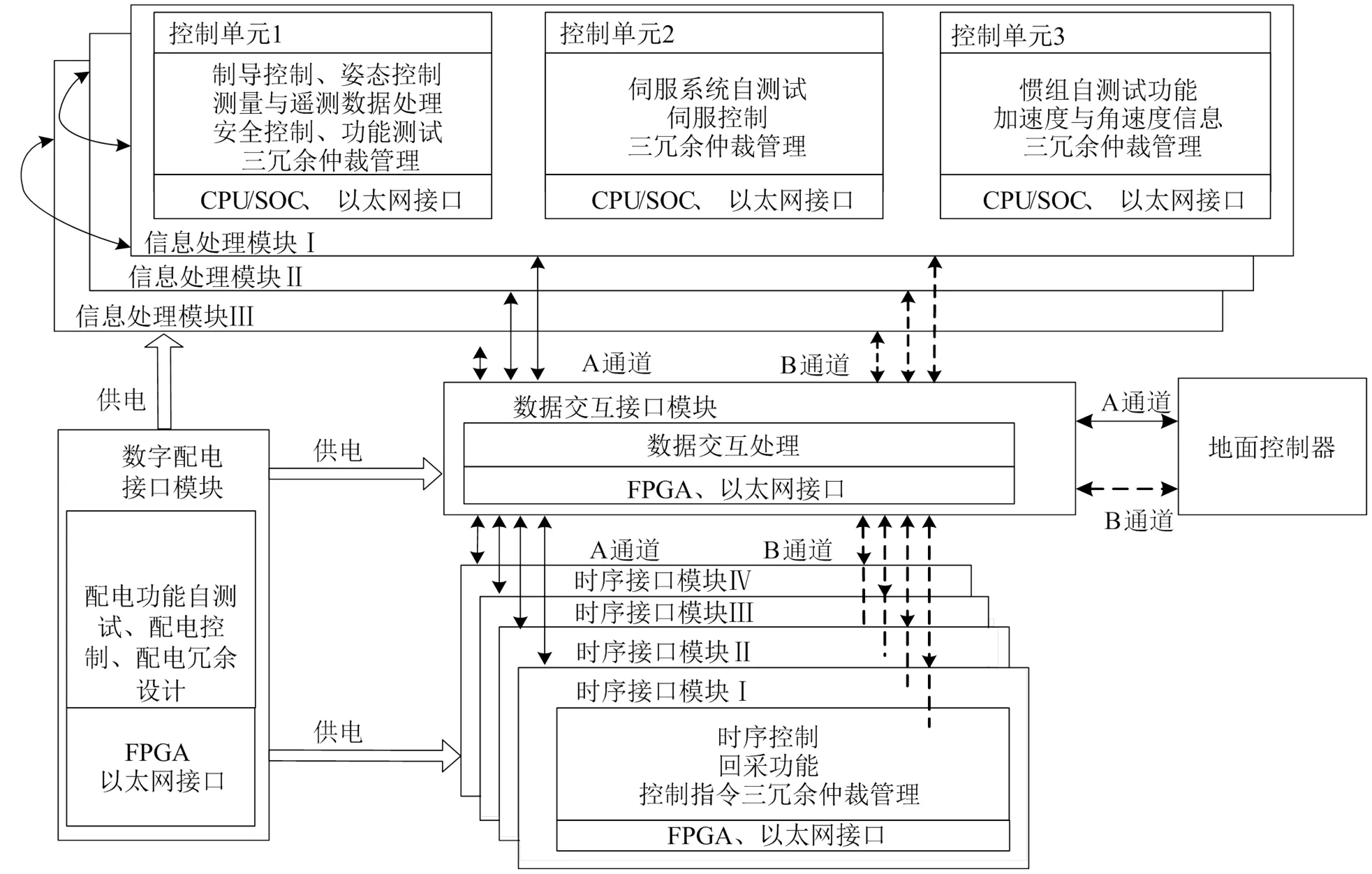

为了满足数据高速传输及高可靠性的设计要求,平台采用双通道星型冗余总线拓扑,以数据交互接口为冗余交换机的节点,以信息处理模块、时序接口模块、地面控制器等为端节点,用以实现模块之间、综合电子系统与地面控制器之间的高速通信功能。综合电子平台硬件架构如图2所示。

图2 综合电子平台硬件架构

2 综合电子平台关键技术

2.1 基于信息处理模块的协同控制架构

信息处理模块是综合电子系统的核心控制模块,采用具有内存管理单元(Memory Management Unit,MMU)的多核高性能处理器与SoPC以满足控制算法、分区操作系统及高速总线协议所需硬件资源。

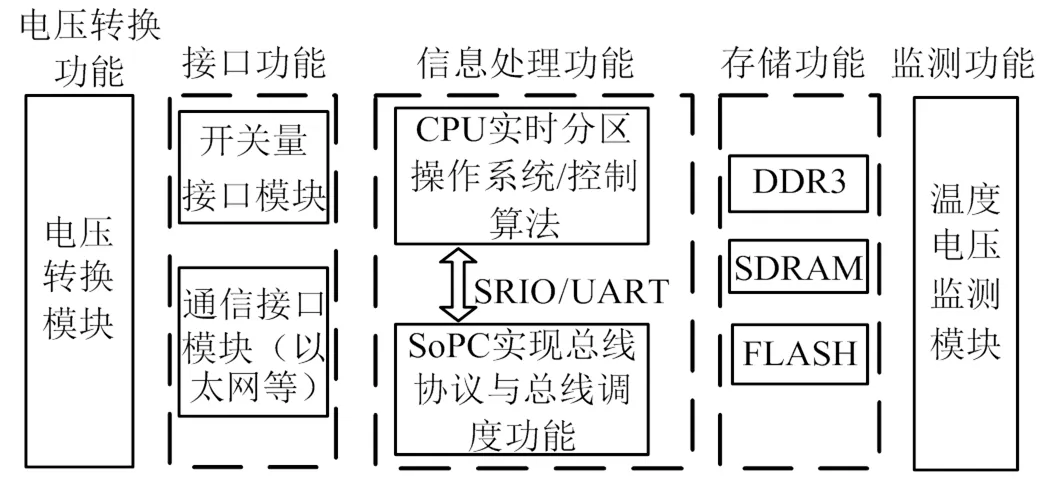

2.1.1 信息处理模块方案设计

本文设计的信息处理模块由3组控制单元组成,每个控制单元实现了信息处理、存储及监测、电压转换及接口功能,如图3所示。

图3 控制单元功能

各个功能具体实现方式如下所述:

a)信息处理功能,采用具有MMU的对称多核架构处理器(主频可达1 GHz),实现任务隔离迁移与重构、智能控制算法等。SoPC处理器实现高速实时以太网协议、网络通信调度管理、时间同步算法等功能。处理器与SoPC之间支持Rapid IO接口,可实现数据高速交互。

b)存储及监测功能,采用DDR3存储器,满足处理器与SoPC数据、图像等信息存储功能;通过温度传感器与电压采集模块,对高功耗芯片的工作温度与电压进行实时监测。

c)电压转换功能,通过DC-DC方式对数字配电模块的输出电压进行采集整形滤波及电压转换,为模块内各功能单元提供工作电压;

d)接口功能,设计紧急断电等关键信号的开关量输入接口、422通信接口及以太网通信接口等,以满足与测发控系统、其他子系统之间通信功能。

2.1.2 多核处理器与SoPC协同控制架构

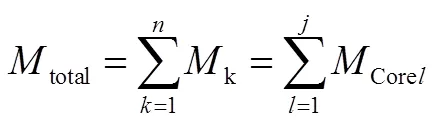

信息处理模块采用多核处理器与SoPC协同控制架构,在多核处理器上设计实时分区操作系统,根据功能需求及故障管理策略进行分区设计,实现多任务并行计算、故障隔离与迁移等功能。在考虑硬件资源开销等因素的前提下,从功能需求角度进行分类,设计若干个应用程序。由于应用程序功能是相对独立的,可根据应用程序数量确定分区数量,从而保证每个应用程序可以在指定分区中运行。根据应用程序划分个分区(1,…,P),每个分区执行的任务数为(1,…,M),操作系统会根据处理器工作状态及任务优先级,将任务分配至不同的处理器核,每个核上运行任务总数为Core1,…,Corej,完成的任务总数为total:

同时设计一个备份分区实现任务恢复功能,当某个任务对应分区故障时,操作系统会启动备份分区,完成后续控制任务。

SoPC芯片实现以太网通信协议栈、时钟同步算法、通信调度管理机制等功能。通过调度表方式,实现与用户层软件之间的接口。处理器通过Rapid 接口将控制参数发送至SoPC,SoPC中软件将接收消息进行分类,按照预先设定通信时隙实现数据实时高速传输。

依托于高性能多核处理器与SoPC协同控制架构,将软硬件资源配置最优化,既提高了大数据量计算与处理速度、软件安全性与可靠性,又满足大数据量高带宽实时传输的要求。

2.2 接口模块分类与设计

根据第1.1节所述,对功能需求进行梳理,将接口模块根据功能分为数字配电接口模块、数据交互接口模块及时序接口模块3类。

a)数字配电接口模块。

数字配电接口模块提供配电接口,将输入1路一次母线转换为6路二次母线。该模块接收数据交互模块发送的控制指令,并通过FPGA算法对控制指令进行解析与表决,完成对6路配电开关的控制,开关电路采取并联冗余方式,提高接口模块可靠性。

b)数据交互接口模块。

数据交互接口模块实现了综合电子系统内部各模块间及与外部其他设备之间数据交互功能,可支持16个端节点之间相互通信。为了提高通信可靠性,采用2个FPGA及其对应接口电路实现支持A、B通道的双冗余转发机制。当端节点之间发送消息时,数据将会通过A、B通道被转发,接收端节点根据消息校验位对数据正确性进行判别,将冗余消息进行丢帧处理。

c)时序接口模块。

时序接口模块作为控制系统时序开关控制节点,对安全性要求较高。该模块设计了3个FPGA芯片,基于FPGA芯片实现控制指令接收与解析、三取二判决及时序状态回采功能。3个FPGA之间设计数据交互接口,如图4所示。控制流程如下所述:a)FPGA1将从A通道接收控制指令,并根据校验位判断控制指令是否正确;b)若正确,则分别通过通道①③将控制指令转发至FPGA2与FPGA3,同时FPGA3不转发其通过通道B收到的控制指令3)若错误,则丢弃该控制指令,并通过通道①③将“健康诊断消息”发送至FPGA2与FPGA3;c)FPGA3收到该信息,则将由通道B收到的控制指令通过通道②③转发至FPGA1与FPGA2。通过硬件冗余实现控制通路的冗余,防止一度故障时时序误动作,很大程度上提高了安全性。

图4 时序接口模块硬件示意

2.3 实时分区操作系统设计

2.3.1 分区及任务绑定

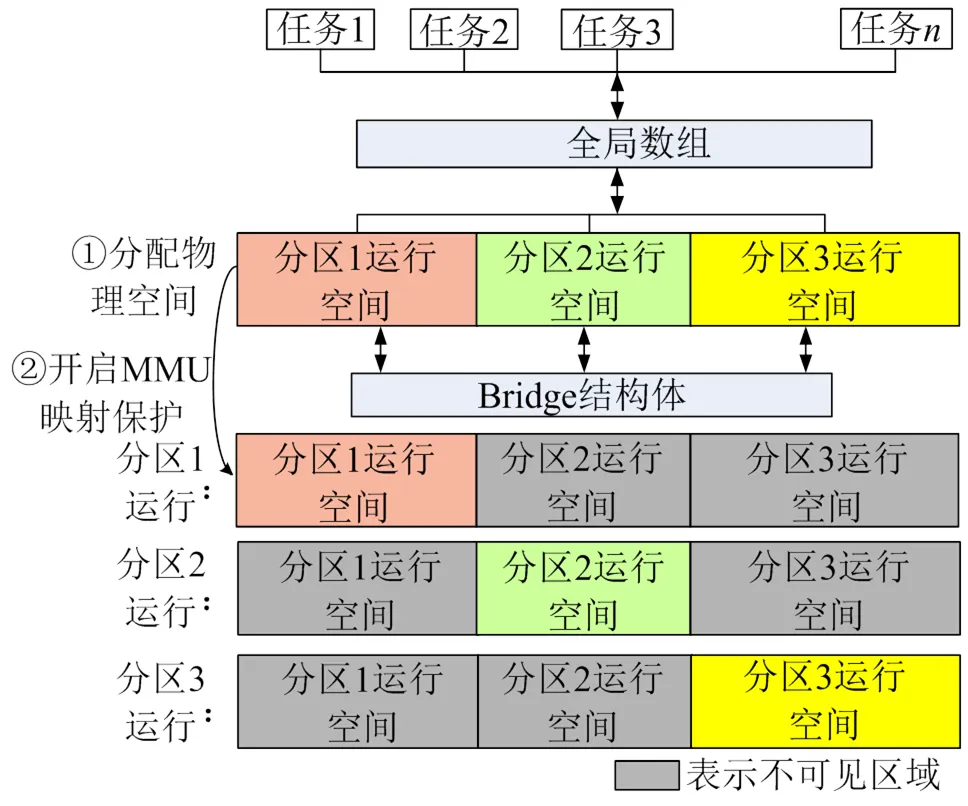

分区操作系统是基于第2.1.2节所述多核处理器而实现,操作系统将不同分区对应内存中不同物理地址,通过MMU实现虚拟地址和物理地址映射及保护,保证分区间的物理隔离性,为任务故障隔离奠定基础。分区及任务绑定示意如图5所示。

图5 分区及任务绑定示意

操作系统为上层应用程序提供了分区创建、初始化、任务与分区绑定等接口。创建任务时,通过一个全局数组来实现任务与分区绑定。不同分区中的任务通过Bridge结构体访问系统资源、调用系统函数,Bridge结构体中设计了系统函数接口、共享变量、自定义函数接口等,该方式提高了软件系统的安全性和可靠性。

2.3.2 基于多核处理器的任务调度策略

本文所设计的操作系统采用内存屏障、原子操作、自旋锁3种同步互斥机制,协调多核间并行任务,避免共享变量与资源、内核数据结构等遭到破坏,保证临界区的互斥访问及共享数据的可重入性,在确保系统正确性与完整性的前提下,提高计算效率。

基于全局队列模型的任务优先级抢占策略,操作系统会维护一个全局任务就绪队列,所有就绪任务都进入该队列等待。调度器根据处理器各个核工作状态及任务优先级,唤醒最高优先级任务。基于软件亲和性原则,将唤醒任务优先分配至它上一次运行的处理器核,减少任务在核间迁移开销。全局队列模型能有效解决多核系统负载平衡问题。

3 试验方案设计

基于前文所述的综合电子平台架构,本章设计了演示验证试验方案,对综合电子系统总线拓扑、模块间高速通信、实时分区操作系统、故障隔离与恢复等功能进行验证。

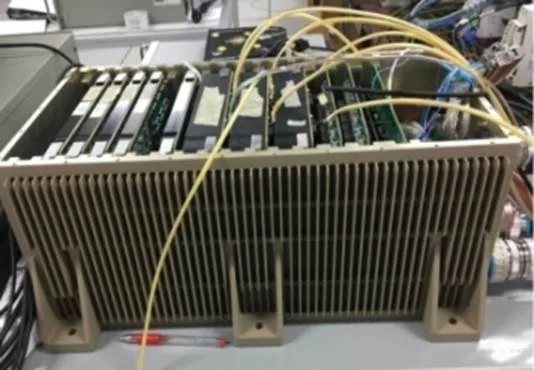

验证平台由信息处理模块Ⅰ、Ⅱ、Ⅲ,数据交互接口模块,时序接口模块Ⅰ、Ⅱ、Ⅲ、Ⅳ,数字配电接口模块组成,采用双通道星型冗余拓扑架构。通过信息处理模块模拟三冗余箭机、伺服控制器、惯组的功能,平台实物如图6所示。

图6 综合电子平台实物

在本设计中,信息处理模块Ⅰ、Ⅱ、Ⅲ中9个控制单元设置为端节点,选取3个时钟精度较高的控制单元作为箭机1、2、3(SM0、SM1、SM2),并提供全网同步时钟源,其他6个控制单元节点为被同步的端节点。时序接口模块设置为被同步的端节点,数据交互接口模块为中心交换节点,各个节点名称及所属硬件模块如表2所示。

SM0、SM1、SM2发送本地时间同步帧至数据交互接口模块,数据交互接口模块获取时钟信息,经过固化压缩产生修正后的本地时钟,并将修正后的同步帧以16 ms周期发送至端节点SM0~SM2,SC3~SC12,实现全网同步。根据功能模块之间数据流,设计了16路虚链路,具体如表3所示。

表2 节点名称及分配表

Tab.2 Types of node name and allocation

节点名称网络节点名称所属硬件模块 箭机1SM0信息处理模块Ⅰ 箭机2SM1信息处理模块Ⅱ 箭机3SM2信息处理模块Ⅲ 伺服控制器1SC3信息处理模块Ⅰ 伺服控制器2SC4信息处理模块Ⅱ 伺服控制器3SC5信息处理模块Ⅲ 惯组1SC6信息处理模块Ⅰ 惯组2SC7信息处理模块Ⅱ 惯组3SC8信息处理模块Ⅲ 时序接口模块Ⅰ控制器SC9时序接口模块Ⅰ 时序接口模块Ⅱ控制器SC10时序接口模块Ⅱ 时序接口模块Ⅲ控制器SC11时序接口模块Ⅲ 时序接口模块Ⅳ控制器SC12时序接口模块Ⅳ 交换机CM数据交互接口模块

表3 网络节点类型分配情况表

Tab.3 Types of network node

虚拟链路源端目的端意义 SN0SC3SM0、SM1、SM2伺服1→箭机1、2、3 SN 1SC4SM0、SM1、SM2伺服2→箭机1、2、3 SN 2SC5SM0、SM1、SM2伺服3→箭机1、2、3 SN 3SM0SC6、SC7、SC8箭机1→惯组1、2、3 SN 4SM1SC6、SC7、SC8箭机2→惯组1、2、3 SN 5SM2SC6、SC7、SC8箭机3→惯组1、2、3 SN 6SM0SC9、SC10、SC11、SC12箭机1→时序1、2、3、4 SN 7SM1SC9、SC10、SC11、SC12箭机2→时序1、2、3、4 SN 8SM2SC9、SC10、SC11、SC12箭机3→时序1、2、3、4 SN 9SC6SM0、SM1、SM2惯组1→箭机1、2、3 SN 10SC7SM0、SM1、SM2惯组2→箭机1、2、3 SN 11SC8SM0、SM1、SM2惯组3→箭机1、2、3 SN 12SC9SM0、SM1、SM2时序1→箭机1、2、3 SN 13SC10SM0、SM1、SM2时序2→箭机1、2、3 SN 14SC11SM0、SM1、SM2时序3→箭机1、2、3 SN 15SC12SM0、SM1、SM2时序4→箭机1、2、3

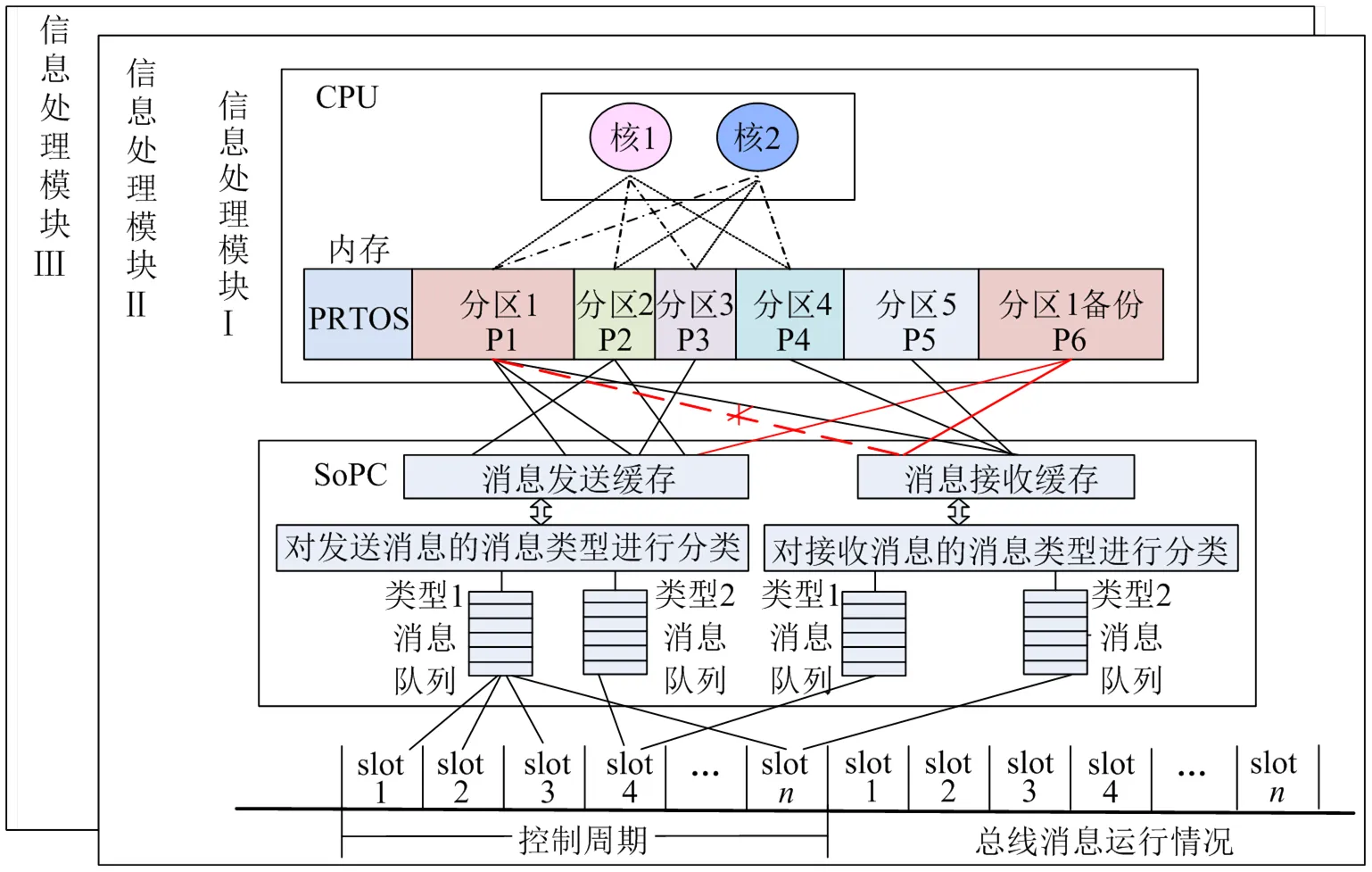

实时分区操作系统运行在箭机1、2、3处理器上,即SM0、SM1、SM2端节点中。根据应用程序功能,设计6个分区,每个分区上创建一个或多个任务,不同分区映射至不同内存空间,实现物理隔离。针对分区1设计备份分区,备份分区会周期性更新并保存数据。当分区1出现故障时,立即对分区1进行隔离,并初始化与启动备份分区运行,实现故障隔离与恢复,分区情况如表4所示。

表4 分区情况统计

Tab.4 Statistical of partition

分区号应用程序功能 分区1(P1)箭机接收惯组数据,并处理数据 分区2(P2)箭机实现控制算法,根据计算结果向时序接口模块发送控制命令 分区3(P3)箭机接收伺服控制器消息,并处理数据 分区4(P4)箭机实现控制算法,根据计算结果向伺服控制器发送控制命令 分区5(P5)箭机接收时序回采结果,并处理数据 分区6(P6)同分区1任务(备份分区)

信息处理模块中箭机1、2、3任务分区及通信方案如图7所示。在多核处理器上,运行基于分区操作系统的任务,在SoPC上运行实时以太网通信协议。当任务需要发送消息时,处理器与SoPC进行数据交互,SoPC会根据消息帧头信息,将消息进行分类,分类后的消息会进入对应的消息队列。根据预先设定的调度表,SoPC根据不同消息类型时槽发送消息至数据交互接口模块,由该模块转发至目的地址对应端节点。

当信息处理模块接收数据交互模块转发的消息时,消息由SoPC接收,SoPC根据消息类型将消息分配至不同队列,同时SoPC向处理器发送中断,通知处理器读取消息。

图7 信息处理模块分区与通信方案

4 试验结果分析

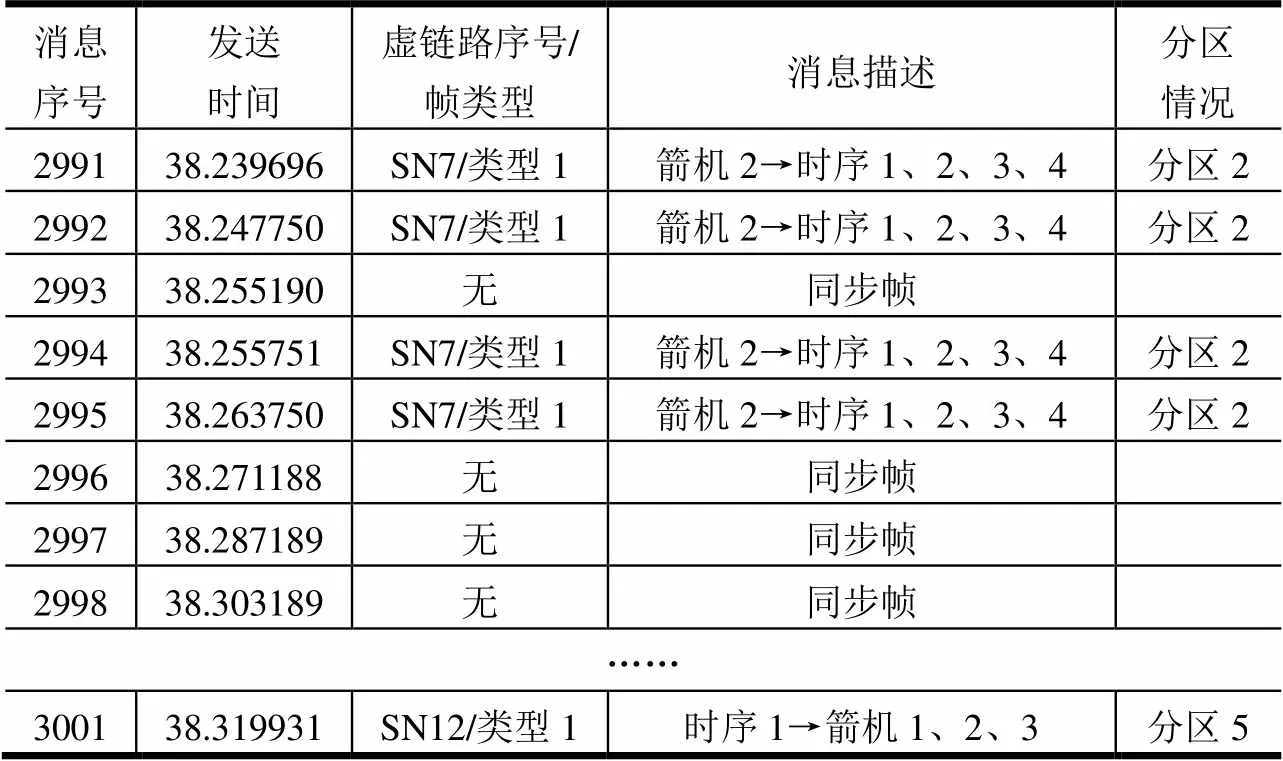

根据上述试验方案开展试验,通过对总线消息进行监测与记录,针对典型数据进行统计,消息情况统计及任务迁移及恢复情况统计分别如表5与表6所示。表5中,以消息序号为2993、2996、2997、2998同步帧消息为例,根据时间戳计算,以16 ms为周期对全网进行时钟同步,与设计值一致;序号为2671-2675、2978-2982、2991-2995的消息为SN6、SN7、SN8虚链路消息。由表5可以看出,当箭机连续向时序接口模块Ⅰ、Ⅱ、Ⅲ、Ⅳ发送消息时,发送消息周期为8 ms,与设计值一致。由表5与表6可以看出,不同任务在预先分配的分区1~5运行,与表4中的设计值一致;由表6可以看出,在消息序号为2724的消息处,分区1出现故障,将分区1进行隔离,任务迁移至备份分区6,并正常运行,箭机能够正常接收惯组数据,完成了任务迁移与恢复功能。

表5 消息情况统计

Tab.5 Statistical of messages

消息序号发送时间虚链路序号/帧类型消息描述分区情况 267134.415777SN6/类型1箭机1→时序1、2、3、4分区2 267234.423776SN6/类型1箭机1→时序1、2、3、4分区2 267334.431264无同步帧 267434.431777SN6/类型1箭机1→时序1、2、3、4分区2 267534.439750SN6/类型1箭机1→时序1、2、3、4分区2 …… 297838.095794SN8/类型1箭机3→时序1、2、3、4分区2 297938.103803SN8/类型1箭机3→时序1、2、3、4分区2 298038.111193无同步帧 298138.111794SN8/类型1箭机3→时序1、2、3、4分区2 298238.119739SN8/类型1箭机3→时序1、2、3、4分区2 …… 278535.871445SN0/类型1伺服1→箭机1、2、3分区3 ……

续表5

消息序号发送时间虚链路序号/帧类型消息描述分区情况 299138.239696SN7/类型1箭机2→时序1、2、3、4分区2 299238.247750SN7/类型1箭机2→时序1、2、3、4分区2 299338.255190无同步帧 299438.255751SN7/类型1箭机2→时序1、2、3、4分区2 299538.263750SN7/类型1箭机2→时序1、2、3、4分区2 299638.271188无同步帧 299738.287189无同步帧 299838.303189无同步帧 …… 300138.319931SN12/类型1时序1→箭机1、2、3分区5

表6 任务迁移及恢复情况统计

Tab.6 Statistical of task migration and recovery

消息序号发送时间虚链路序号/帧类型消息描述分区情况 270934.887912SN9/类型1惯组1→箭机1、2、3 分区1 271034.887913SN10/类型1惯组2→箭机1、2、3分区1 271134.888071SN11/类型1惯组3→箭机1、2、3分区1 …… 272335.023790SN5/类型1箭机2→伺服1、2、3分区4 272435.031913SN9/类型1惯组1→箭机1、2、3 分区6 272535.031914SN10/类型1惯组2→箭机1、2、3分区6 272635.032077SN11/类型1惯组3→箭机1、2、3分区6

5 结束语

本文对未来运载火箭电气系统需求进行研究与分析,设计了一种双通道星型冗余总线拓扑的综合电子平台,基于该平台对多核处理器与SoPC协同控制架构、实时分区操作系统、接口模块的分类与设计、高速通信等技术进行研究及工程实现。通过演示验证试验,模拟三冗余箭机、伺服控制器、惯组、配电、时序等功能,验证了信息处理模块及接口模块、高速通信、总线拓扑、任务迁移与恢复等功能。对运载火箭综合电子平台进行了探索和实践,为后续运载火箭综合电子平台的深入研究奠定了基础。

[1] 柳嘉润, 巩庆海, 翟雯靖. 智能自主系统及其航天控制应用[J]. 飞控与探测, 2018, 1(1): 59-62.

LIU Jiarun, GONG Qinghai, ZHAI Wenjing. Intelligent autonomous system and its aeropace control applications[J]. Flight Control and Detection, 2018, 1(1): 59-62.

[2] 马卫华, 包为民, 禹春梅, 等. 关于“航天智能控制系统”的认识[J]. 航天控制, 2019, 37(5): 4-8.

MA Weihua, BAO Weimin, YU Chunmei, et al. Understanding of aerospace intelligent control system[J]. Aerospace Control, 2019, 37(5): 4-8.

[3] 郝燕艳, 潘瑞, 万小磊. 基于TTEthernet的综合电子系统通信网络研究[J]. 航天器工程, 2013, 22(6): 86-91.

HAO Yanyan, PAN Rui, WAN Xiaolei. Research of integrated avioonics communication network based on TTEthernet[J]. Spacecraft Engneering, 2013, 22(6): 86-91.

[4] 刘伟伟, 程博文, 汪路元, 等. 一种分布式航天器综合电子系统设计[J]. 航天器工程, 2016, 25(6): 86-93.

LIU Weiwei, CHENG Bowen, WANG Luyuan, et al. Design of distributed spacecraft avionics system[J]. Spacecraft Engneering, 2016, 25(6): 86-93.

[5] 宋征宇. 新一代运载火箭电气系统体系架构的研究[J].载人航天, 2016, 22(3): 317-322.

SONG Zhengyu. Research on avionics system configuration of next generation launch vehicle[J]. Manned Spaceflight, 2016, 22(3): 317-322.

[6] 孙海峰, 刘俊阳, 程胜, 等. 面向下一代运载火箭的综合电子系统集成技术[J].宇航学报, 2019, 40(3): 334-344.

SUN Haifeng, LIU Junyang, CHENG Sheng, et al. Integration technology of avionics for next-generation launch vehicle[J]. Journal of Astronautics, 2019, 40(3): 334-344.

[7] 宋征宇. 考虑成本效率的航天运输系统研制[J]. 航天控制, 2015, 33(6): 3-11.

SONG Zhengyu. The study on the development of cost-effective launch vehicle[J]. Aerospace Control, 2015, 33(6): 3-11.

[8] 宋征宇. 嵌入式实时操作系统在运载火箭中的应用研究[J]. 航天控制, 2013, 31(3): 3-10.

SONG Zhengyu. The application study on embedded real-time operation system in launch vehicle[J]. Aerospace Control, 2013, 31(3): 3-10.

[9] 胡海峰, 宋征宇. 航天运载器飞行控制电子产品可靠性与成本分析[J]. 导弹与航天运载技术, 2018(6): 65-70.

HU Haifeng, SONG Zhengyu. Reliability and cost analysis of electronic products of flight control for aerospace vehicles[J]. Missiles and Space Vehicles, 2018(6): 65-70.

Design and Research of New Generation Integrated Electronic Platform for Future Launch Vehicle

WANG Yuanjin1, ZHANG Jun1,2, DUAN Ran1,2, HAN Xiangyu1, LIU Zhu1

(1. Beijing Aerospace Automatic Control Institute, Beijing, 100854;2. Science and Technology On Aerospace Intelligent Control Laboratory, Beijing, 100854)

In order to meet the requirements of intelligent control, task migration and recovery and real-time communication of large amounts of data for the launch vehicle electrical system, the key technologies of Multi-core CPU and SoPC collaborative control architecture, classification and design of interface modules, real-time partition operating system, and dual-channel redundancy topology are researched. An integrated electronic platform based on real-time partition operating system is proposed and implemented. Through the experiment, functional performance such as hardware module, high-speed communication, network topology, task migration and recovery is verified. At present, this system is applied to the integrated electronic products for heavy launch vehicle, which is providing technical support for the optimization and development of technology in the future.

launch vehicle; multi-core CPU and SoPC collaborative control architecture; classification and design of interface modules; real-time partition operating system; integrated electronic platform

2097-1974(2023)02-0058-07

10.7654/j.issn.2097-1974.20230212

TP353

A

2020-05-19;

2020-07-23

王苑瑾(1985-),女,高级工程师,主要研究方向为嵌入式系统设计、控制系统综合设计。

张 隽(1987-),女,高级工程师,主要研究方向为智能自主系统设计。

段 然(1976-),男,博士,研究员,主要研究方向为控制系统综合设计。

韩翔宇(1982-),男,研究员,主要研究方向为软件开发与测试技术。

柳 柱(1976-),男,研究员,主要研究方向为高性能计算与嵌入式系统技术。