基于嵌入式的多路视频流硬解码装置设计*

姚 宇 任勇峰 袁延荣 陈建军

(1.中北大学电子测试技术重点实验室 太原 030051)(2.空间物理重点试验室 北京 100076)

1 引言

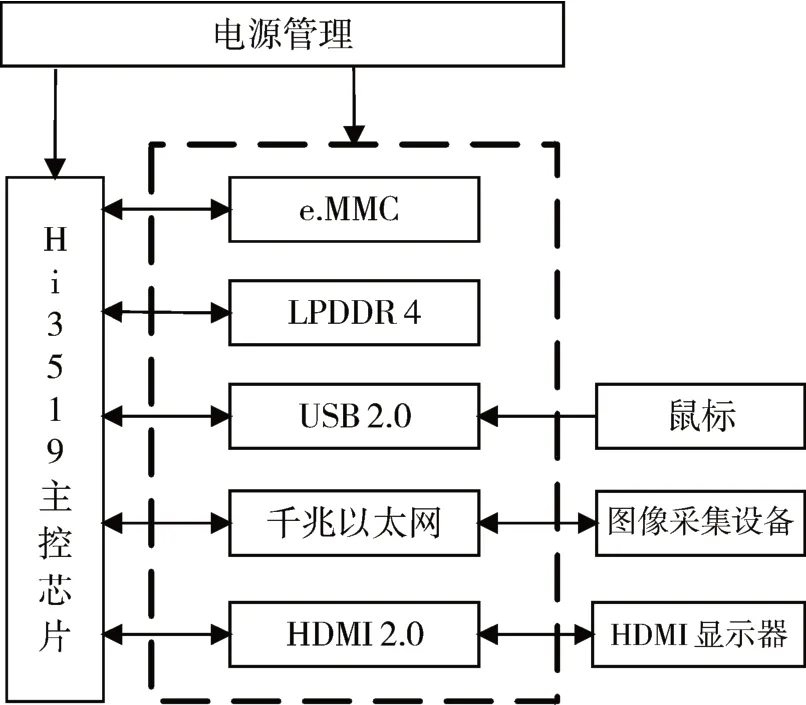

随着信息技术的高速发展,具有大量数据信息的视频已成为人们生活中最重要的信息传输方式[1]。随着人们对视频分辨率的需求不断增长,高清、超高清视频的海量数据已严重制约了视频信息的传输和存储,视频压缩解码技术应运而生[2]。视频压缩解码技术可以有效去除视频数据中的冗余信息,实现视频数据的快速传输和离线存储。同时,采用硬件解码技术能有效降低CPU在处理多路视频流时的压力。本文设计了一种基于嵌入式支持H.265 和H.264 的多路视频流硬解码装置,通过以太网接收视频流数据,可通过一台设备控制多个视频采集设备,根据需求选择要显示的视频通道,可应用于多种场景。视频解码装置的系统框图如图1所示。

图1 视频解码装置系统框图

2 硬件设计方案

高清视频解码装置使用高性能Hi3519 处理器,硬件由电源管理模块、存储模块、HDMI 输出模块和以太网模块组成,如图2所示。电源管理模块采用LTM4644开关电源芯片,为系统供电。Hi3519核心处理器作为主控芯片对各个子模块和用户接口进行配置,并对视频数据进行处理和解码。存储模块由LPDDR4和e.MMC组成,LPDDR4作为DDR为片上Linux系统的运行和海思对图像媒体的处理提供运行空间;e.MMC 作为Flash 芯片用来存放引导Linux启动的fastboot、Linux内核Kernel以及文件系统rootfs 等必要文件,并且可以保存以太网接收到的H.265 码流数据。以太网模块使用UDP 协议来接收视频采集设备传输过来的H.265 视频数据流。USB接口主要用来连接鼠标,方便使用人员对用户界面进行操作。HDMI2.0 接口连接HDMI 显示器,输出用户界面和解码后的视频。

图2 视频解码装置原理框图

2.1 电源供电模块

电源完整性是高速信号电路中重要的一环[3],为了保证高速电路中信号传输的效率,我们要考虑电磁兼容,走线阻抗,去耦电容布局等问题来为PCB 设计一个良好的电源和地[4]。方案中采用LTM4644电源芯片产生5.0、3.3、1.8、1.1V 为系统供电,单路供电电流可达到2A,4 路可达到8A,可以满足大多数设备的供电需求。同时该设计结合了SVB 动态调压功能,通过PWM 波形输出管脚输出不同的脉宽的直流电平,当运算量不大时降低频率和电压,运算量增加时提高频率升高电压,可以实现输出电压的调节、降低装置的功耗[5],具体实现方法如图3所示。

图3 动态调压实现方法

2.2 存储电路模块

本设计的存储电路是由LPDDR4(Low-Power DDR4 SDRAM)电路和e.MMC 电路构成的,其中LPDDR4作为DDR为片上Linux系统的运行和海思对图像媒体的处理提供运行空间;e.MMC 作为Flash 芯片用来存放引导Linux 启动的fastboot、Linux 内核Kernel 以及文件系统rootfs,同时也可以存储软件运行时产生的运行日志和UDP 接收到的视频码流。

LPDDR4 是一种高速CMOS、动态随机存取存储器。为了满足装置高性能和低功耗的需求,选用MT53E256M32 这款LPDDR4 芯片作为DDR,这款LPDDR4芯片将内核和I/O电源降至1.1V[6],每个芯片读写速率高达12.8GB/s(两个通道,每个通道6.4GB/s),在实现高速率的同时降低了芯片的体积。

选用三星的KLM8G1GETF-B041 作为e.MMc芯片,该芯片具有后台操作控制、命令队列、安全写保护和增强频闪等功能,并且提高了RPMB 的吞吐量,有效地提高了数据的读写速度[7]。其高达8G的存储容量可以离线存储5 个通道100min 的1080P@60fps 的H.265 码流数据,保证了存储模块的数据高容量。

2.3 HDMI输出模块

HDMI 输出模块采用HDMI2.0 接口,连接方式如图4所示,数据传输带宽可达18 Gbps,最大支持传输4K@60Hz 的视频。为保证PCB 设计的良好效果,需要控制HDMITX 差分对的PCB 走线控制差分阻抗100ohm+/-10%,并将查分对内等长控制在20mil内。

图4 HDMI接口连接

在HDMI 源端启动后,若显示器与HDMI 源端未处于连接状态,即可检测到引脚19 为低电平;若为连接状态,那么18号引脚将会给HDMI显示器提供+5 V 的电压,然后HDMI显示器内部再进行线路转换,将19 号引脚转为高电平。此时就可以通过检测15、16 号引脚的DDC(Display Data Channel)通道,以获取显示器的分辨率信息,由此来确定HDMI输出模块的输出屏幕分辨率参数[8]。

2.4 以太网模块

以太网网口是工业相机常见的接口,视频解码装置可以与视频转发服务端或视频采集装置直接连接进行视频数据接收,同时对多个视频采集装置进行指令控制。本系统采用RGMII模式,RGMII是一种减少引脚数的接口,通过将接口引脚数从GMII 接口中使用的25 个引脚减少到12 个,可以简化设计。与现有的GMII 或TBI 接口相比,它可以减少路由高密度网络解决方案所需的层数,从而降低系统成本。使用RGMII,MAC/switch ASIC 需要更少的管脚,这可以通过实现比GMII 或TBI 更小的芯片尺寸来降低MAC/switch 成本[9],该模式的参考时钟频率是125 MHz,同时兼容25 MHz 和2.5 MHz。该设计采用RTL8211作为以太网物理芯片,RTL8211 支持IEEE 802.3 RGMII 接口,RGMII 接口支持3.3V、2.5V、1.8V、1.5V 信号,并且支持半工、全工操作[10]。图5所示为以太网硬件连接示意图。

图5 以太网硬件连接

3 嵌入式软件设计

视频解码装置的开发环境为Ubuntu 16.0.4,开发环境需要安装交叉编译工具arm-himix200-linux、Hi3519AV100SDK、Qt SDK 及Qt Creator 开发环境。Ubuntu 16.0.4 运行于vmware16.0.2 虚拟机,虚拟机运行于Windows 10 操作系统。海思提供的媒体处理软件平台(Media Process Platform,MPP),可支持应用软件快速开发。该平台对应用软件屏蔽了芯片相关的复杂的底层处理,并对应用软件直接提供MPI(MPP Programe Interface)接口完成相应功能[11]。

3.1 软件整体设计

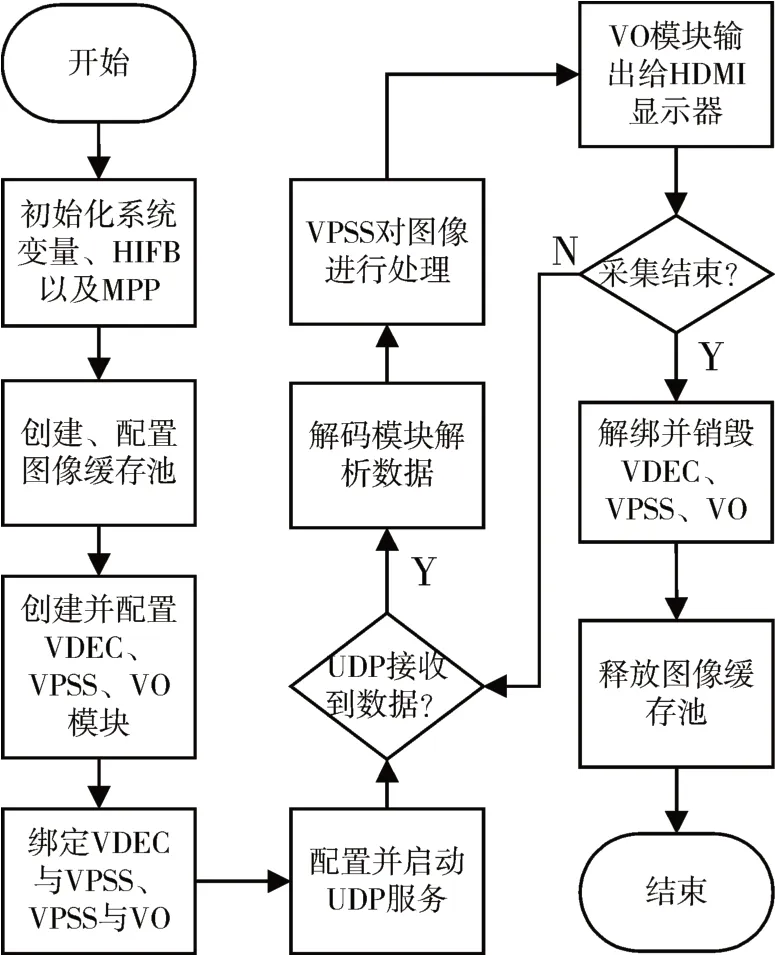

软件整体流程图如图6所示。

图6 软件整体流程图

在程序运行时,首先对系统变量完成初始化,通过读取HDMI 接口的EDID 信息来确定显示器的时序和分辨率,根据信息对HIFB进行初始化配置,最终实现用户界面的显示。根据分辨率和通道路数创建配置视频缓存池,视频缓存池主要向媒体业务提供大块物理内存管理功能,负责内存的分配和回收,让物理内存资源在各个媒体处理模块中合理使用。然后根据启动的通道数来创建相应数量的VDEC、VPSS 通道,并一一绑定。接下来根据配置界面的网络端口进行UDP 的创建与端口绑定,启用相应数量的线程进行数据的接收、处理并发送给对应的VDEC 通道,VDEC 在对视频数据进行解码后再将图像发送给VPSS 模块对图像进行裁剪、格式转换后转发给VO模块输出至显示屏显示。

3.2 界面模块设计

图形用户界面基于Qt 和海思的HIFB 实现,在视频解码装置启动后,海思视频层VHD0与Qt的图形层G0在视频输出模块完成叠加处理,通过HDMI接口输出。同时加载Linux 设备列表的鼠标驱动,使得用户可通过鼠标进行修改配置来控制视频解码装置的状态。

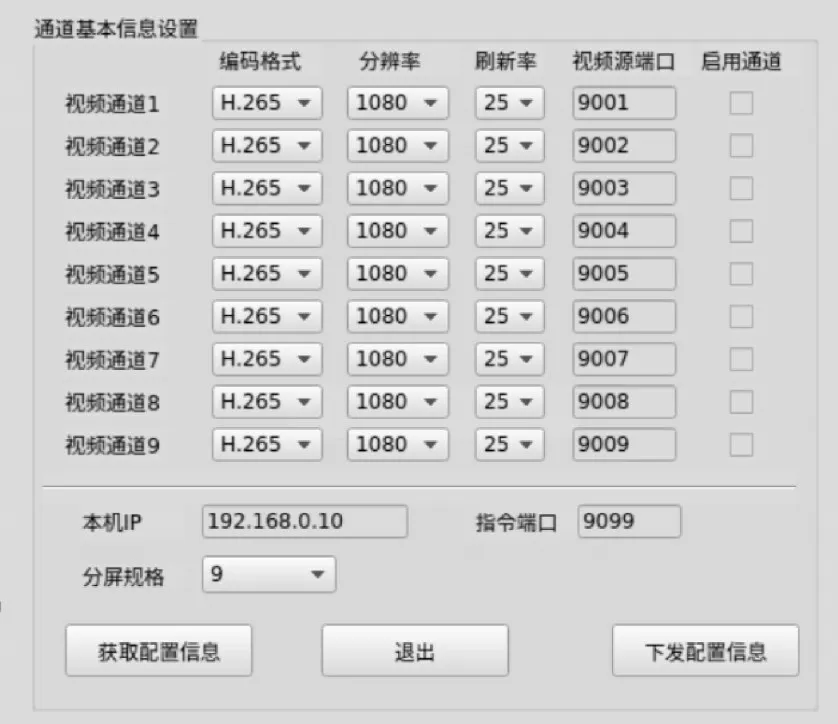

图形用户界面如图7所示,主要包括编码格式、分屏规格、通道选择和分辨率选择等参数的配置。重写Qt 的鼠标移动事件,鼠标移动到配置功能区位置区域时自动弹出,鼠标移开区域后自动隐藏,可以实现全屏无遮挡的实时预览。

图7 图形用户界面

其中编码格式是视频源端发送的视频数据压缩编码格式;视频源端口是视频源的发送视频数据的UDP 端口;分屏设置为VO 模块显示的视频个数,规格为1/4/9 分屏,根据所选分屏选项来设置VO 视频输出模块的分屏模式;最后根据所勾选的启动通道个数来确定开启UDP 端口、VDEC 解码模块和VPSS视频处理子模块的个数。

3.3 解码模块设计

Hi3519 中对视频的解码是通过视频解码模块(VDEC)实现的。VDEC 模块提供驱动视频解码硬件工作的MPI 接口,实现视频解码功能。VDEC 的硬件解码模块包括VDH 和JPEGD,支持H.264/H.265/JPEG/MJPEG,H.264/H.265 最大支持3840×2160@60fps,JPEG/MJPEG:最大支持4096×2160@60fps。视频解码功能流程图如图8所示,首先根据启动的通道个数和分辨率分配合适的VBPool 给VDEC,然后创建相应数量的VDEC 通道并配置属性,解码通道配置成功后调用HI_MPI_VDEC_StartRecvStream()函数让解码器开始接收码流。将UDP 接收到的码流数据存放在FIFO 中,每次收到数据后对FIFO 中的码流数据进行编码格式的判断,当检测到一帧完整的编码数据后,将FIFO 中的这一完整帧数据发送给VDEC 解码模块开始解码,解码完成后将图像发送给VPSS进行裁剪和格式转换。在每次完成一包数据解码后,需要判断是否结束解码功能,若需要结束解码功能则需要停止、销毁解码通道并且注销VBPool资源。

图8 解码功能流程图

4 功能测试

功能测试包括多通道功能测试、图像质量测试和解码延时测试,通过这三个测试结果来衡量解码装置。

将U-boot 引导程序、Hisilicon Linux(内核基于Linux 标准内核4.9.y 版本移植)和编写好的嵌入式程序通过HiTool工具烧写到解码装置,开机启动后加载相应的驱动[12]。然后将解码装置和遥测数据采集装置的以太网接入同一个交换机内,并配置好IP地址,每个遥测数据发送装置通过不同的端口发送遥测数据流给解码装置,在解码装置上配置好每个通道的端口号。

4.1 多通道功能测试

在只有一个通道或者对某一通道全屏观察时,启用通道只需勾选1 个,分屏规格设置为一分屏,点击下发配置信息,就可实现对某一通道的全屏显示,效果如图9所示。

图9 单分屏单通道测试图

当启用通道勾选4 个,分屏规格选择为四分屏,点击下发配置信息,效果如图10所示。

图10 四分屏四通道测试图

当启用通道全部勾选时,即所有通道都开启,点击下发配置信息后,效果如图11所示。

图11 九分屏九通道测试图

4.2 图像质量测试

本小节通过客观评价标准峰值信噪比(PSNR)来分析图像质量[13],PSNR的计算公式如下:

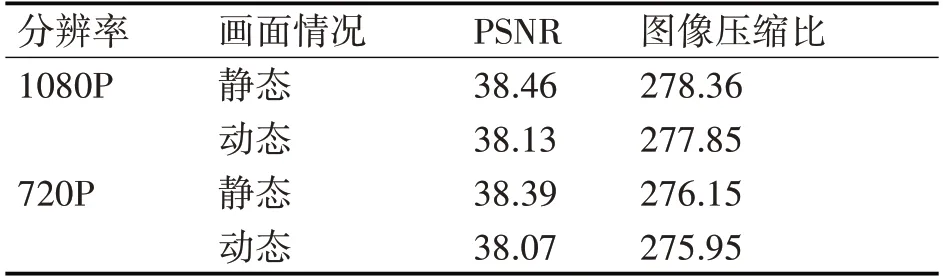

通常来讲,PSNR 值越高,图像就越清晰,一般PSNR 在[35dB,40dB]区间时,人眼已经无法分辨出图像之间的差异[14]。使用海思官方工具vpss_src_dump 可以获取到VDEC 解码后的图像数据,使用Matlab 计算图像的峰值信噪比,并且对比H.265 码流与原始YUV 图像文件压缩比。在不同分辨率和不同画面场景下的PSNR 和图像压缩比结果如表1所示。

表1 PSNR分析结果

通过表1的分析结果可知本装置在静态和动态情况下的PSNR 都处于[38dB,39dB]之间,证明解码后的图像质量良好。

4.3 解码延时测试

经系统整体流程分析可知,从视频采集装置采集数据到显示器显示主要经过三个部分,编解码延迟、以太网传输延迟和显示延迟。测试环境是在平板电脑上开始秒表计数,用相机采集秒表计数软件的图像,然后在解码装置的HDMI 显示器上显示,用手机同时抓拍平板电脑和HDMI 显示器图像得到测试结果。在高码率和低码率的传输情况下进行十组时延测试(前五组为高码率2M,后五组为低码率1M),测试结果如表2所示。

表2 解码延时测试

通过表2测试结果进行分析可知,在2M 码率情况下,实时播放的时延平均在150ms~160ms。在相同条件下采用1M 码率传输时,实时播放的延时增加,平均在250ms 左右,相比增加100ms。视频采用H.265 编码后的文件与YUV 文件压缩比大约为1:270。可以满足快速传输和实时解码的需求,具有较高的经济及军事效益。

5 结语

针对当下海军舰船监测的需求,设计了一种基于嵌入式支持多通道的解码装置。该解码装置实现了对遥测视频码流的快速传输、实时显示和多通道显示。实验结果证明,该设计用户界面操作简单,解码图像质量较好,高码率传输下实时显示延时小于200ms。相较于传统解码装置,该设计具备低延时、易操作和高质量等突出优势。该装置的设计为海军舰船领域的多通道实时监测问题提供了潜在可行的新型解决方案。