嵌入式CPU的RTC实现时间戳标定的误差分析及改进*

曹海锋

(山西工程职业学院,山西 太原 030032)

0 引言

嵌入式CPU 处理器通过特定的硬件和软件,实现了各种智能产品的管理、控制和人机交互功能,在智能产品功能实现中发挥着重要作用。

在工业自动化领域的智能仪表、控制装置中嵌入式CPU 的一项重要功能就是精确记录传感器、控制开关、警告事件等关键事件发生的时间,或者在多台智能终端组成的系统化应用中要求智能终端在时间上实现精准的流水线操作或同步动作,在此类产品实现中CPU 处理器需要对类似事件的记录或控制信号的触发控制与CPU 系统时间相互关联,准确地记录事件发生的时间或在预定的时间发出控制动作/操作指令[1]。在CPU处理器中,通常采用芯片内置的RTC(实时时钟)来实现与时间信息相关联的功能应用。

1 嵌入式CPU 基于RTC 实现输入输出事件时间戳标定的工作原理

RTC 是嵌入式CPU 处理器芯片上的常见功能模块,它的硬件结构如图1所示。

图1 CPU RTC功能模块

CPU RTC 的核心器件是一组计数器,在外部晶振的激励下进行时间间隔的累计计数,计数器的初始值通过CPU 软件进行初始化,使其与标准时间如北京时间或UTC 时间一致。RTCX1、RTCX2 是CPU 外部32.768KHz 晶振输入管脚,为RTC 电路提供时钟源,Vbat是电池供电输入管脚,该管脚的作用是当CPU 在关机状态时RTC 电路能通过该管脚从板载电池供电,维持RTC 电路正常工作,防止当系统再次加电开机后实时时间信息丢失。

在嵌入式CPU 系统设计中,一般基于RTC 实现对特定输入输出事件的时间戳标定是通过图2所示的流程实现的。

图2 基于RTC实现对输入输出事件的时间戳标定原理

事件输入、事件输出是与嵌入式CPU 系统实现特定应用相关联的外部接口,如数字变电站的继电保护装置中的跳闸信号输入、控制开关输出信号,或者工业自动化生产线上温度、湿度传感器告警输入和冷却风扇控制输出。这些与特殊应用相关联的事件信号,通过嵌入式CPU 系统设计中的输入/输出事件监测电路转换为CPU 可以识别的中断输入和事件类型信号输入到CPU 处理器。CPU 收到事件中断后,软件响应中断申请并进入中断服务程序,CPU 事件中断服务程序从RTC 功能模块读取当前时间并关联到当前申请中断的事件类型后,产生一条事件记录消息,并通过软件完成数据记录或转发,从而进一步实现上层网管信息的提交或人机交互功能。

时间同步模块是嵌入式CPU 系统实现的可选功能,当产品应用对事件的记录时间戳精度要求高或要实现多台CPU 系统时间同步关联的应用,如要求多个智能控制装置在相同时间同时触发输出动作,此时需要由时间同步模块来完成各智能终端中CPU 系统时间信息的同步。时间同步模块一般由时间同步接口硬件和时间同步协议软件组成,在电力行业比较常见的时间同步协议是IEEE1588、NTP,对应的接口类型是多模ST 光接口、100BASE-TX 以太网;移动通讯领域同步协议有1PPS+TOD、PTP 等,分别对应RS422 接口和1000BASE-T/1000BASE-X以太网接口[2]。

2 嵌入式CPU 基于RTC 实现输入输出事件时间戳标定的误差分析

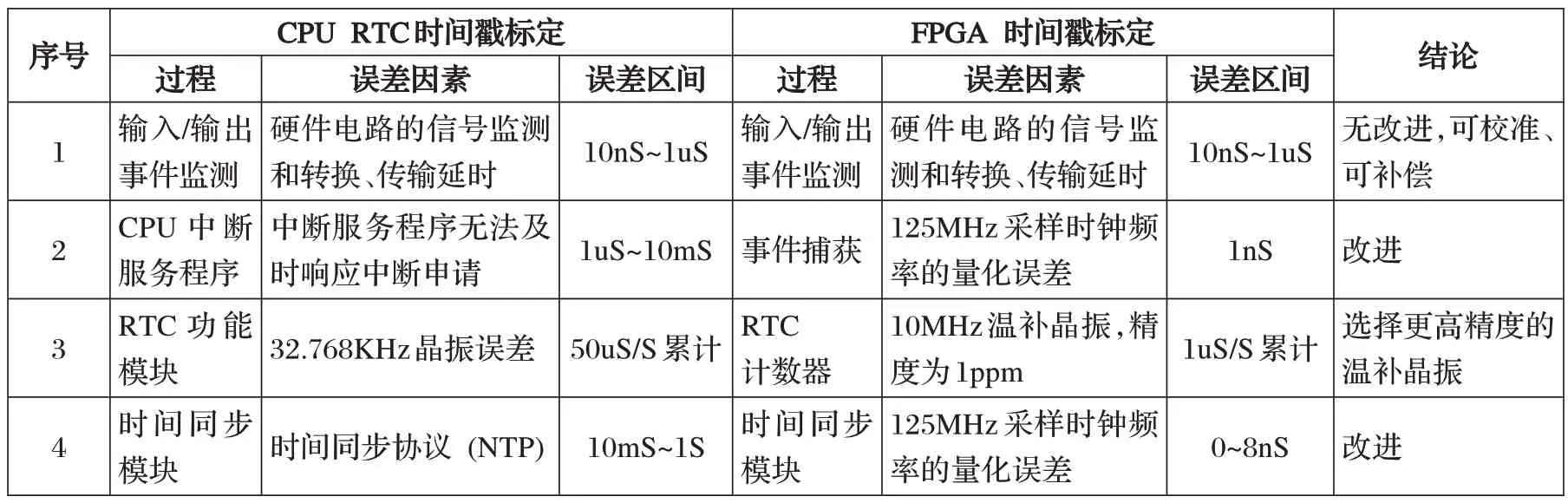

从上述时间戳标定的工作原理来看,嵌入式CPU系统完成一条事件的记录需要经过多个硬件和软件处理过程,每一个过程都会对事件对应的时间戳标定的精度带来误差,详细分析结果参见表1。

表1 嵌入式CPU基于RTC实现事件时间戳标定的误差分析表

从表1 分析结果来看,误差1 为电路信号的转换、传输误差,是单向误差,误差大小与电路元器件的性能和具体实现方案有关,经过评估测量和补偿后,该项误差可以降到100纳秒以下。

误差2 是CPU 中断服务程序执行过程的误差,该过程误差的大小与CPU 处理器性能、系统软件功能复杂度有很大关系,是随机误差,不可测量且无法补偿修正。

误差3 是由于32.768KHz 晶振存在频率偏差引起的,以50ppm 精度为例,每秒会最大累计50 微妙的时间误差,此误差为系统误差,可以通过提高晶振的频率精度和温度稳定性,同时结合使用时间同步模块的周期性校准来消除晶振的频率偏差带来的累计时间误差,比如在采用1ppm 温补晶振、利用时间同步模块实现每秒校准一次的时间校频率,理论上可以将误差3 降到1uS 以内,如果需要进一步提高,可考虑采用GPS 驯服原子钟铷钟技术来实现将误差3 降低到每秒10E-12S的偏差[3]。

误差4是时间同步模块在实现时间校准过程中引起的误差,此过程产生的误差大小与时间同步网络实现、CPU 处理器性能、系统软件复杂度有很大关系,NTP 协议同步精度受到同步数据报文的路由延时、CPU 软件对同步报文时间戳标定精度有很大关系,一般采用NTP同步的系统时间误差会大到秒级。

综合上述分析,CPU 基于RTC 实现输入输出事件时间戳标定可能会存在秒级的误差,造成误差的主要因素是因为受CPU 性能、软件运行的不确定性而产生的随机误差。在交通、工业控制、电力领域常常对智能设备的时间同步误差要求到毫秒级甚至更小,因此该实现方案常常无法满足实际应用的精度要求。

3 基于FPGA实现输入输出事件时间戳标定的设计方案

FPGA 是可编程的逻辑阵列,属于专用集成电路中的一种半定制电路。FPGA 基本结构包括可编程逻辑块、可编程输入输出单元、数字时钟管理模块、嵌入式块RAM 存储器、布线资源和内嵌专用硬核。由于FPGA 具有布线资源丰富,集成度高和可重复编程,投资较少的特点,在数字电路设计领域得到了很好的应用。

利用FPGA 实现对输入输出事件时间戳标定的设计方案如图3所示。

图3 基于FPGA实现对输入输出事件的时间戳标定原理

输入/输出事件监测模块输出的硬件中断源和事件类型由FPGA 内部高速时钟进行实时监控,当被监控的中断源信号发生触发跳变,FPGA 锁存该中断源和对应的事件类型,同时为该事件标定时间戳,并生成事件记录,FPGA 通过事件记录接口,将事件记录数据发送给CPU,由CPU 进一步实现上层网管信息的提交或人机交互功能。

时间同步功能,由时间同步接口硬件电路实现同步报文对外的收发接口信号处理。通过此功能模块可以实现多台智能终端组建成时间同步系统,实现系统级的时间同步应用。目前常用的时间同步接口有GPS(全球定位系统)、PTP(精确时间协议)、TOD(日时间)及工业领域常用的IRIG-B[4]。时间同步报文由FPGA 实现接收和发送高精度时间戳标定,并对添加时间戳的报文重新进行CRC 校验。时间同步协议则继续由CPU软件实现[5]。

采用FPGA 实现对输入/输出事件时间戳标定的设计方案主要利用了FPGA 内部的DCM 数字时钟管理单元、BRAM 存储器、高速时钟网络和可编程逻辑资源。FPGA内部功能设计如图4所示。

图4 FPGA内部模块化设计方案

FPGA 事件捕获模块是125MHz 高速时钟同步设计模块,实时监控硬件中断源信号的跳变,当采样到有事件发生时,通过同时对RTC 计数器和事件类型锁存,完成对触发事件和对应时间戳的实时标定,并将得到的事件记录写入事件记录FIFO。

由于外部被捕获事件是相对于FPGA 内部高速时钟是随机发生的,如果直接采用时钟信号来捕获事件的触发沿会存在一个时钟周期的量化误差。例如直接使用125MH 时钟采用事件触发沿会有最大接近8nS 的量化时间误差。为提高被捕获事件的测量精度,在FPGA 内部采用两个时钟PLL 实现8 个125M 时钟的静态相位调整,得到8 个精确到等相位差时钟阵列,这组时钟阵列相邻时钟输出相位依次偏移1nS。在事件捕获时采用这8 个125MHz 时钟(本文按CLK125M_0、CLK125M_45、CLK125M_90、CLK125M_135、CLK125M_180、CLK125M_225、CLK125M_270、CLK125M_315 命名)作为被测脉冲信号的时间测试时钟,相邻时钟相位偏移为45°,上升沿时间偏差1nS。

事件捕获功能模块使用8个32位时间测量计数器MEASURE_CNT0[31:0]、MEASURE_CNT45[31:0]…MEASURE_CNT315[31:0],这8个32位时间测量计数器,分别受CLK125M_0、CLK125M_45…CLK125M_315 8 个时钟激励,自由翻转,每个计数器的跳变时间偏差为1nS,该组计数器受DCM、PLL 的复位信号做同步复位。

外部事件的脉冲信号触发事件测量由FPGA RTC 时间计数器TIME_CNT_S、TIME_CNT_NS、8 个125M 多项位时钟CLK125M_0~CLK125M_315、8 个时间测量计数器MEASURE_CNT0[31:0]~MEASURE_CNT315[31:0]负责实现。外部事件脉冲信号被CLK125M_0 检测到上升沿跳变时对应的时间计数器为Tx+8,时间测量计数器MEASURE_CNT0[31:0]~MEASURE_CNT7[31:0]各自时钟采样到上升沿时的计数值分别为2、2、2、2、2、2、1、1,从时间测试计数器值看到与CLK125M_0 检测到跳变沿计数值相同的计数有6 个,由此计算被测事件脉冲跳变沿发生的时间为Tx+8-2=Tx+6,测量分辨率单位为nS,测试精度可以达到1nS。

FPGA 内部RTC 时间计数器由32 位秒计数TIME_CNT_S 和32 位纳秒计数TIME_CNT_NS 组成。FPGA 时间计数器由CLK125M_0时钟触发计数,每个时钟周期增加8nS。FPGA RTC 时间计数器的关键功能是能提供时间校准接口并完成平滑校准功能,避免时间校准前后出现时间瞬间突变。

时间校准由32 位以纳秒为单位的时间校正寄存器TIME_CNT_NS 和1 位校正标志TIME_ADJUST_FLAG 组成,该组寄存器提供给CPU 作为软件时间校正接口。当软件请求校准时,FPGA 用此组数据修正时间计数器;FPGA 内部为实现时间平滑校准功能,提供32 位时钟调整计数器CLK_ADJUST_CNT 和32 位时钟校正寄存器CLK_ADJUST_REG。在时间平滑调整过程中每个CLOCK 125MHz 0°上升沿到时,CLK_ADJUST_CNT值增加1,并将其和CLK_ADJUST_REG 做比较,如果相等,则CLK_ADJUST_CNT 计数清零,根据TIME_ADJUST_FLAG 标志,确定从TIME_CNT_NS 加“1”还是减“1”纳秒;该机制实现的校正最高精度为1/([2E32)*8]即1/34359738360。平滑调整精度由CLK_ADJUST_REG 决定,当其值为32’h00000001时,表示每个时钟周期调整1纳秒,是最快的调整节奏,调整率为1/8,当其值为32’hffffffff 时为最慢调整节奏,调整率为1/34359738360。调整率的选择由CPU 软件根据时间协议软件程序运行结果获得的RTC 时间偏差大小来决定,大偏差采用快调整率,小偏差采用慢调整率。

事件记录FIFO 是由FPGA 内部BRAM 数据存储器和读写控制逻辑组成,有写入和读取两个数据接口,遵循先入先出的写入和读取规则,通过事件记录FIFO 实现了事件记录数据的缓存和FPGA 内部不同功能模块对接时的时钟域切换。

UART 接口功能检测事件记录FIFO 是否有记录数据,如果有数据则发起读FIFO 操作,从事件记录FIFO 读出数据,按照与CPU 串口相同的波特率设置把事件记录数据从FPGA发送给CPU。

DCM 是FPGA 内部的数字时钟管理功能资源,它将从温补晶振输入的10MHz时钟信号倍频到125MHz并从BUFG 全局时钟网络输出,BUFG 是FPGA 内部专用于时钟信号的低延时高扇出布线资源,通过该时钟网络,能将125MHz 高速时钟引入到FPGA 内部其他功能模块,为它们提供工作时钟[6]。

PHY MII 接口、同步报文时间戳标定、CPU MII接口模块是FPGA 实现时间同步功能的模块,PHY MII 接口和CPU MII 接口模块分别实现与外部100BASE-T以太网PHY芯片和CPU 芯片的MII接口对接,实现接口时序和内部数据总线的转换。同步报文时间戳标定是在同步报文进入FPGA 和输出给外部PHY时由FPGA负责精确标定报文的接收和发送时间戳。采用FPGA 对时间同步报文进行时间戳标定相比CPU 通过内置RTC 标定时间戳能完全消除软件标定时间戳过程中产生的随机误差,因此使时间同步功能精度得到显著提高。

4 时间戳标定新旧方案误差对比分析

采用FPGA 对输入输出事件实现时间戳标定功能消除了CPU 在基于RTC 进行时间戳标定过程中由于受到CPU 处理器性能和系统软件复杂度影响引起的随机误差,因此明显提高了对事件时间戳标定的精度,详细对比分析见表2。

表2 对比分析表

从表2可以明显看到在采用嵌入式CPU基于芯片内部RTC功能进行事件时间戳标定时,由于受CPU性能和软件设计复杂度影响是产生标定时间精度误差的主要因素,且因为是随机误差类型,无法进行补偿,采用该设计方案标定的时间戳的总体误差在秒级别。

基于FPGA 时间戳标定的方案充分利用了FPGA实时性和硬件可编程的特点,用此方案标定时间戳的总体误差可以控制在微妙级别。

5 结论

基于嵌入式CPU 的智能产品对关键事件进行时间标定的应用非常广泛,当系统对时间同步精度要求比较高时,采用FPGA 实现时间戳标定是一个较好的技术方案,在同等时间服务器组建的时间同步网应用中,相比CPU 基于内部RTC 标定事件戳,采用FPGA实现时间戳标定能将时间戳同步误差从秒级降低到微秒级,因此,采用FPGA 标定时间戳的方案能满足大多数高精度时间同步业务应用要求。