一种基于SIC DSRD脉冲功率系统的优化方法

郭京凯,弋 锦,周 瑜,郭登耀,张 雨,袁 昊, 杜丰羽,汤晓燕,宋庆文,孙乐嘉,张玉明

(西安电子科技大学 微电子学院,西安710071)

脉冲功率技术广泛应用于食品加工、废水废气处理、离子注入一氧化氮产生等工业生产、环境处理和医疗等领域[1]。脉冲功率技术的核心是脉冲功率开关。漂移阶跃恢复二极管(drift step recovery diodes,DSRD)作为一种脉冲功率开关,可通过匹配的外部触发电路实现纳秒级的快速关断,并在负载上输出瞬时高功率窄脉冲信号。但是这种脉冲功率开关器件对于电路匹配度的要求很严格,不匹配器件的驱动电路会导致器件的输出峰值降低、脉冲前沿变缓、出现平台区使功耗升高等问题。俄罗斯科学院Ioffe研究所基于DSRD设计研制了前沿为600 ps,幅值为2 kV的脉冲源[2];以色列SoreqNuclear实验室研制出前沿小于1 ns,幅值为6 kV的固态脉冲源[3];美国SLAC国家加速器实验室通基于DSRD的前级泵浦电路,研制出幅值为15 kV,上升时间小于2 ns的脉冲电源[4-5];德国的 FID 公司及俄罗斯的Megaimpulse 公司等[6]利用 DSRD器件生产了一系列纳秒级脉冲电源。国内:西北核技术研究所研制了一套脉冲前沿为700 ps,幅值为2 kV的脉冲源[7];2018年,王亚杰等[8]报道了输出脉冲幅值为2 kV,脉冲前沿为680 ps(20%~90%)的脉冲发生器。

上述脉冲功率源的研制大多基于Si基DSRD,尽管有不少研究者报道了SiC DSRD器件的研制,但少有基于SiC DSRD器件的脉冲功率源设计。虽然SiC基DSRD的阻断机制与Si基器件相同,但SiC材料的载流子寿命更短,载流子的迁移率、饱和漂移速度也与Si材料不同。现有的脉冲发生电路的设计思路很难匹配SiC基DSRD器件。本文基于DSRD脉冲源驱动发生电路的工作原理,求解DSRD器件的驱动电流,并结合SiC材料的特性,从脉冲功率系统优化的角度出发上,分别从器件与电路两方面,提出了基于SiCDSRD的脉冲功率系统的优化方法。

1 基于SiC DSRD的脉冲功率系统优化

在脉冲功率系统优化中,DSRD驱动电路与DSRD器件本身的匹配是双向问题,既需要根据器件特性设计最优化的驱动电路参数,又需要结合驱动电路的输出能力对器件的参数进行匹配,本节从器件参数优化与驱动电路参数匹配两个角度,阐述了基于SiC DSRD的脉冲功率系统优化方式。

1.1 基于SiC DSRD脉冲功率器件参数优化

值得一提的是,在抽取等离子体的过程中,流经器件的反向电流密度过大,器件平衡空穴导电能力不足使P+P结处出现空穴积累[9],形成空间电荷区,此电荷区的扩展速度远小于空穴的饱和漂移速度,因此会延长器件的关断时间,导致器件在快速关断之前提前承受电压,出现平台区电压VPP。过早出现的VPP会徒增器件的功耗。为避免平台区的出现,器件的抽取电流Imax需满足:

Imax≤qNAvsS

(1)

其中:q为元电荷量;NA为器件基区掺杂浓度;vS为基区多子饱和漂移速度;S表示器件横截面积。式(1)是SiC DSRD脉冲源参数设计的重要考虑因素之一。除此之外,脉冲功率源的输出上限与器件结构参数的关系可表示为:

(2)

其中:W为器件基区宽度;Na为器件基区掺杂浓度;RL为脉冲功率系统的匹配负载;Vmax为脉冲源输出的峰值电压,由DSRD的最大耐压决定,其最大耐压又由器件的基区宽度、器件面积、掺杂浓度等外延参数决定。

1.2 DSRD基脉冲源驱动发生电路模型建立

DSRD脉冲源的工作电路拓扑结构如图1所示。其中:V1,V2为系统机理电压;L1,L2,L3为电感;C1,C2,C3为电容;R1为匹配负载电阻。电路使用单个MOSFET作为开关,实现器件的正向泵浦和反向抽取过程。静态下MOSFET关断,V1和V2在C2上形成的电压差为ΔV;当MOSFET在驱动芯片的控制下导通时,电感L1开始充电,电容C2经C2-MOSFET-DSRD-L2回路进行放电,为DSRD提供正向泵浦电流,DSRD的基区开始形成等离子体;ΔT时间后MOSFET关断,L1给C1充电,同时L2中的能量一部分转移给C1,另一部分转移至C2,节点A的电压逐渐升高,当C2两端电压差最大时,流经L1和L2上的电流转换路径,由L1-C2-L2-DSRD形成回路为DSRD提供反向抽取电流,当DSRD基区内积累的等离子体被抽取殆尽时,DSRD开始关断。

图1 基于DSRD的脉冲功率源拓扑电路

基于此电路的工作原理,求解正向泵浦过程KCL和KVL方程,得出电路提供给DSRD的泵浦电流为

(3)

其中,

(4)

式(3)两边对时间由0到ΔT进行积分,可计算出DSRD正向泵浦电荷量Qin为

Qin=C2ΔV(1-cos(ω2ΔT))

(5)

MOS管关断后的电路行为满足的微分方程为

(6)

其中:iL1,iL2分别为流过电感L1,L2的电流,uC1,uC2分别是电容C1,C2上的电压。

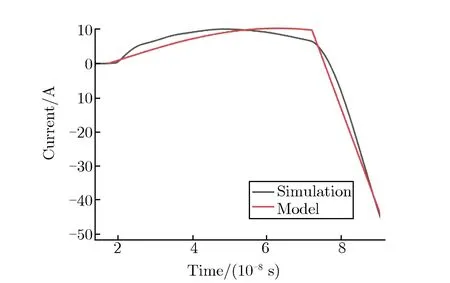

通过求解式(6)可获得电路提供给DSRD的抽取电流的表达式,但该式是一个四元的二阶常系数非齐次线性微分方程组,难以通过常规的数学方法获得解析解,虽然利用Pspice仿真软件可很好地求解该方程组,但通过Pspice获取的数值解中的抽取电流并不利于实际脉冲功率电路的设计。本文采用一种半经验半物理的建模方式,通过引入物理近似,将电路方程降阶简化式(6),求解后再结合Pspice的仿真结果,引入拟合修正参数得到解析式,最后对复杂解析式进行一阶Taylor展开,得到抽取电流iL2与各电路参数的线性拟合表达式表示为

(t-ΔT)+IL2

(7)

其中:IL1,IL2分别为MOSFET关断瞬间,通过电感L1,L2的电流值;α为能量转化比;β为能量分配比;γ为经验比例系数。

式(7)所示线性拟合模型与Pspice仿真结果对比如图2所示。由图2可见,拟合模型和仿真结果具有较好的吻合度,能作为脉冲功率源的设计依据。

图2 线性拟合模型与Pspice仿真结果对比

1.3 基于SiC DSRD的脉冲源驱动电路参数匹配

基于第1.2节的推导,可开展基于SiC DSRD的脉冲源的参数选取。基于SiC DSRD的传统脉冲源设计思路中,为减小器件基区的电荷损失,要求整个器件的动作过程时间小于载流子寿命的百分之一,但SiC的空穴寿命可能小于30 ns[10],难以实现器件的整个工作过程时间小于其空穴寿命的百分之一,因此,必须考虑SiC DSRD在工作过程中的电荷损失。由式(5)可知,DSRD脉冲源电路的正向泵浦过程可较为准确地给出,通过控制ΔV与ΔT很容易控制正向注入电荷量。但SiC DSRD的具体电荷损失率难以估量,因此,在设计基于SiC DSRD的脉冲源时,应该优先确定抽取电荷量及抽取速率,再通过抽取电荷量反推注入过程的参数。

本文选用的自研SiC DSRD的静态击穿电压为870 V,为确保器件高安全性、高可靠性地工作,脉冲源的输出脉冲峰值电压选取800 V,因此反向抽取电流峰值为

(8)

为尽可能地减少电荷损失,脉冲源器件的整个工作过程应越短越好,因此抽取速度应尽量快,确保抽取时间尽量短,在式(7)中表现为电感L1,L2与电容C1应尽量小,电容C2应尽量大。虽然正向泵浦时间也应越短越好,但考虑到MOS管的导通上升时间为5 ns,关断下降时间为8 ns,正向泵浦时间选取30 ns,结合式(3),给出电感L2和电容C2应满足的条件为

(9)

其中,Tf为电容和电感的振荡周期。

电容C1的作用是吸收器件关断后的过冲电压,保护MOS管,所以取值不宜太小,可通过Pspice仿真指导取值。根据SiC材料空穴寿命及选取的正向泵浦时间估算,全过程中电荷损失率可能大于70%,根据此损失率结合式(5),式(7),式(8),可获得电感L1的取值应满足:

(10)

其中,t′为抽取时间。在实际工作电路中t′不由电路设计者决定,但在电路设计过程中事先给定t′的取值可确定反向抽取电荷量,根据抽取电荷量可大致确定正向注入电荷量,进而确定电路参数,最后通过实际调试调整ΔV达到注入与抽取匹配的目的。综上所述,最终选取L1为350 nH,L2为100 nH,C1为1 nF,C2为20 nF,ΔT为40ns,并在测试中动态调整V1与V2。

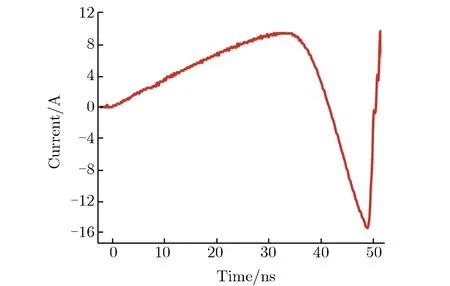

2 基于SiC DSRD的脉冲源实现

基于第1节得出的参数,搭建基于自研SiC DSRD的脉冲源。选用IXYS公司的IXRFD630驱动器,搭配DE475-102N21A射频MOSFET作为开关,搭配选定的电路参数;使用Tektronix MSO64B示波器捕捉脉冲功率系统输出波形;输出负载采用两个30 dB的衰减器,通过同轴线连接到示波器;脉冲功率系统的匹配负载阻值为50 Ω;使用德国T&M公司的SDN-414-05电流分流器读取流过DSRD的电流。基于SiC DSRD脉冲源的输出波形及通过DSRD的电流波形如图3所示。

(a)Output waveforms of pulse generator

(b)Current though SiC DSRD

由图3(a)可见:输出波形中基本没有平台区,表明优化参数后的脉冲源输出波形良好;峰值电压为760 V,脉冲上升沿tr为810 ps,基本达到脉冲源的设计需求。该结果表明,通过对器件与电路的匹配计算得到的电路参数可很好地匹配器件输入能量与输出能量,完全消除电路在残余能量下振荡引发的器件多次触发现象。可预见器件在优良的工作条件下,重频能力可得到最大化的发挥。对图3(b)所示流经器件的电流积分可知,该SiC DSRD的电荷损失率达80%,短空穴寿命导致的高电荷损失率会带来额外的功耗,但对器件输出波形有优化作用。根据第1节中描述的平台区的成因,短的空穴寿命使P+P结处不易产生空穴积累,因此输出波形不易出现平台区,器件上的反向抽取电流便可更大,使器件关断速度更快。

在高功率微波等领域的应用中,往往需要数百千伏甚至更高的脉冲电压,可将本文提到的SiC DSRD器件进行堆叠实现单个脉冲源输出脉冲峰值电压大于10 kV,然后利用数十个此类高压脉冲源进行功率合成,达到百千伏量级的脉冲电压输出。

3 结论

本文根据DSRD器件的工作原理,并从脉冲系统的角度提出器件最优面积;根据DSRD脉冲形成电路的工作原理,采用半经验半物理的方式获取了关于DSRD反向抽取电流的解析拟合表达式并结合SiC材料短空穴寿命的特性,提出了SiC基DSRD驱动电路参数的优化方案;基于该方案研制了采用SiC DSRD的脉冲功率源。实验结果表明,研制的脉冲功率源能够在50 Ω的匹配负载上输出760 V的峰值电压,脉冲上升沿达810ps,且不存在单脉冲下的多次触发现象。该脉冲功率源输出脉冲前沿在亚纳秒量级,且波形稳定性好,脉冲源体积小,能够应用在小型化超宽带电磁脉冲发生器中。