基于FPGA的便携式四极杆质谱控制系统设计

葛卫敏,许春华,林利泉,陈家新,吴曼曼,乔 佳

(广州禾信仪器股份有限公司,广东 广州 510535)

四极杆质谱仪广泛用于生物成分分析、环境污染分析和食品安全等领域。便携式四极杆质谱仪因具有体积小、功耗低、移动性强等特点,可以较好地应对现场快速、精准检测,深受人们的关注和青睐[1-2]。

传统四极杆质谱仪的下位机控制系统通常使用芯片组合架构,如Polaris Q的设计是使用微控制单元芯片(MCU)+现场可编程的门阵列(FPGA)架构实现控制和传输,上位机+数字信号处理专用芯片(DSP)芯片实现数字信号算法处理,网络协议芯片(如W5500)实现数据高速传输,控制器+双倍速率同步动态随机存储器(DDR)实现数据的缓冲和存储[2-3]。这种架构设计会占用过多的硬件板卡空间,增加功耗负担,不能满足对空间体积及功耗有严格要求的便携式四极杆质谱仪。在仪器功能和性能不变的前提下,降低功耗和减小板卡面积对于便携式质谱仪的发展具有重要意义。

本文针对便携式四极杆质谱仪体积小和功耗低的要求,使用单一芯片架构替代现有的芯片组合架构,将原本分散的扫描、控制、采集、存储、数据处理和高速传输功能集成于同一FPGA芯片内,希望能够有效降低系统功耗和板卡面积。

1 控制系统设计

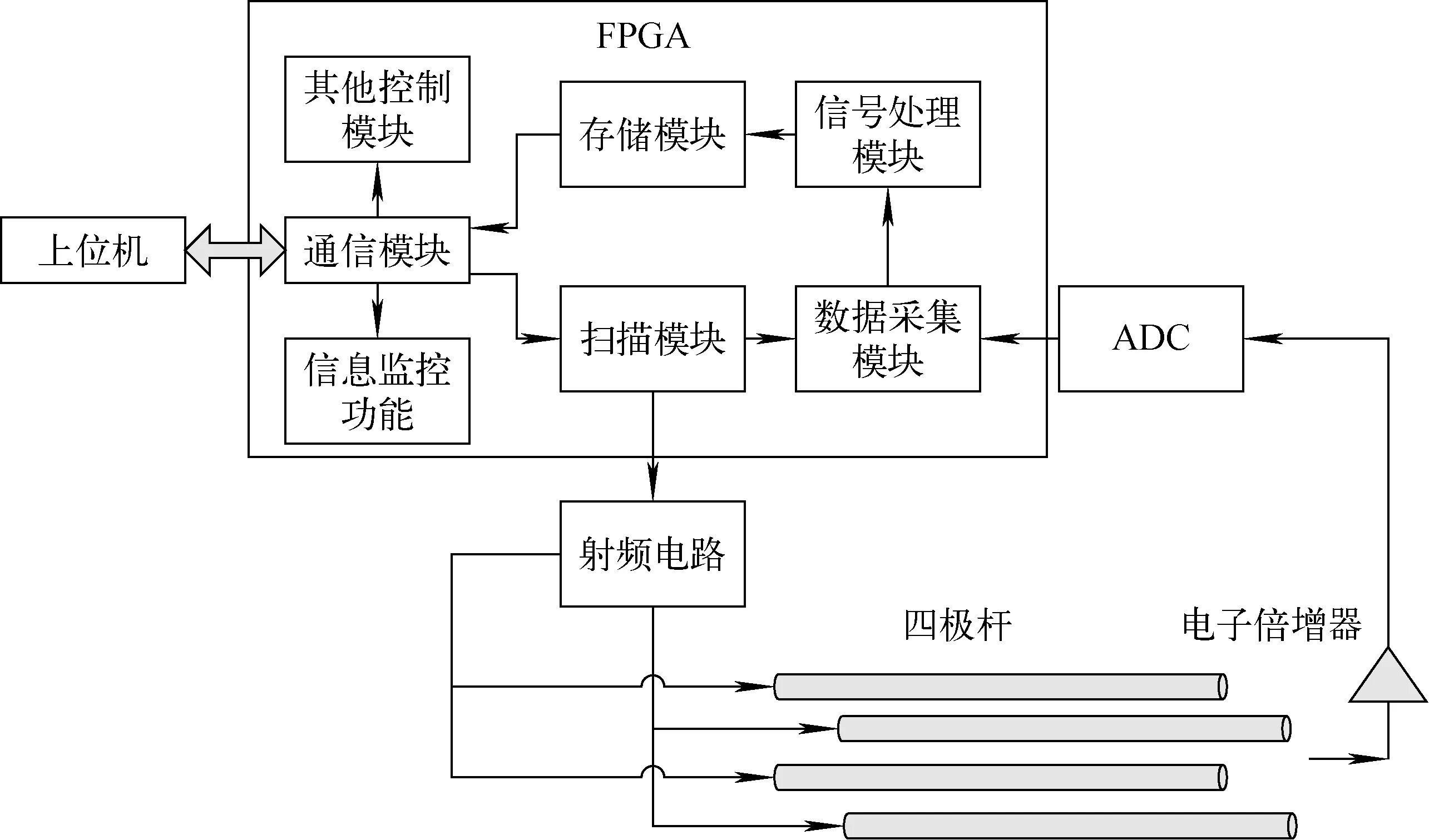

便携式四极杆控制系统采用上位机+FPGA的结构,示于图1。上位机与下位机采用千兆以太网通信,负责指令的下发和质谱图的显示。上位机选用研华PCM-9376工控机,其采用AMD G系列CPU,DDR3-SODIMM的4 GB缓存,接口丰富,并搭载了Windows嵌入式系统,可以满足低功耗小型仪器的人机交互。下位机FPGA选用Xilinx的Spartan-6低功耗芯片开发平台,相比于同级竞品Altera公司EP系列的Cyclone Ⅲ EP3C25Q240C8,该芯片采用六输入查找表技术,资源利用率更高,并且采用45 nm低功耗敷铜技术,在功耗、性能、成本之间可以更好地平衡。下位机集成开发的模块包括通信模块、扫描模块、数据采集模块、信号处理模块、存储模块及其他控制模块和信息监控功能,资源使用率相对较高。

图1 便携式四极杆控制系统架构Fig.1 Portable quadrupole control system architecture

整个控制系统通过上位机控制下位机实现。首先,上位机发送扫描采集指令到FPGA,FPGA内部的扫描状态机按照离子扫描顺序配置数模转换器(DAC)电压值,配置的电压值经射频放大电路后对四极杆进行动态扫描,从而筛选带电目标离子通过四极杆[4]。然后,将筛选的离子打在电子倍增器上将微弱信号放大形成微弱电流,被模数转换器(ADC)芯片采集,在芯片内部将模拟信号转换成16 bit位宽的数字信号,传送至FPGA内部进行处理和帧协议整合。最后,将处理后的数据存储并上传至电脑端上位机,生成谱图[5]。

1.1 通信模块

以太网通信速率有10、100和1 000 Mb 3种模式。支持片上系统(如Linux、Windows)的主控CPU,在系统端集成了完整的以太网协议,数据传输可达1 000 Mb;其余不支持片上系统的主控芯片通常选择搭载协议芯片完成网络传输。常用的协议芯片(如以太网控制芯片W5500、以太网协议栈芯片CH395)仅支持10、100 Mb速率模式。此外,协议芯片与主控芯片的数据交互采用串行外设接口(SPI),最高传输时钟仅10 MHz,由于传输过程中的固有字段消耗以及内部多级缓存逻辑的交互延时,实测吞吐量只有3~5 Mb。

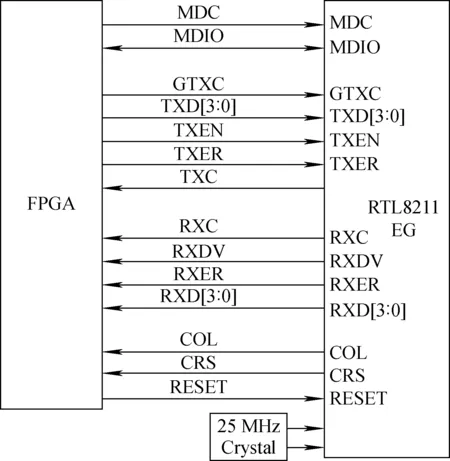

由于引脚资源的稀缺,系统采用通道复用的设计,在FPGA与上位机之间使用单一网口传输外围模块的控制指令及回传信息、各类突发告警信息、内外部模块的运行状态信息,以及扫描功能的指令和采集的数据,各类数据由内部协议按需分配通道资源。此外,其他板卡的MCU会将FPGA芯片作为信息桥,与上位机进行上下行的数据传输,此时FPGA内部承担了协议转译和MCU数据传输,该功能同样会占用大量的通道资源。经计算吞吐量,搭载协议芯片的方案已不能满足系统的数据传输。与此同时,考虑到后期数据量的扩展和多平台技术的兼容性,使用FPGA芯片引脚资源完成了千兆传输接口,使用FPGA内部逻辑资源完成了协议栈的设计,设计的千兆速率模式可以兼容百兆和十兆速率模式。首先,采用FPGA的数字I/O接口开发标准的吉比特介质独立接口(RGMII),示于图2。然后,输入端时钟使用物理层PHY(端口物理层)芯片(RTL8211EG)的125 MHz输出时钟,输出端时钟利用内部锁相环将输入时钟锁存再输出,频率同样为125 MHz。最后,上行数据和下行数据各占用4根数字I/O,在内部分别使用了输入端双沿采样(Iddr)资源和输出端双沿采样(Oddr)资源完成时钟上升沿和下降沿的双边采样,这样该设计在硬件上能够满足1 000 Mb全双工的传输速率。

图2 通信硬件结构图Fig.2 Diagram of communication hardware

在实时传输的应用场景下,点对点的用户数据报协议(UDP)比传输控制协议(TCP)更适用。本控制系统中设计的标准以太网UDP协议在内部固定了媒体存取控制位址(MAC)和静态网际互连协议(IP),按照协议最大传输单元(MTU)分包传输,实现了千兆以太网传输,可以满足便携式四极杆质谱仪高速、稳定的传输要求。

UDP协议属于公有协议,负责上位机和下位机的通信,为确保仪器内部传输的保密性,设计了以寄存器为主导的私有传输协议嵌套在UDP协议内部。私有协议中设计了16 bit位宽寄存器地址和16 bit位宽数据,采用少量显示查找表(LUT)资源为系统提供了65 536个双字节的大容量控制单元。

相较于FPGA+协议芯片的组合设计,本控制系统不仅实现了1 000 Mb以太网传输,而且硬件板卡的面积减小约2 cm×3 cm,功率降低了0.6 W(参照协议芯片W5500)。

1.2 扫描模块

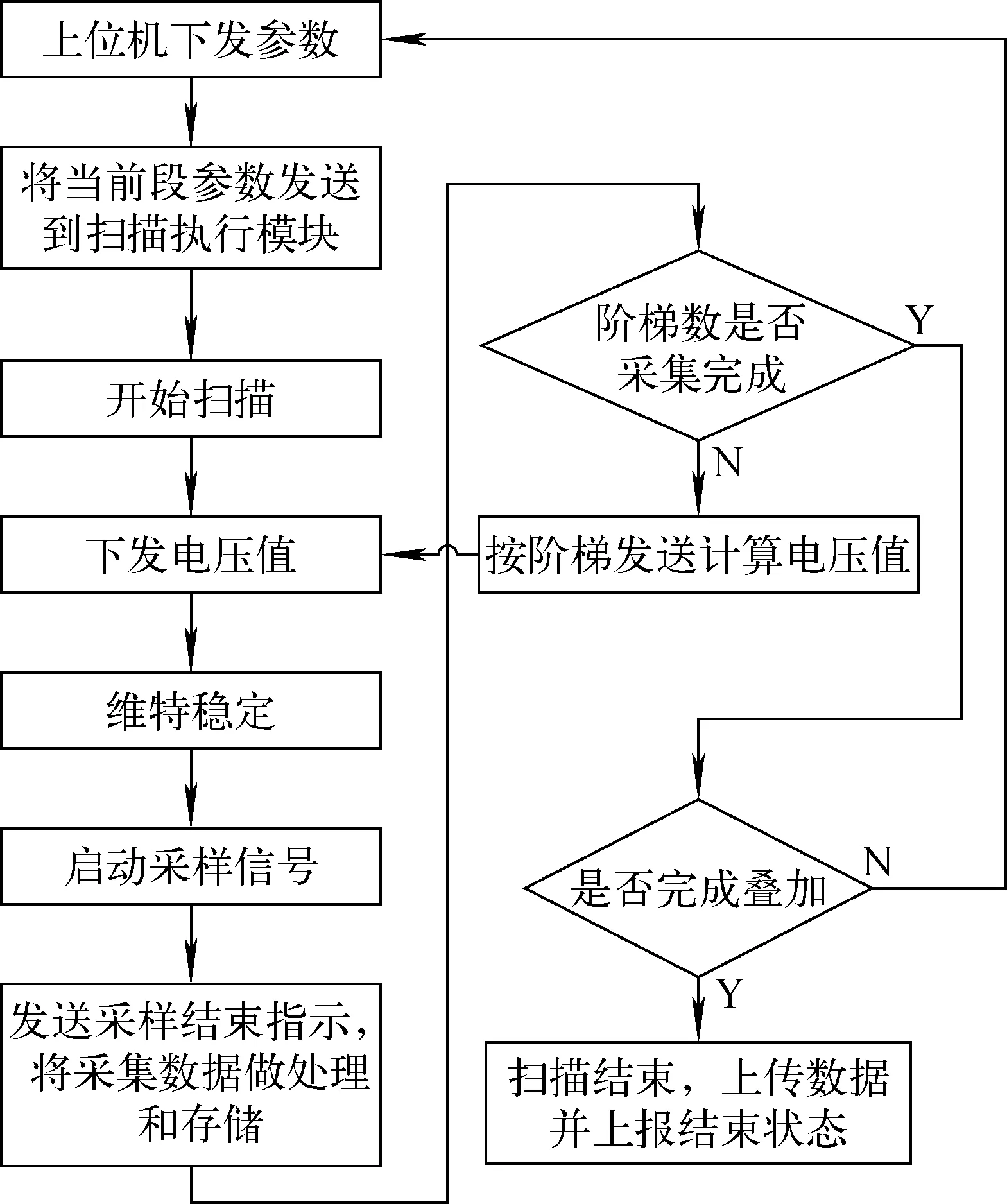

射频电压驱动四极杆产生的电场可以筛选相应质荷比的目标离子通过筛选器。改变射频电压可实现不同质量的离子通过四极杆[6]。扫描控制流程示于图3。本文设计的扫描功能是根据目标离子和扫描范围设定的,上位机将首个目标离子对应的电压值V0、目标离子个数N、步进电压ΔV以及扫描速率和循环周期等参数按照寄存器数据流的形式下发给FPGA。此时,FPGA内部的扫描模块根据这些参数构建出整套阶梯扫描模型。扫描模型包括DAC的配置数值、电压驻留时间和台阶数。根据公式Vn=V0+n×ΔV可计算出每个台阶的电压值,按照时段顺序配置给DAC芯片,通过射频放大电路后,以射频高压驱动四极杆产生电场[7-8]。电压驻留时间以μs为单位,其误差会直接影响离子筛选的结果,本设计的FPGA内部以100 MHz的时钟控制状态机的运行,精度可达ns,能够精准控制四极杆扫描时序和采集功能的联动。设计的扫描模块最快可在150 ms内完成m/z50~300全扫描。

图3 扫描控制流程图Fig.3 Flow chart of scanning control

上位机可通过参数组合的形式选择不同的扫描模式,下位机FPGA根据上位机的参数组合,采用参数分组和内部状态机复用的方式实现全扫描和选择性离子扫描两种模式,以达到资源高效复用的目的。

1.3 数据采集模块

数据采集模块的设计使用AD7723(Analog Devices公司产品)作为模拟-数字转换器。数据采集模块采用与扫描功能实时联动机制,在每阶射频电压稳定后触发开始采集信号,有效地避开了振荡期畸变信号的影响,确保数据采集的准确性[9]。

1.4 信号处理模块

ADC模块采集的原始信号存在信号基线与基准零压不匹配的问题,同时存在信噪比差、波峰分裂和毛刺突兀等问题。采用CPU或DSP专用芯片,通过一系列的数字信号处理可解决此类问题[10]。本文设计的控制系统利用FPGA的高实时性以及模块之间并行处理的优势,将信号处理算法集成于FPGA芯片内部,在节省算法芯片成本的同时,降低主控CPU的运算负荷。该设计使硬件板卡减少了约3 cm×3 cm的面积,功率降低了约1.5 W(参照TMS320系列)。

本设计的FPGA系统集成算法包括基线校准算法、数字低通滤波器算法、局部平滑算法和阈值去噪算法。其中,基线校准算法解决了基线偏差问题;数字低通滤波器算法将谱图的信噪比提升了40 dB;局部平滑算法有效去除了噪声中突发的高强毛刺噪声;阈值去噪算法有效消除噪声中的毛刺,降低了噪声[11]。

1.4.1基线校准算法 由于ADC芯片自身特性以及硬件电路设计的不足,导致采集基线与零压基线存在偏差。此外,外部干扰(如电源、射频线、高速通信线路等)也会对采集端产生不确定的噪声干扰,多方面因素导致数据采集基准线与零压偏差增大,且这种偏差的大小在仪器每次启动时无法提前预测,会直接影响仪器的稳定性和准确性。

本设计的基线校准算法根据以往的测试预设1个基准值,上电启动后,将采集的谱图数据加和并平均,然后对比计算值与预设基准值,其差值补偿到下一张谱图采集的数据中,通过不断调整和优化基准值以达到无限接近零压的目的。

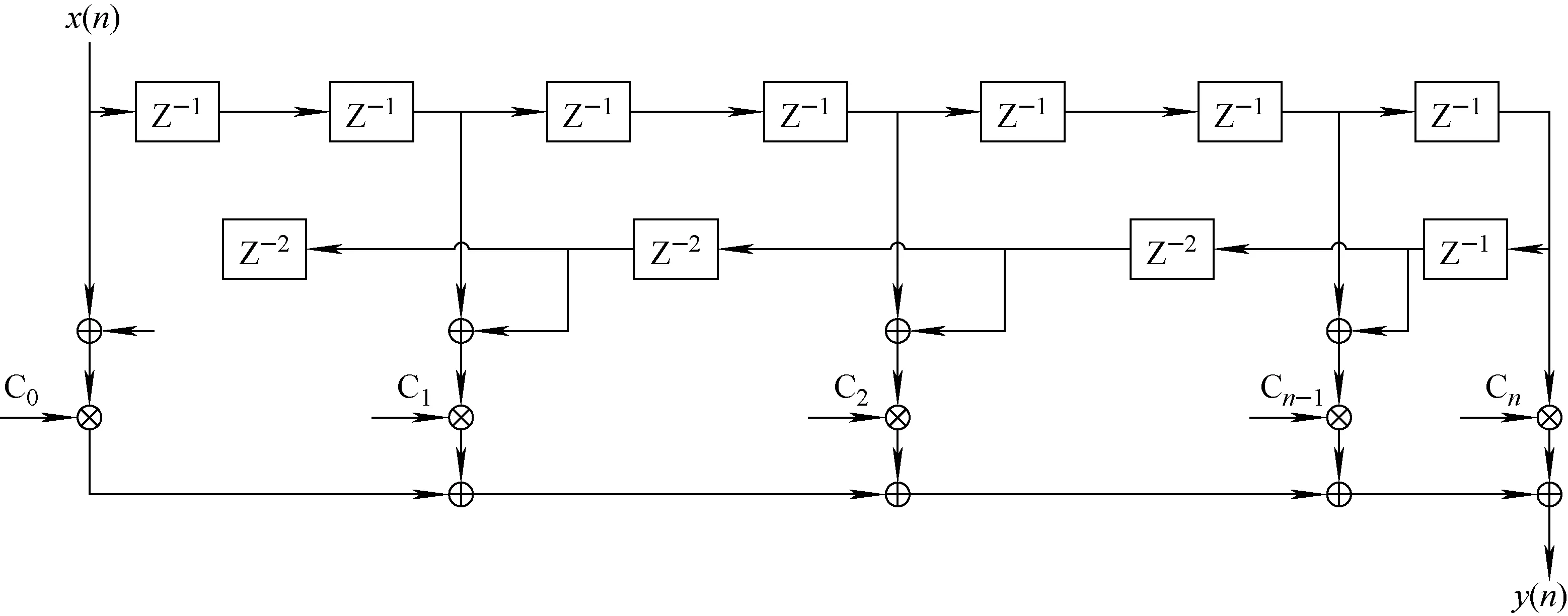

1.4.2数字低通滤波器算法 数字滤波器分为有限长单位冲激响应(FIR)和无限长单位冲激响应(IIR)。相比于IIR,FIR形式具有严格的线性相位,信号内不同频率成分之间仍保持原始相位差,只改变信号波形幅值,质谱信号失真较小[12]。不同于其他FPGA+外部模块的设计,本设计的FIR滤波器采用FPGA内部DSP资源以及内部只读存储器(ROM)存储资源完成开发。

FIR的系统差分方程为y(n)=∑h(m)×x(n-m)。式中,y(n)是当前滤波器的输出信号;n是滤波器阶数;m是滤波器的当前阶;h(m)是滤波器中的系数;x(n-m)是输入数据。由该方程可知,滤波器的输出信号是由连续的采集信号与滤波系数做线性时不变卷积运算所得,其信号质量完全取决于滤波系数的设计。滤波器结构示于图4,根据内部资源与运算速率匹配的要求,本设计的滤波器阶数为100

图4 滤波器结构图Fig.4 Diagram of filter

阶,需要matlab模拟出100个滤波系数。在matlab仿真平台上将大量数据做傅里叶变换,得到有效信号的截止频率为80 kHz,根据截止频率设计通带、过渡带和衰减率,最终生成100阶的滤波器系数,再将这些系数转换为二进制,最后固化在滤波器模型的ROM中。根据低通滤波器的对称性和时钟速率,使用FPGA内部4个DSP资源和ROM资源建立滤波器模型,经过实际测试,在有效信号不变的情况下噪声衰减40 dB。

1.4.3局部平滑算法和阈值去噪算法 实验时可以根据噪声不连续的特性区分大部分有效信号和噪声。局部平滑算法是对连续16个噪声信号做均值,用来减弱噪声信号的强度差和突兀信号。阈值去噪算法是对比设置的阈值与噪声,强度高于阈值的毛刺会被筛选出来做线性衰减[13]。这2种算法都是在数据采集后实时处理,有效地减弱了噪声信号,去除噪声中突兀毛刺,提升了谱图信号的辨别度[14]。

1.5 存储模块

由于便携式四极杆质谱仪对离子检测的实时性和准确度有较高要求,所以在仪器设计时采集大量数据做分析,且对数据传输有较高要求,通常在缓存端外置DDR存储芯片做一级缓存[15]。在本系统的数据采集过程中,同一阶梯的驻留时间内,ADC采集的是同一个离子的强度信号(16 bit),将本次采集的信号做累加(通常10~30个数据),之后再归一化,这种处理称为采集数据的横向累加。对于同组参数的多张谱图(10~20张),信号以点对点的方式累加,之后同样做归一化,称为采集数据的纵向累加。大量数据经过横向累加和纵向累加处理后,达到单点数据对应单点离子的效果,有效地将数据总量压缩80~100倍,压缩后的最大数据量可以从50 MB降至500 kB。处理后的数据可以使用FPGA内部RAM资源进行缓存,替代外设DDR方案。该设计不仅降低了物料成本,同时节省硬件板卡约2 cm×2 cm面积,功率降低约0.7 W(参照DDR芯片MT41J64M16LA_187E)。

1.6 其他控制模块和信息监控功能

除上述的模块功能外,在整个控制系统中还有其他多个DAC、ADC及外部功能模块的控制集成,主要实现数字频率合成(DDS)控制、预杆电压控制、轴向电压控制等功能,以及每个状态和告警的实时监控和上报功能。

2 实验测试

2.1 系统性能测试实验

上位机下发全扫描模式(测试范围m/z0~500),由高质量数向低质量数扫描,FPGA内部时序按阶梯模型将电压值输出给DAC。输出端DAC采用16 bit位宽的AD669,外部参考电压为10 V,配置转换速率130 ns,完全满足精度μs的电压配置输出。使用示波器检测循环扫描的电压幅值和周期时间,可以清晰地看到周期扫描的Vp-p为-0.42~9.58 V,与参考电压10 V完全一致,示于图5a。在示波器中可以看到500个离子质量数的扫描周期为-299.64 ms,与理论值300 ms相比误差为0.12%,在仪器允许误差范围内。阶梯电压测试图示于图5b,可以清晰地看到阶梯电压的时序分布,阶梯之间的电压差均衡,未有明显抖动,驻留时间一致,能够满足四极杆驱动电压的条件。多次测试结果表明,扫描电压无干扰信号或抖动,具有较好的重复性和稳定性。

2.2 25种组分挥发性有机物的混标测试

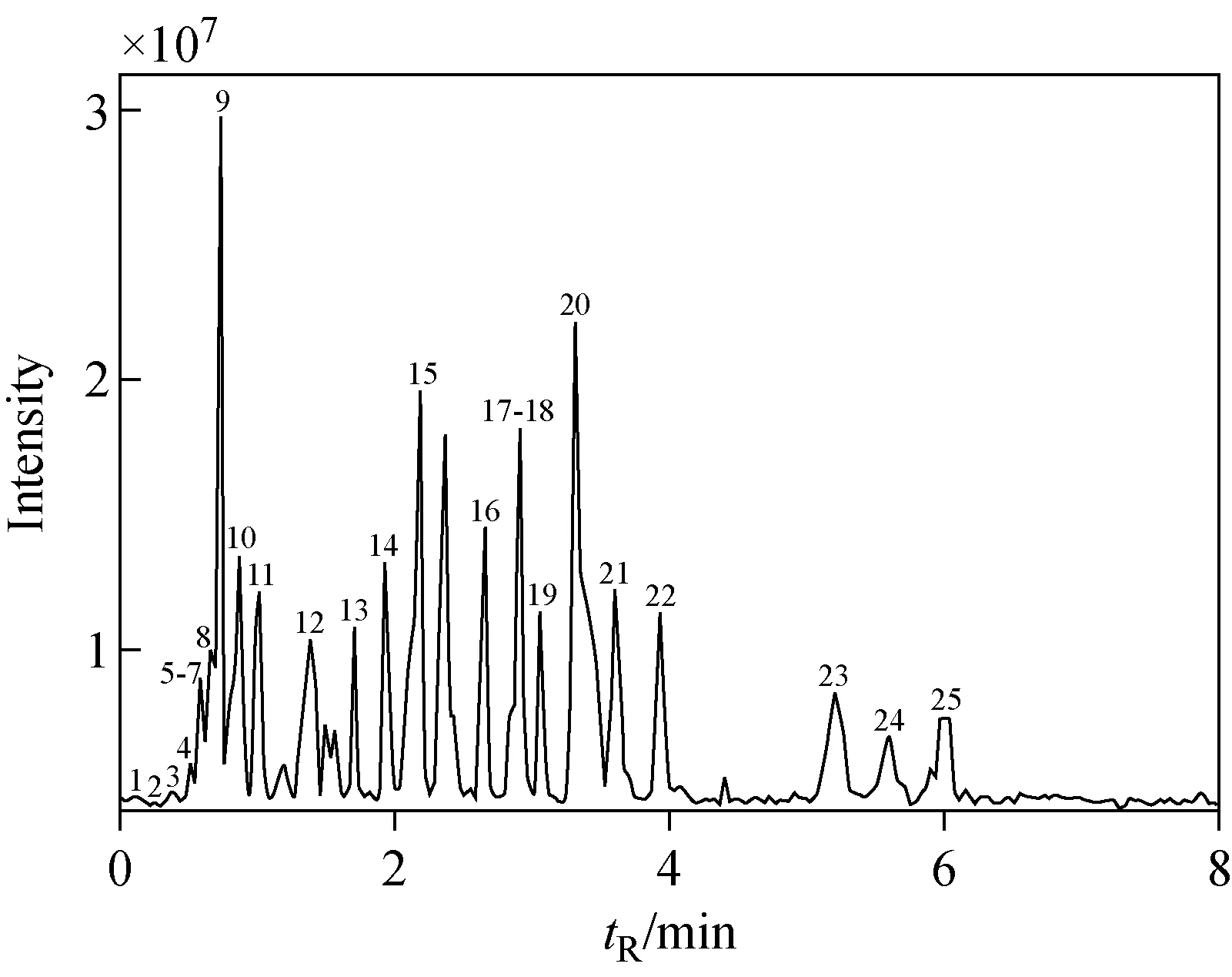

将本文设计的上位机+FPGA控制系统应用于自制的便携式四极杆质谱仪中,通过检测25种组分挥发性有机物(VOCs)标准样品,测试其可行性和稳定性。自制的便携式四极杆与磐诺A91plus气相色谱仪联用:1) 色谱条件:进样量1 μL,40 ℃保持1 min,以30 ℃/min升温至190 ℃,保持2 min,进样口温度200 ℃,接口温度230 ℃;2) 质谱条件:EI电离源,能量70 eV,质量扫描范围m/z50~300,扫描速率2 500 u/s。25种组分VOCs检测结果示于图6,经与NIST标准谱库匹配,可检出全部25种物质,无目标离子漏采缺失,定性结果列于表1。结果表明,本文设计的控制系统可以较好地应用于便携式四极杆质谱系统,能够满足系统控制、底层数据处理及传输等功能,且运行稳定。

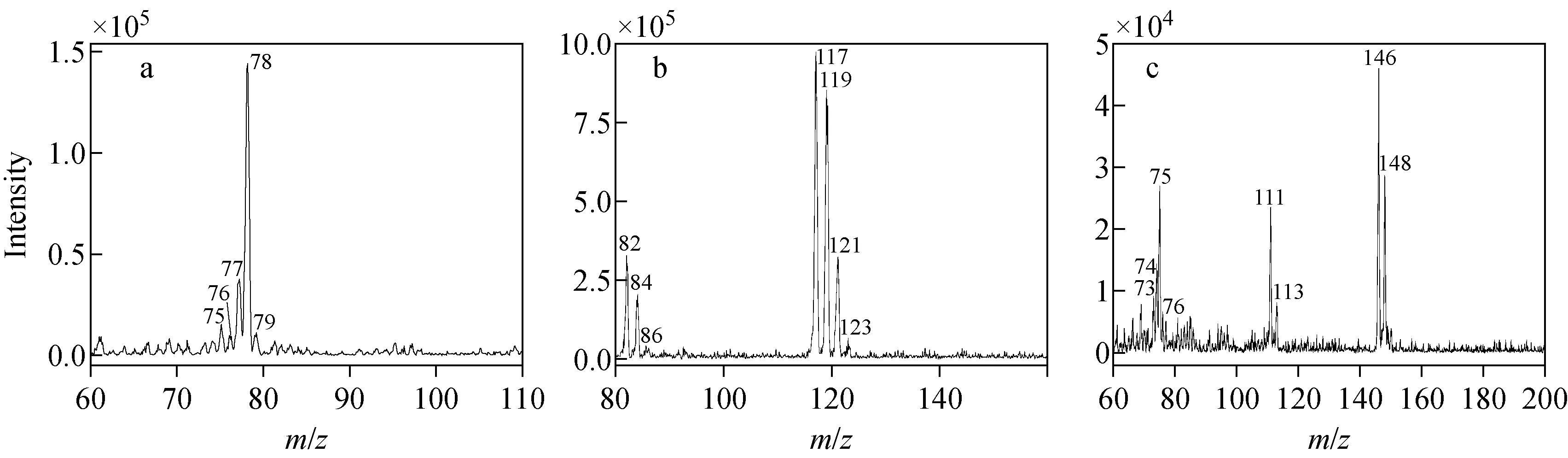

其中,苯、四氯化碳、1,4-二氯苯3个典型物质的质谱图示于图7。

注:a.扫描信号循环周期图;b.阶梯电压图图5 扫描阶梯电压测试图Fig.5 Test diagram of scan step voltages

图6 25种组分VOCs混标TIC图Fig.6 Mixed standard TIC chromatogram of 25 component VOCs

3 结论

本文设计了一种可应用于便携式四极杆质谱仪的下位机控制系统。该系统主要利用FPGA内部资源,将扫描、控制、采集、存储、数据处理和高速传输等功能集成于单一FPGA芯片内,替代了主控板上原有的W5500MCUDSPDDR等功能芯片。经过系统性能测试实验和VOCs混标测试发现,该控制系统能够满足便携式四极杆质谱仪的各项指标和需求。通过验证和测量,并与传统的四极杆质谱仪下位机控制系统相比,在保证仪器功能和性能不变的前提下,本系统的主控板功耗降低了37%,板卡面积减少了10%,并且在高速传输和底层运算功能方面得到了一定提升。本研究对于小型化仪器,特别是便于移动和有现场测试需求的仪器而言,具有较高的借鉴价值。同时,其功能模块可在多个技术平台进行移植和使用,应对不同的应用场景,无需改变硬件,只需简单修改内部代码即可,具有较高的灵活性和兼容性。

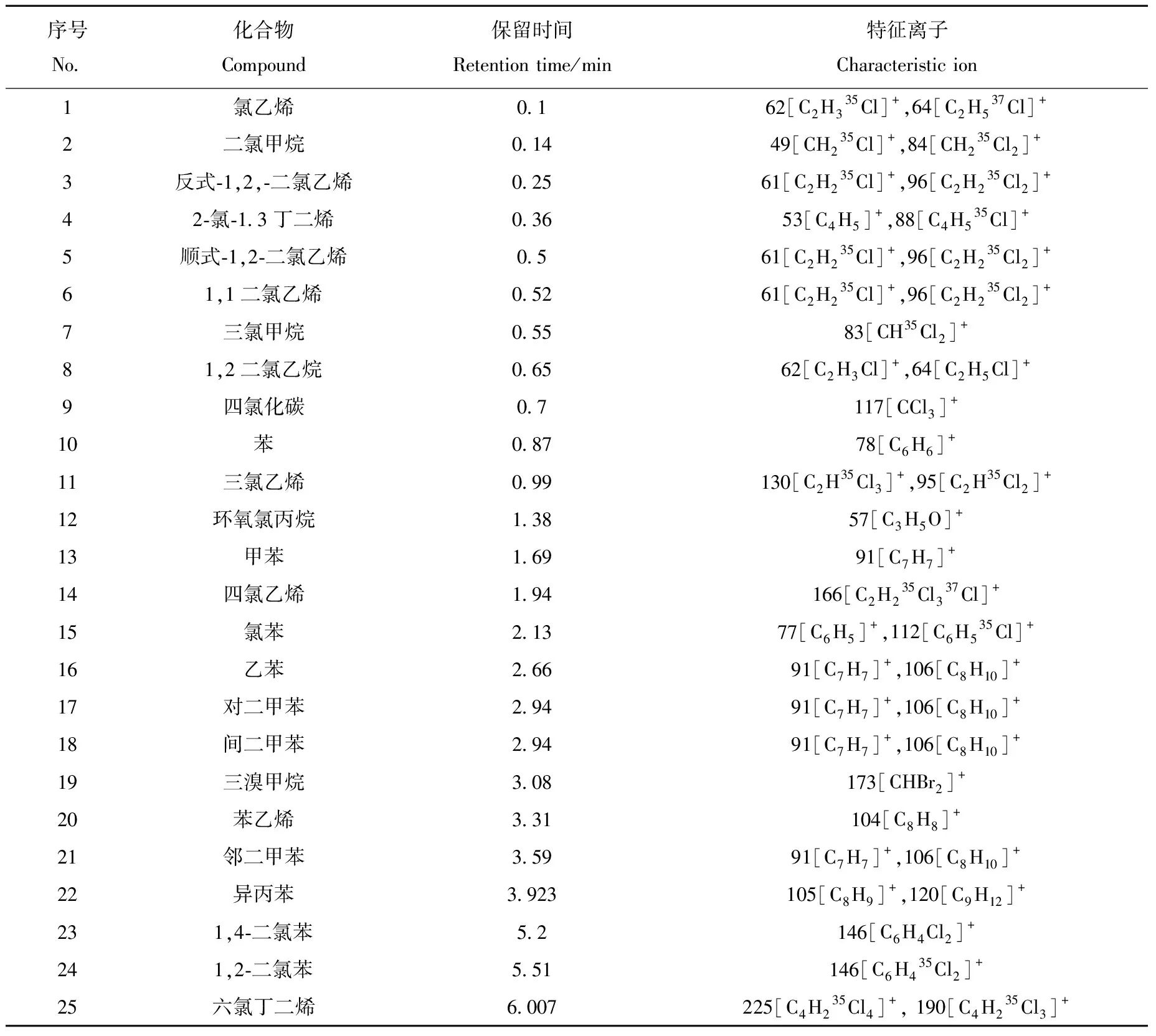

表1 25种组分VOCs混标定性结果Table 1 Qualitative results of 25 component VOCs mixed standard

图7 苯(a)、四氯化碳(b)、1,4-二氯苯(c)的质谱图Fig.7 Mass spectra of benzene (a),carbon tetrachloride (b) and 1,4-dichlorobenzene (c)