具有厚硅层的偏振分束-旋转-合波集成器件

宋泽琳,陈鹤鸣,b

(南京邮电大学 a.电子与光学工程学院、柔性电子(未来技术)学院; b.贝尔英才学院,南京 210023)

0 引 言

绝缘体上硅(Silicon-on-Insulator,SOI)平台由于其与互补金属氧化物半导体(Complementary Metal Oxide Semiconductor,CMOS)工艺的兼容性而越来越受关注[1],但SOI的偏振敏感性会引入偏振模色散和偏振相关损耗[2]。偏振分集系统被提出以解决这一问题,偏振旋转器[3-4]、偏振分束器[5-6]和偏振分束-旋转器(Polarization Splitter-Rotator,PSR)[7-13]是该系统的关键组成部分。其中,PSR同时实现偏振分束和旋转,更为可靠和稳定。

PSR包括模式演变型[7-9]和模式耦合型[10-13],前者将基模转换为高阶模,实现模式演化,带宽大、工艺容差良好,但尺寸较大;后者利用波导垂直方向不对称性实现模式转换,尺寸小、结构简单,但工艺容差低。Xiong Y等[11]利用双层锥形蚀刻波导增加工艺容差,但该器件尺寸偏大;Bai B等[13]采用混合等离子激元波导缩小尺寸,但该器件金属层对光场的吸收导致损耗较高。

对于光栅耦合器、硅光调制器和混合Ⅲ-Ⅴ/Si器件等,传统的220 nm厚硅芯层并非最好的选择[14-17],220 nm硅芯层的偏振控制器件与这些器件级联需要引入锥度,增大损耗,故需研究厚硅芯层的无源器件。

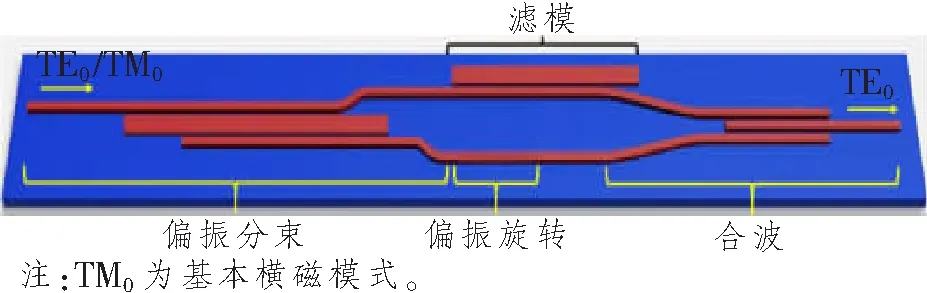

本文提出一种具有厚硅芯层的偏振分束-旋转-合波集成器件,能够将任意输入光转换为基本横电(Fundamental Transverse Electric,TE0)模式并从单通道输出。仿真结果表明,该器件在1.55 μm中心波长处偏振消光比(Polarization Extinction Ratio,PER)为45 dB,插入损耗(Insertion Loss,IL)为0.53 dB,在1.500~1.575 μm的波长范围内,PER高于30 dB,IL低于1 dB。

1 结构设计与优化

本文所提出的器件整体结构如图1所示。该器件由3部分组成,分别为偏振分束器、偏振旋转器和合波器。偏振分束器由3个波导构成的非对称定向耦合器(Asymmetric Directional Coupler, ADC)构成;偏振旋转器为切角结构,并用亚波长光栅(Subwavelength Gratings, SWG)替换其中的角区;合波器由3波导对称定向耦合器(Directional Coupler, DC)构成。该器件具有2 μm厚SiO2衬底、340 nm厚硅芯层和1 μm厚SiO2上覆层,Si和SiO2的折射率分别为nSi=3.47和nSiO2=1.44。

图1 偏振分束-旋转-合波集成器件三维示意图Figure 1 Three-dimensional schematic diagram of polarization beam splitting-rotation-combined integrated device

1.1 偏振分束器

图2 偏振分束器Figure 2 Polarization beam splitter

图2所示为偏振分束器的基本结构,由输入/输出两个窄波导和中间宽波导组成,两个输出端口通过s型波导与中间宽波导解耦。w1和w2分别为窄波导和宽波导的宽度;wgap为波导间隔;L0和Lc分别为偏振分束段上方和下方窄波对应的耦合长度;Lx1和Ly1分别为s型波导的长度和宽度。窄波导中的TM0和第一高阶横磁(TM1)模式的相位匹配条件得到满足,进入宽中间波导,在TM1的帮助下,发射的TM0模式被耦合至交叉端口。对于需要求解的单一模式,耦合长度Lc与耦合强度F的表达式分别为[18]

式中:κ为耦合系数;δ=(β2-β1)/2,β1和β2分别为该模式在窄波导和宽波导中的传播常数。由于SOI纳米线的双折射,TE0模式存在一定的相位失配,从而δ≠0,因此,尽管波导厚度h=340 nm的双折射适中,仍然不足以抑制窄输入波导和宽中间波导中TE0模式的交叉耦合,但通过优化波导间隙,使得δ远大于κ,就能够找到最佳的耦合长度,将TE0与TM0模式分离。

为了找到最佳的中间波导宽度w2和耦合长度L0/Lc,当输入光为TM0模式时,直通端口的透过率如图3所示。由图可知,当L0=Lc=10.5 μm,w2=0.830 μm时,TM0模式能更好地耦合至交叉端口输出。

图3 不同w2下,TM0模式透过率随耦合长度的变化曲线Figure 3 The variation curve of TM0 mode transmittance with coupling length under different w2

在波导间隔wgap变化的情况下,耦合长度也会随之变化,并且对于TE0和TM0模式,耦合长度并不是同步变化的。在最佳波导间隔下,TE0和TM0模式在其相应的输出端口透过率均接近1。 图4所示为不同波导间隔wgap下,直通/交叉端口的TE0/TM0模式透过率,为了使TM0模式最大程度上耦合至交叉端口,波导间隔wgap=0.19 μm。

图4 不同wgap下,TE0/ TM0模式在直通/交叉端口的透过率Figure 4 Transmittance of TE0/ TM0 mode at straight- through/crossover ports under different wgap

1.2 偏振旋转器

偏振旋转器的结构如图5所示,该结构基于切角结构,即在波导边缘刻槽,以在垂直方向上实现不对称,通过模式混合原理实现偏振模的转换[19]。所谓的模式混合原理,即当TM0模式的光入射时,由于传播截面的不对称性,波导中一对正交的混合模式(记为HP1和HP2)被激发,并且会在传播途中相互干涉,产生拍频,逐渐累积相位差。当两模式相位差累积到π时,波导中的模式就被旋转了90 °,输出光被转换为TE0模式。以SWG取代切角结构的角区,可以降低偏振转换长度对波长的依赖,增大工作带宽[20]。图中,Λ为光栅周期;wwg和hwg分别为纳米线波导的总宽度和总厚度;wetch和hetch分别为蚀刻的SWG宽度和高度。

为简化计算,将SWG替换为等效介质[21],

式中:nxx、nyy和nzz分别为x、y和z方向上的介质有效折射率;no和ne分别为寻常光和非寻常光折射率;f为SWG占空比。以f=0.5为例,偏振旋转角的表达式为[19]

式中:ηTM0-HPi为TM0模式与HPi模式的功率耦合比;HPi为波导中的第i个混合模式。为确保完整的偏振转换,要求ηTM0-HP1=ηTM0-HP2。当波导几何形状在偏振旋转角轴线上对称,即wetch=hetch时,可以获得与波长无关的θpol=45 °[19]。模式转换长度LR的表达式如下[21]:

式中:λ为工作波长;neff,HP1和neff,HP2分别为HP1和HP2模式的有效折射率。归一化模式色散系数的表达式为

式中,n0,HPi为HPi模式在1.55 μm处的有效折射率。通过优化SWG参数,可以降低色散,从而减少模式转换长度对波长的依赖,获得较大的工作带宽。

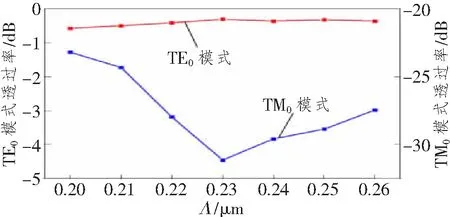

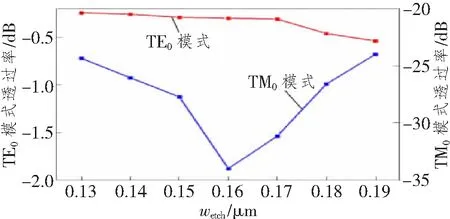

输入TM0模式,Λ和wetch变化时,输出TE0/TM0模式透过率分别如图6和7所示。为了最大程度上将TM0模式转换为TE0模式,此处选择Λ=0.23 μm,wetch=hetch=0.16 μm,此时周期数N=16。

图6 输入TM0模式时,输出的TE0/ TM0模式透过率随Λ的变化曲线Figure 6 When the TM0 mode is input, the output TE0/TM0 mode transmittance varies with Λ

图7 输入TM0模式时,输出的TE0/ TM0模式透过率随光栅宽度的变化曲线Figure 7 When the TM0 mode is input, the variation curve of the output TE0/TM0 mode transmittance with the grating width

1.3 合波器

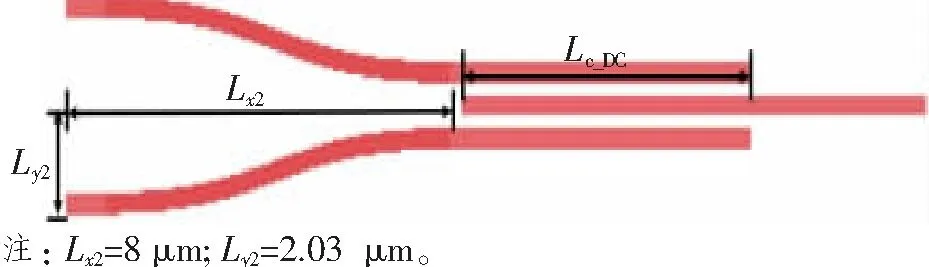

合波器的结构如图8所示。该模块的目的是将两个相同输出模式(TE)端口的光耦合至一个端口输出,采用对称DC结构,且其3波导的分布是完全对称的,因此只需对其中相邻的两个波导进行分析即可。Lc_DC为耦合长度;Lx2和Ly2分别为s型波导的长度和宽度。

图8 合波器Figure 8 Combiner

将输入光的波导称为波导1,输出光的波导称为波导2,定义δ=(β1-β2)/2,β1和β2分别为TE0模式在波导1和2中的传播常数。由于波导1与2的结构完全相同,β1=β2,满足相位匹配条件,因此式(1)所表示的耦合长度可改写为

式中,κ′为波导1和2间的耦合系数。通过优化耦合长度,能够使两波导中TE模式的光能量完全传输至输出波导内,达到单口输出TE单偏振的目的。

为了得到最优的耦合长度,在此模块的两个输入端口均输入TE0模式,在不同Lc_DC下,得到的透过率如图9所示,此处选择Lc_DC=6.7 μm。

图9 输入TE0模式时,输出端口透过率随Lc_DC变化曲线Figure 9 When the TE0 mode is entered, the output port transmittance varies with Lc_DC curve

1.4 偏振分束器、偏振旋转器与合波器级联模块

将上述模块进行级联,级联后的整体结构已在图1中展示。由于在设计时统一采用了横截面为340 nm×340 nm的硅纳米线,因此级联时无需引入额外的连接结构。对于整体器件,当任意光输入时,其中的TE0模式从上方窄波导中直接传输,在合波器处耦合至输出端口;TM0模式经过偏振分束器的中间宽波导耦合至下方窄波导,通过偏振旋转器旋转为TE0模式,然后通过合波器耦合至输出端口,最终该端口输出的为TE0模式。光在传输时,TM0模式无法全部在偏振分束区耦合至下方交叉端口,直通端口残留的TM0模式会导致器件整体PER降低,因此在直通端口末端连接一段短的宽波导用以过滤TM0模式的剩余功率,如图10所示,其工作原理与偏振分束器中的中间宽波导类似,在TM1模式的帮助下,将残留的TM0模式耦合至宽波导末端。LF为滤模波导长度。

图10 滤模结构Figure 10 Filter mode structure

同时输入TE0和TM0模式,不同的LF下,输出端口的TE0/TM0模式透过率如图11所示,TE0模式对LF变化并不敏感,但TM0模式受其影响很大。为了得到最大的PER,此处选择LF=9.8 μm。

图11 不同LF下,同时输入TE0和TM0模式,输出端口的TE0/ TM0模式透过率Figure 11 The TE0/TM0 mode transmittance at the output port under different LF, and simultaneous input TE0 and TM0 modes

级联后,由于3个模块之间相互影响,特别是偏振分束器的交叉端口与偏振旋转器相连接,需要对相关参数进行微调。同时输入TE0和TM0模式,对于偏振分束器的下方窄波导,其耦合长度Lc导致输出端口处TE0/ TM0模式的透过率变化如图12所示,为了最大化输出光的PER,选择Lc=11.5 μm。

图12 不同Lc下,同时输入TE0和TM0模式,输出端口的TE0/ TM0模式透过率Figure 12 The TE0/TM0 mode transmittance at the output port under different Lc, and simultaneous input TE0 and TM0 modes

不同的SWG参数下,同时输入TE0和TM0模式,在输出端口得到的TE0/TM0模式透过率如图13所示,可见TE0模式的输出透过率变化不大,但TM0模式透过率很大程度上受到结构参数变化的影响。为了得到最佳的PER,选择wetch=0.17 μm,hetch=0.15 μm。

图13 不同wetch和hetch下,同时输入TE0和TM0模式,输出端口的TE0/ TM0模式透过率Figure 13 TE0/TM0 mode transmittance at the output port under different wetch and hetch conditions, and simultaneous input TE0 and TM0 modes

2 性能分析

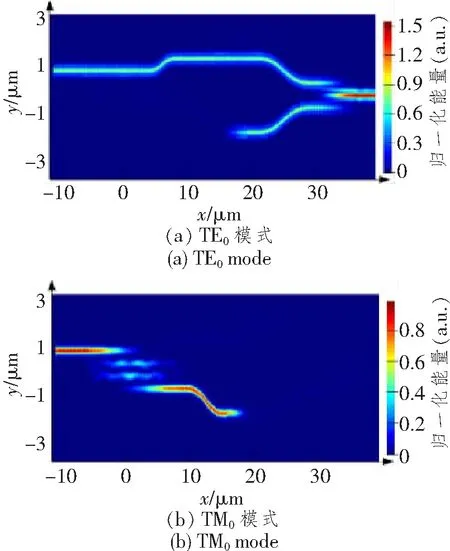

图14 整体器件中的光场传输Figure 14 Light field transmission in the integral devices

对于本文设计的器件,使用具有非均匀网格尺寸的三维有限时域差分方法(Three-Dimensional Finite Difference Time Domain, 3D-FDTD)来研究模式特性。器件在工作波长为1.55 μm处的模场如图14所示,输入的TE0模式沿上方直通通道传播,在合波器处耦合至输出端口;输入的TM0模式则通过中间宽波导耦合至交叉通道,在偏振旋转区转化为TE0模式,并通过合波器耦合至输出端口。

器件的性能主要由PER和IL来评估,定义为

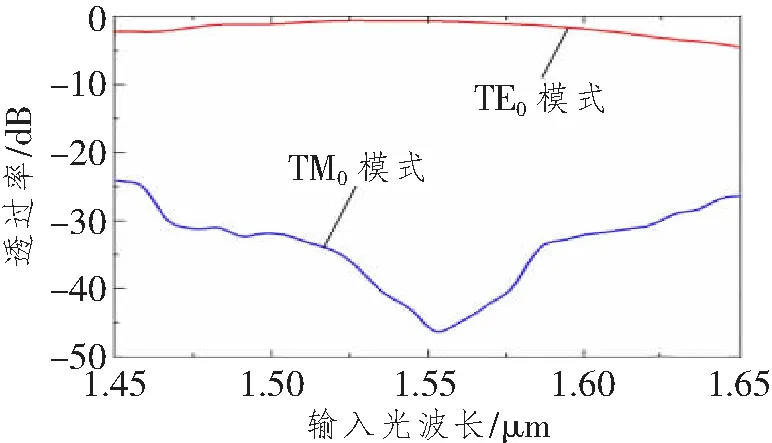

式中,TTE和TTM分别为输出端口处TE0和TM0模式的透过率。输出端口的TE0/TM0模式透过率如图15所示,由图可知,TM0模式的透过率能够保持在较低的水平。

图15 输出端口TE0/TM0模式的透过率随输入光波长的变化Figure 15 The variation of the transmittance of the TE0/TM0 mode at the output port versus the input wavelength

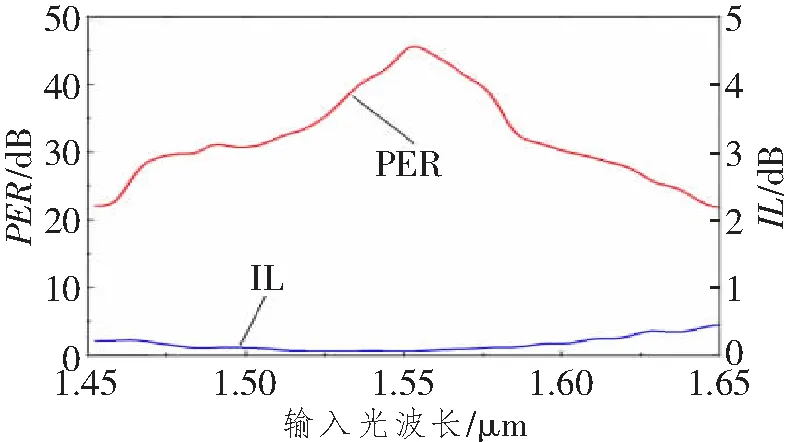

图16所示为不同输入波长下PER和IL的变化。由图可知,在1.55 μm的中心波长处,PER为45.0 dB,IL为0.53 dB。所设计的器件在1.536~1.573 μm波长范围内,PER>40 dB;在1.525~1.580 μm波长范围内,PER>35 dB;在1.500~1.575 μm波长范围内,IL<1 dB且PER>30 dB。

图16 PER和IL随输入光波长的变化曲线Figure 16 The variation curve of PER and IL versus the input wavelength

3 工艺容差分析

本文所设计器件通常的制造工艺流程如下[22]:首先使用340 nm厚顶部Si层和2 μm厚掩埋SiO2的标准 SOI晶片,通过电子束光刻技术将结构图案转移,然后利用感应耦合等离子体刻蚀工艺对硅芯层进行蚀刻,得到硅波导。在实际制造过程中,器件尺寸不可避免地存在一定的误差,从而引起性能的劣化。制造工艺误差会导致波导的宽度和厚度产生变化,同时器件中有SWG结构,工艺误差会影响SWG周期。下面将分析器件整体性能仍有原来的85%以上,即在透过率仍大于70%且PER仍大于25 dB的情况下,允许的厚度、宽度以及光栅周期的制造误差。

图17所示为仿真得到的PER和IL在不同波导宽度和厚度偏差内的变化,由图可知,在1.500~1.575 μm波段,在PER>25 dB,IL<1.54 dB的情况下,允许有±5 nm的厚度、±10 nm的宽度和±10 nm的SWG周期误差。因此,该器件具有较好的制造容差,并且在容差范围内性能良好。

表1所示为本文设计的器件与文献报道的PSR之间的PER、IL和长度等几个参数之间的性能比较。由表可知,与同类器件相比,本文设计的器件具有较高的PER,且IL相比文献[13]低得多。与IL较低的文献[9]和[11]所报道器件相比,本文所设计的器件尺寸更小,有利于大规模片上集成。

表1 本文设计的器件与文献中PSR的性能比较Table 1 Performance comparison between the device designed in this paper and PSR in the literature

图17 PER和IL受工艺误差影响的变化Figure 17 The value of PER and IL affected by input wavelength

4 结束语

本文利用非对称3波导渐逝耦合系统和SWG结构,提出了一种单通道输出TE0模式的集成器件。该器件由偏振分束器、偏振旋转器和合波器组成,所采用的SOI纳米线经过优化设计,输入的TE0和TM0模式被分离并分别进入直通和交叉通道,其中TM0模式经过SWG替换切角的偏振旋转器旋转为TE0模式,并与直通通道输出的TE0模式一同耦合至输出端口。仿真结果表明,器件在1.55 μm波长处具有较高的PER(45 dB)和较低的IL(0.53 dB),在1.500~1.575 μm波长范围内工作良好,PER>30 dB,IL<1 dB,且具有较好的工艺容差。该器件具有高消光比和宽工作带宽的优点,在硅基光子集成电路中具有重要的应用前景。