一种嵌入式装置逻辑仿真系统的实现方法

徐艳艳,孙运乾,姜艳娟

(许继电气股份有限公司, 河南 许昌 461000)

0 引 言

可视化逻辑设计技术以图形化和模块化逻辑组态方式代替传统手工编写源代码的程序开发方式,为嵌入式装置提供了快速开发手段,保证了装置的可靠性和稳定性,为智能电网领域强大的智能设备开发能力提供了支撑,在智能变电站中得到了广泛的应用[1-4]。但是,在装置开发过程中,当逻辑设计工具自动生成的目标代码下载到嵌入式装置后,如果出现逻辑运行异常,开发人员对装置很难快速定位问题出现的具体原因。因此迫切需要一种对装置内部逻辑进行在线监视的工具,方便开发人员和调试人员快速定位问题原因。

为此,本文提出一种嵌入式装置的逻辑仿真系统的开发思路,对用户逻辑图采用XML数据建模方式,利用数据透视技术,实现嵌入式装置内部逻辑的实时图形化展示。

1 可视化逻辑仿真的系统架构

采用模块化的设计思想,将系统大致分为逻辑设计工具、逻辑仿真工具以及运行在嵌入式装置中的远程过程调用(remoteprocess communication,RPC)服务程序三个模块。

逻辑仿真系统的总体结构组成如图1所示。

图1 系统总体结构

逻辑设计工具输出逻辑图描述文件、内存映射文件和目标程序三个文件。

嵌入式装置运行逻辑设计工具生成目标程序,同时,建立RPC服务进程,为逻辑仿真工具提供内存读写服务。

逻辑仿真工具打开逻辑图描述文件和内存映射文件,通过解析两个文件,可得到逻辑图各节点的图形信息和内存地址。和嵌入式装置建立RPC服务连接后,最终可实现装置内部逻辑的实时图形化展示功能[5-6]。

2 功能模块设计实现

2.1 逻辑设计工具的实现

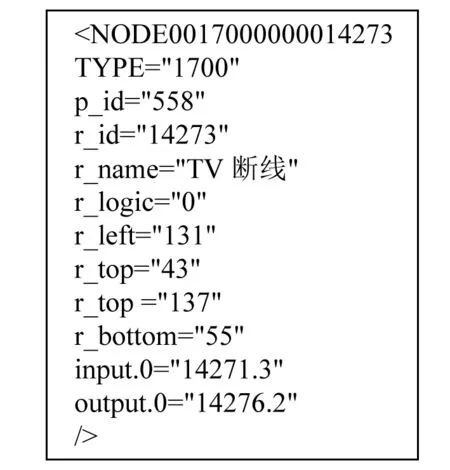

逻辑设计工具的主要功能为用户提供逻辑组态界面,支持用户进行逻辑图进行修改参数、添加节点和删除节点等操作,最后,生成逻辑图描述文件。逻辑图描述文件采用可移植、易扩展的可扩展标识语言(extensible markup language,XML)建模方式[7],存储各个节点的图形信息包括类型、ID号、页面信息、位置信息、逻辑操作、参数信息、输入连线和输出连线等。以“TV断线”节点为例,该节点的XML数据建模内容如图2所示。

图2 XML的数据建模

在建模信息中, TYPE 是逻辑节点的类型,p_id是节点所在的页面号,r_id是节点的注册ID号,r_name是节点的名称,r_logic是节点的逻辑操作类型,r_left、r_top、r_top、r_bottom是节点的坐标位置,input.0、output.0是节点的输入、输出参数。该建模信息被逻辑仿真工具用于图形化展示。

逻辑设计工具的另一重要功能,是在用户完成逻辑图形的组态设计后,编译生成目标程序和内存映射文件。逻辑设计工具按照如下流程进行编译。

(1) 对逻辑节点进行分类、排序和编号。

(2) 生成逻辑图对应的C代码。

(3) 调用编译器编译C代码,生成目标程序和map文件。

(4) 解析map文件中的映射符号表,得到逻辑节点状态存储的首地址。

(5) 根据逻辑节点状态存储的首地址和节点编号,得到各个节点在装置的内存地址。

(6) 将节点编号和内存地址的映射关系,生成到内存映射文件。

2.2 RPC服务功能的实现

逻辑仿真工具的数据透视功能通过RPC服务实现[8-9]。RPC 作为一个客户/服务器模型,在本文所述的逻辑仿真系统中,其服务端程序在嵌入式装置中运行,其客户端在逻辑仿真工具中运行。

逻辑仿真工具发起内存读取请求,将内存地址通过报文形式发送给嵌入式装置;嵌入式装置收到报文后,触发RPC服务读取装置内存,将内存读取结果以报文形式回复给逻辑仿真工具;最后,逻辑仿真工具将内存数据以图形化方式显示在用户界面。

2.3 逻辑仿真工具的实现

逻辑仿真工具的工作流程如图3所示。

(1) 加载并解析由逻辑设计工具生成的逻辑图描述文件,绘制用户界面。

(2) 加载内存映射文件,得到各个逻辑节点的相对地址。

(3) 通过RPC服务与装置建立连接,得到装置的重定位信息。

(4) 将逻辑节点的相对地址转换为绝对地址,发出RPC请求。

(5) 得到RPC的回复报文,更新图形界面上逻辑节点的状态。

图3 仿真工具工作流程

(6) 任务休眠500 ms后,流程回到第(4)步,重复读取内存、刷新界面和任务休眠操作,直到用户关闭软件。

经过上述流程,可视化逻辑仿真工具实现了逻辑图内节点状态的实时刷新功能。

在工程应用中,需要对逻辑仿真工具的RPC访问效率进行优化。一方面,只对当前用户可见的节点状态进行刷新;另一方面,对节点的内存地址进行升序排序,地址连续的节点地址整合为一个内存块,以内存块为单位发送RPC请求,避免频繁地单字节读取内存[10-11]。

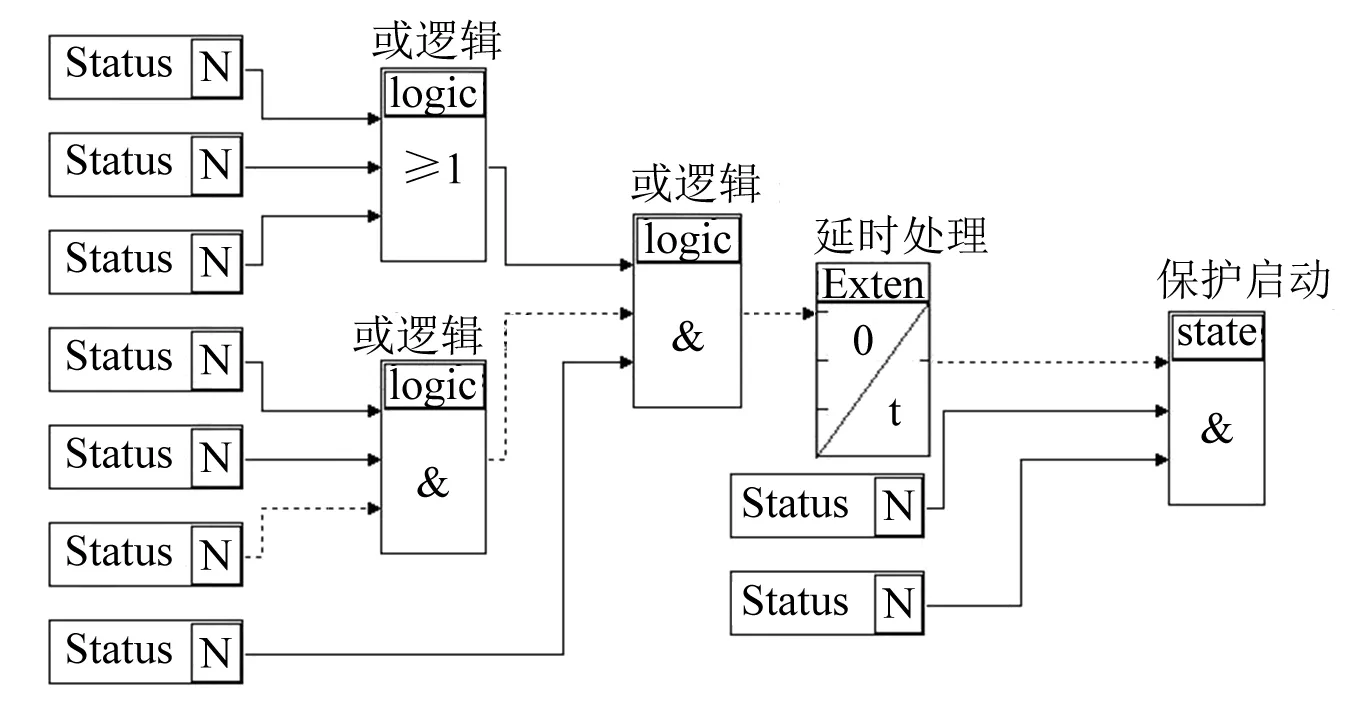

逻辑仿真工具的显示界面如图4所示。图中的实线表示逻辑结果为“真”,虚线表示结果为“假”。通过逻辑图形化展示的方式,使用户能够快速定位问题的原因。

图4 逻辑仿真工具界面

3 系统可靠性和时效性验证

根据工具的设计与实现,采用某型号的嵌入式继电保护装置,测试工具的可靠性和时效性。

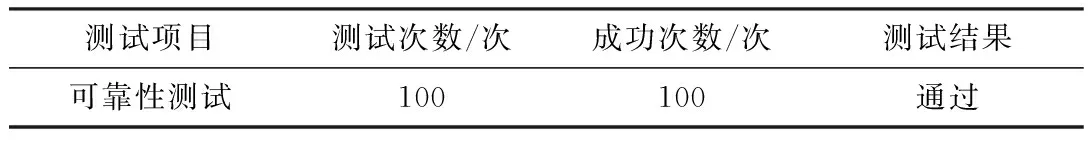

3.1 可靠性测试

首先,测试逻辑仿真工具显示的逻辑节点的状态和嵌入式装置的该逻辑节点的运行状态的一致性。

在继电保护装置的逻辑图中选择一个逻辑节点,了解该节点的变位逻辑,通过测试仪加量的方式,触发选中节点的状态在“真”和“假”之间反复变位[12]。查看工具显示的逻辑节点的状态是否能够同步刷新,测试结果如表1所示。

表1 可靠性测试结果

3.2 时效性测试

主要验证工具的逻辑图显示的节点状态和装置实际运行的节点状态的同步时间。

逻辑仿真工具界面刷新的定时器周期设定为500 ms,分别打开3个不同的逻辑图描述文件,所包含的逻辑节点的个数分别为500个、1 000个和2 000个。在嵌入式装置上进行单个或多个节点的状态变位,查看工具界面上逻辑节点的状态同步时间。测试结果如表2所示。

表2 时效性测试结果

3.3 结果分析

随着逻辑图描述文件内节点个数的指数级增加,逻辑仿真工具的响应时间没有明显延时,这说明对逻辑仿真工具的显示优化处理是有效果的。

4 结束语

本文设计的嵌入式装置逻辑仿真系统,通过在线的读取和分析装置内存中逻辑节点的当前状态,实时图形化展示装置的逻辑运行结果,从而快速定位逻辑运行异常的问题原因。该系统采用模块化的设计思想,可适应于不同操作系统的嵌入式装置,为嵌入式装置的开发和维护提供了有力的支撑,已经在国内外的智能变电站中广泛应用。