基于导频的储存环束流位置测量处理器研制

梁 钰,谢春杰,朱文超,唐雷雷,卢 平,孙葆根,王 琳,周泽然

(中国科学技术大学 国家同步辐射实验室,安徽 合肥 230022)

束流轨道稳定度是同步辐射光源的关键指标,它直接影响光源性能以及实验线站同步光源的质量, 束流位置测量(BPM)处理器根据BPM的电极感应信号计算束流实时位置,监测束流轨道变化,是轨道稳定系统不可或缺的组成部分[1-4]。合肥先进光源(HALF)是第4代真空紫外与软X射线衍射极限储存环,由中国科学技术大学国家同步辐射实验室承担其设计与预研工作[5]。衍射极限储存环亚微米量级的束流轨道稳定度给加速器BPM系统带来了新的挑战。

为满足合肥先进光源BPM系统的稳定性要求,本文设计并研制具有自主知识产权的基于导频的储存环BPM处理器。相比于目前在HLS Ⅱ上应用的IT公司的商业化BPM处理器使用铰链开关补偿通道一致性,自研BPM处理器采用导频机制消除通道增益不一致的影响。为提高研发的自主性和器件采购的灵活性,设计中采用国产化芯片。

1 BPM处理器的总体架构和硬件设计

HALF是周长为480 m、能量为2.2 GeV的第4代衍射极限储存环,具有超低的发射度和极小的束团尺寸,其主要设计参数列于表1。为满足超低发射度和超高亮度要求,束流轨道抖动不能超过束流尺寸的10%,即水平方向不超过500 nm、垂直方向不超过200 nm,这就需要具有百纳米分辨率BPM系统实时监测轨道变化。目前HALF尚在预研阶段,为使研制的样机能在HLS Ⅱ上进行束流实验验证,BPM处理器的参数基于HLS Ⅱ的参数设计。根据软件无线电技术[6],在此设计上稍作修改即可适用于HALF储存环。HLS Ⅱ的高频频率为204 MHz、回旋频率为4.533 MHz,通过电缆输入BPM处理器的BPM感应信号是重复频率为204 MHz的窄脉冲信号[7]。为减小高频腔的干扰,设计中选择二次谐波(408 MHz)作为处理信号。

表1 HALF和HLS Ⅱ储存环的主要参数Table 1 Parameter of storage ring of HALF and HLS Ⅱ

BPM处理器总体设计如图1所示,主要包括导频模块、模拟前端模块、数字处理模块和嵌入式工控模块。导频模块置于BPM电极附近,4路BPM电极感应信号首先输入导频模块,分别与导频信号组合后经过同轴电缆传输到模拟前端模块。导频信号与4路输入信号经过相同的电缆和模拟通道,可消除因温度变化等因素导致的通道增益的不一致,进而维持BPM处理器的长时间稳定性。模拟前端模块包括4个相同的信号调理通道,完成输入信号的幅度调整与滤波功能,提高BPM处理器的动态范围。数字处理模块集成了ADC、FPGA、DDR3等,ADC完成信号带通采样,FPGA实现数字信号处理算法与数据传输逻辑,DDR3用于数据存储。嵌入式工控模块集成了龙芯2K1000、千兆以太网(GbE)、DDR3等,通过GbE与数字处理模块通信,接收束流位置信息,并与加速器控制系统通信,提高系统的可拓展性。

图1 BPM处理器总体设计Fig.1 Overall design of BPM processor

1.1 导频模块

导频模块在补偿通道不一致性、模块自检等方面有多种应用。参考Elettra的导频前端[8],本研究导频模块的电路设计如图2所示。为有效补偿通道的不一致性,导频补偿信号由高稳低噪恒温晶振经过锁相环产生,幅度可调,频率为410.975 MHz,在待测束流主频(408 MHz)的TBT数据带宽(4.533 MHz)之外,后续处理中可被滤除。BPM电极感应信号首先进入一中心频率408 MHz、带宽10 MHz的LC带通滤波器。该滤波器具有插入损耗低、远端带外抑制比良好、通带平坦、温漂系数小、承受功率大等优点,用于滤除噪声信号成分。滤波后的输入信号与导频信号组合,经过中心频率为408 MHz的带通滤波器后,通过同轴电缆传输到远端的模拟前端模块。

图2 导频模块示意图Fig.2 Diagram of pilot-tone module

1.2 模拟前端模块

模拟前端电路设计如图3所示,主要包括4路相同的信号调理通道,用来完成4路电极信号的幅度调整和滤波功能。来自导频模块的组合信号首先进入一中心频率408 MHz、带宽10 MHz的4阶LC带通滤波器,用于滤除噪声信号成分。为提高BPM处理器的动态范围,每个信号调理通道设计了2级放大电路,即可选放大电路和固定放大电路。可选放大电路部分有2个可选分支,即放大电路分支和信号直通分支。放大支路包括1个增益约32 dB的放大器和1个低通滤波器,低通滤波器用于滤除由放大器引入的信号谐波。通过开关控制,大输入信号通过直通分支,而小信号通过放大分支得到约30 dB的增益。固定放大电路由2级放大器(每级增益为22 dB)与2个RFSA3715数字步进衰减器组成。数字衰减器调节步进为0.25 dB,单个动态可调范围为0~31.75 dB,分别用于调整4通道之间的增益一致性和通道增益倍数。另外2个带通滤波器是声表滤波器,其中心频率为408 MHz、带宽为10 MHz,用于滤除射频通道的带外噪声和非线性失真。模拟前端模块采用FR-4四层复合材料制成,每个通道最大增益约为63 dB、动态可调范围为0~63 dB、分辨率为0.25 dB。

1.3 数字处理模块

数字处理模块主要完成模拟信号的ADC采样、数据处理和数据传输。设计中的芯片全部选择国产芯片,主要芯片(型号)信息如下:FPGA(SMQ7K325T-FFG900)、DDR3(SM41J256M16M),深圳市国微电子有限公司;ADC(YA16D125),苏州云芯微电子科技有限公司;232收发器(AST3232AE)、开关电源(AST4644I、AST51200-DRCR),深圳市雅创芯瀚电子科技有限公司;时钟芯片(GM4526C),成都振芯科技股份有限公司;千兆以太网芯片(JEM88E1111HV),中国电子科技集团公司第三十二研究所。

ADC选用苏州云芯微电子科技有限公司的YA16D125,是双通道、16位、125MSPS模数转换器,适合高频率、高动态范围的信号采样。ADC采样信号由FPGA内集成的数字信号处理算法进一步处理获得数据速率分别为4.533 MHz、10 kHz和10 Hz的TBT数据、FA数据和SA数据。FPGA是数字处理模块最核心的元件,选用深圳市国微电子有限公司SMQ7K325T-FFG900,内部可编程资源非常丰富,包括840个DSP、326 080个逻辑单元、445个BRAM等,适合BPM处理器的高性能、大数量逻辑运算要求。此外,数字处理模块还集成了SM41J256M16M型4Gb DDR3、AST25QU256MX型256Mb SPI Flash等用于数据及代码存储;集成了SFP光口快速传输FA数据,可拓展应用到快轨道反馈系统;集成的千兆网口支持与嵌入式工控模块通信,可批量读取ADC原始数据和TBT数据用于物理分析,也可实时传输SA数据和控制信号等。

1.4 嵌入式工控模块

嵌入式工控模块通过千兆以太网(GbE)与数字处理模块通信,将得到的束流位置信息发送到加速器控制系统。其核心元件是基于MIPS架构的龙芯2K1000芯片,板载SPI Flash用于存储代码,DDR3用于存储代码和数据,2个千兆网口分别与数字处理模块和加速器控制系统通信。EPICS广泛应用于加速器控制系统,由于原生EPICS仅支持VxWorks、x86、ARM等架构,为适应MIPS架构,修改了EPICS base包的配置文件。并基于EPICS架构开发了IOC程序,与数字处理模块进行数据交互,提高了系统的可拓展性。

图3 模拟前端模块示意图Fig.3 Diagram of analog front-end module

2 数字信号处理算法设计

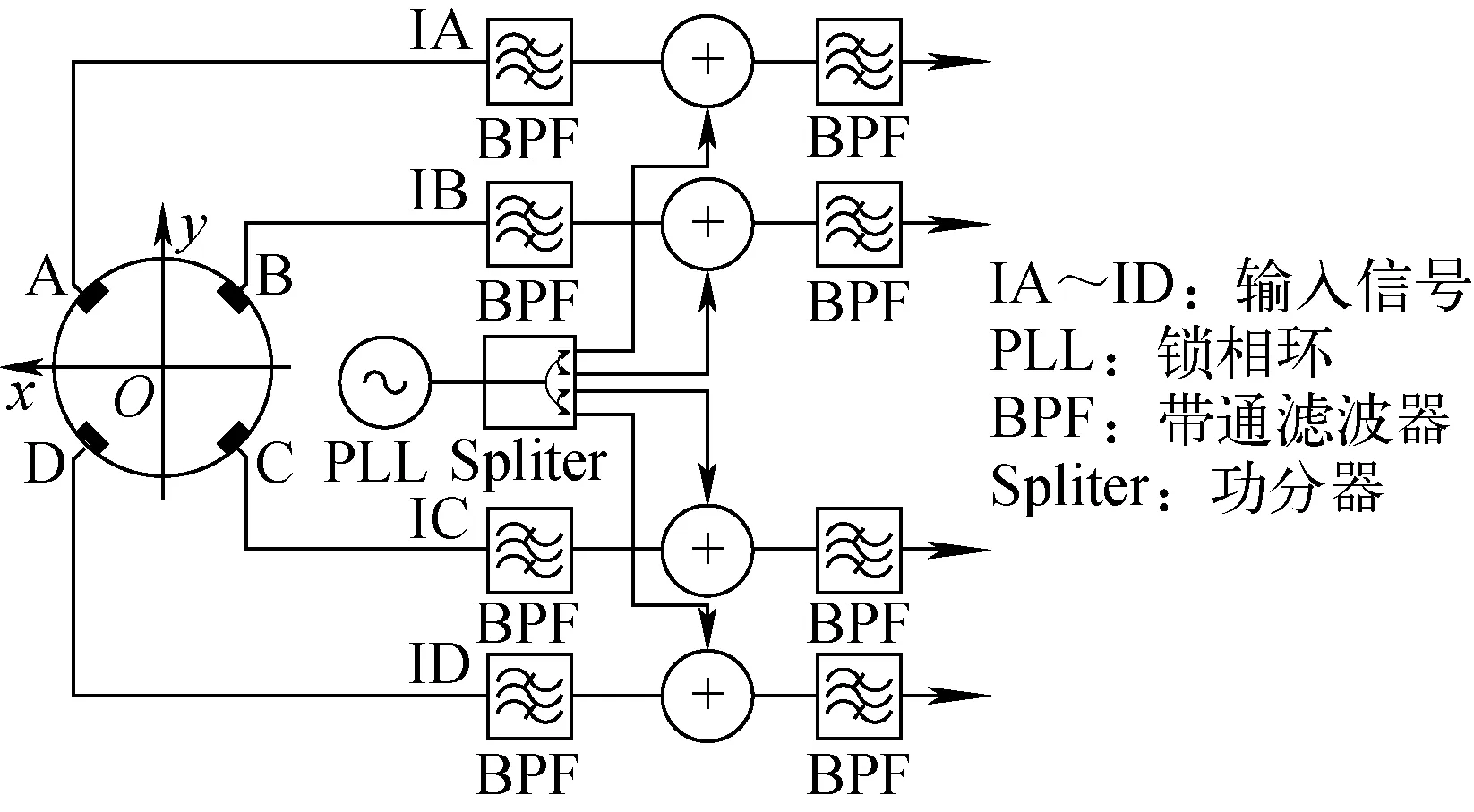

位置测量的数字信号处理算法都集成在FPGA上。BPM电极信号经过模拟前端处理后,得到的是408 MHz输入信号与410.975 MHz导频信号叠加的4路组合信号。为获得束流位置信息,4路组合信号在数字模块的处理流程如图4所示。输入信号经过ADC数字化后,在FPGA内经过数字下变频模块、滤波抽取模块、CORDIC(坐标旋转数字计算)模块、补偿模块、差比和算法等处理后得到TBT数据、FA数据和SA数据。

1) ADC采样

输入到ADC的信号是经过模拟前端调理后的射频带通信号,其中心频率为408 MHz、带宽为10 MHz,包含410.975 MHz的导频信号分量。本文采用带通采样处理射频带通信号,考虑到采样时钟需要是回旋频率的整数倍,采样频率fs设计为108.8 MHz。每路采样后,得到的是27.2 MHz与24.225 MHz组合的数字中频信号,带通采样的频谱折叠示意图如图5所示。

图4 数字信号处理流程Fig.4 Diagram of digital signal processing

图5 带通采样的频谱折叠示意图Fig.5 Spectrum aliasing diagram of bandpass sampling

2) 数字下变频

通过数控振荡器(NCO)产生1对正交信号,与中频信号混频,将信号的中心频率搬移到基带,得到2路正交信号I、Q[9-10]。ADC采样得到的数字中频信号的频率分量主要是27.2 MHz和24.225 MHz,因此,本设计中需要2个NCO,分别产生27.2 MHz和24.225 MHz两对正交信号。假设束流信号采样后27.2 MHz中频信号为A0cos(ω0t-φ0),导频信号采样后24.225 MHz中频信号为A1cos(ω1t-φ1),其中A0、A1是信号幅度,-φ0、-φ1是初始相位,ω0=27.2 MHz、ω1=24.225 MHz,则ADC原始数据可表示为A0cos(ω0t-φ0)+A1cos(ω1t-φ1),与NCO_0产生的两路正交信号cos(ω0t)、sin(ω0t)混频如下:

(A0cos(ω0t-φ0)+A1cos(ω1t-φ1))·

(1)

(A0cos(ω0t-φ0)+A1cos(ω1t-φ1))·

(2)

3) 滤波抽取

为提取数据中的有效频率成分并降低数据速率,滤波抽取是BPM处理器数字信号处理不可或缺的一部分。由于采样频率是108.8 MHz,每个回旋周期有24点数据,为满足TBT数据的数据速率要求,数字下变频得到的零中频信号需要抽取24倍。为避免抽取过程中信号高频成分发生混叠,在抽取前需要预滤波[11]。积分梳状(CIC)滤波器和有限长单位冲激响应(FIR)滤波器是最常用的抽取滤波器[12]。CIC滤波器实现简单,加法器就足够,适合高速率大规模抽取场景,常用作第1级抽取滤波器[13]。因此,第1级采用CIC滤波器抽取12倍,第2级选用FIR滤波器抽取2倍。设计中CIC抽取滤波器采用3级Hogenauer结构,如图6所示。

图6 3级Hogenauer CIC抽取滤波器结构示意图Fig.6 Schematic diagram of three-stage Hogenauer CIC decimation filter

4) CORDIC模块

滤波抽取模块不仅降低了零中频正交信号的数据速率,也滤除了数字下变频引入的其他谐波成分,得到的是2对I、Q正交信号。依据CORDIC在圆周坐标系的向量模式,这2对正交信号可分别计算输入信号和导频信号的幅度,至此BPM输入信号和导频信号又从组合信号中分离出来。CORDIC算法通过基本的加和移位运算代替三角函数、乘法、开方、指数等复杂运算,降低了硬件实现难度,适合应用于FPGA[14]。CORDIC幅度计算流程图示于图7,由于CORDIC算法适用于-99°~99°之间矢量(I,Q)的幅度计算[15],象限调整模块将(I,Q)调整到第一、四象限,然后是7级CORDIC迭代单元。在FPGA中,7级CORDIC迭代单元结合23位小数位长,有效提高了幅度计算精度,同时采用流水线结构提高了系统速度[16]。

5) 基于导频补偿的差比和算法

差比和算法常用于束流位置计算,如式(3)[17-18]所示。

(3)

其中:x、y为位置坐标;Kx、Ky为位置系数;VA、VB、VC、VD为4路BPM电极感应信号的幅度;Xoff、Yoff为位置偏移。设计中,引入导频信号,并使之与输入信号经过同一模拟通道。假设输入信号幅度分别为VA、VB、VC、VD,导频信号幅度为VP,4路模拟通道的传递函数分别为H1、H2、H3、H4,模拟通道输出的信号幅度分别为VAO、VBO、VCO、VDO,4个模拟通道输出的导频信号幅度为VAP、VBP、VCP、VDP,则有:

图7 CORDIC幅度计算流程图Fig.7 Flow of CORDIC amplitude calculation

VAO=VAH1,VBO=VBH2,

VCO=VCH3,VDO=VDH4

(4)

(5)

(6)

由式(6)可见,导频补偿后的差比和算法可消除通道增益不一致给位置计算带来的影响。

6) TBT、FA、SA数据

基于前文CORDIC模块得到的射频信号幅度和导频信号幅度,采用导频补偿后的差比和算法,可计算TBT数据。TBT数据的数据速率为4.533 MHz,如图4所示,10 kHz的FA数据由TBT数据抽取450倍获得,第1级选用CIC滤波器抽取90倍,第2级采用FIR滤波器抽取5倍;10 Hz的SA数据由FA数据进一步抽取1 000倍得到,第1级选择CIC滤波器抽取100倍,第2级采用FIR滤波器抽取10倍。

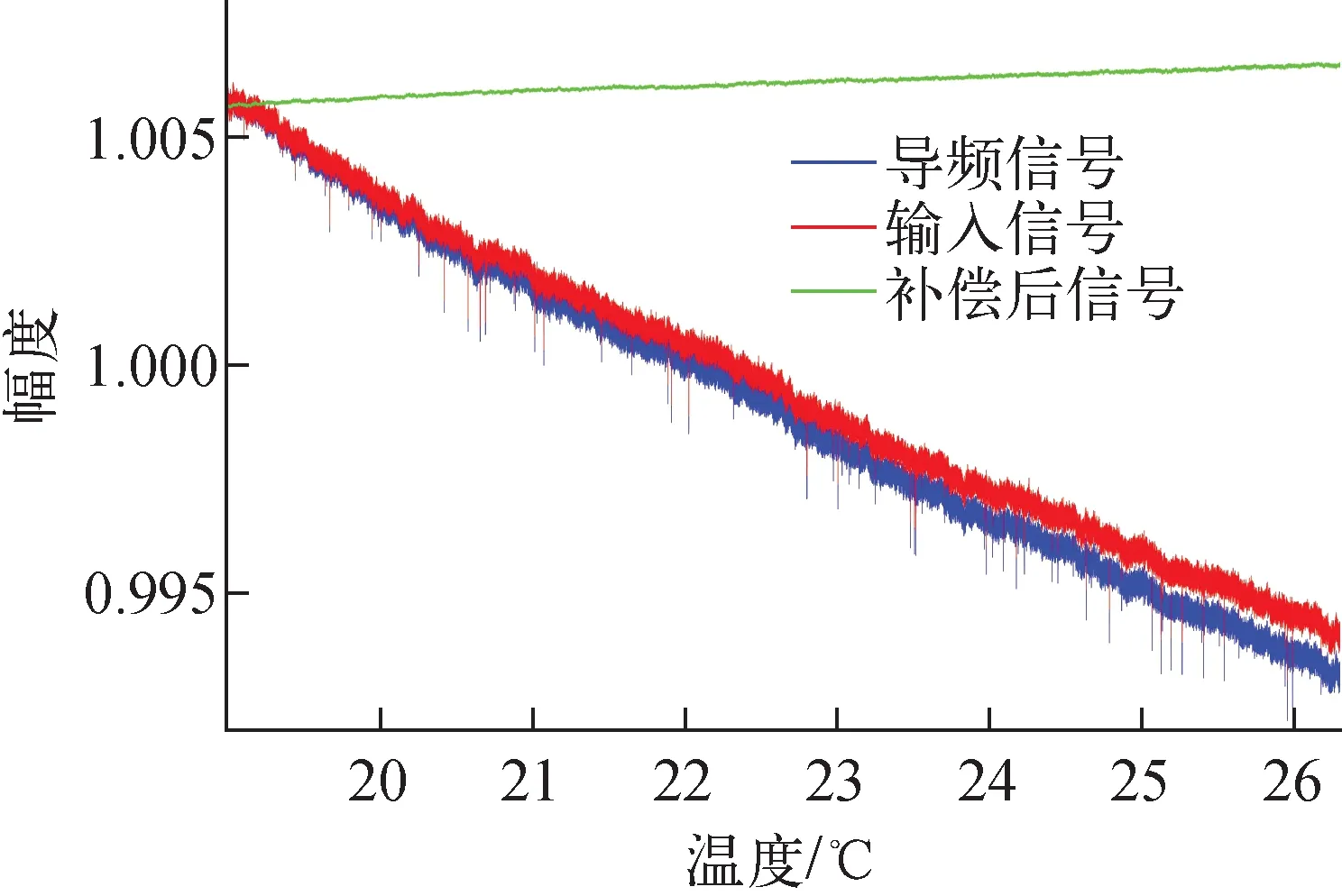

为测试导频的补偿功能,设计了1个数字信号处理幅度测试本。其信号处理流程如图8所示,对于其中1个通道,前期处理与BPM处理器的数字信号处理算法相同,有数字下变频模块、滤波抽取模块、CORDIC模块。对CORDIC模块得到的RF信号幅度和导频信号幅度分别进一步抽取450 000倍,得到数据速率为10 Hz的信号幅度,再计算该通道信号幅度补偿结果。此测试本直接以较低的数据速率(10 Hz)输出RF信号幅度、导频信号幅度和幅度补偿结果,方便数据存储以及分析导频补偿信号对长时间温漂的抑制效果。

图8 测试导频补偿功能的数字信号处理示意图Fig.8 Diagram of digital signal processing for pilot-tone test

3 测试

BPM处理器测试包括离线测试与束流测试。离线测试包括模拟前端的性能测试、导频功能测试,以及BPM处理器分辨率测试,束流测试完成基于HLS Ⅱ储存环的在线束流位置监测。

3.1 离线测试

1) 模拟前端测试

图9为用网络分析仪KeysightE5071C测试的模拟前端通道A的S21参数,调节输入信号频率从378 MHz到438 MHz,输出信号幅度归一化分析后可直观看到模拟前端电路的中心频率是408 MHz、带宽为10 MHz,带外噪声抑制好于75 dB。模拟前端的通道间隔离度对导频补偿机制很重要,依次给其中1个通道输入频率408 MHz、功率-2 dBm的信号而其他通道连接50 Ω的匹配电阻,通过测量每个通道的输出结果来计算通道间隔离度。测试结果列于表2,通道间隔离度好于76 dB。

图9 模拟前端通道A的幅频响应Fig.9 Amplitude-frequency response of channel A in RF front end

2) 导频功能测试

在实验室搭建了离线测试系统,如图10所示,以测试导频的补偿功能和BPM处理器的分辨率。频率综合系统提供408 MHz的RF信号和108.8 MHz的时钟信号,功分器将RF信号分成4路后作为导频模块的输入信号。

表2 模拟前端电路通道间隔离度Table 2 Isolation between channels in RF front end

图10 离线测试系统Fig.10 Diagram of offline test system

图11 A通道信号幅度随温度的变化Fig.11 Signal amplitude variation with temperature of channel A

为方便测试导频的补偿功能,前文设计了一个数字信号处理幅度测试本。基于该测试本,可分别获得输入信号、导频补偿信号的信号幅度以及补偿后的效果。调节实验室温度为20~26 ℃,通道A的测试结果如图11所示,输入信号幅度变化0.013,导频信号幅度变化0.014,补偿后幅度变化0.001。导频信号可有效补偿温度对射频输入信号的影响,可抑制92.308%温度漂移带来的影响。调节实验室温度为20~26 ℃,基于BPM处理器的数字信号处理算法,分别获得带有导频补偿算法和不带导频补偿算法的SA数据,结果如图12所示。带有导频补偿算法的x、y方向SA数据位置分辨率分别为65.268、58.075 nm,不带导频补偿算法的SA数据位置分辨率分别为161.800、170.370 nm,导频补偿机制抑制了温漂对位置计算的影响,提高了BPM处理器的长期稳定性。

图12 SA数据随温度的变化Fig.12 SA data variation with temperature

图13 TBT、FA和SA数据的位置分辨率Fig.13 Position resolutions of TBT data, FA data and SA data

3) 分辨率测试

测试系统如图10所示,调节输入射频信号幅度从-55 dBm到5 dBm,分别记录并分析4.533 MHz TBT数据(20 s)、10 kHz FA数据(10 min)和10 Hz SA数据(8 h)。测试结果示于图13。由图13可见,BPM处理器位置系数Kx、Ky取8 mm时,TBT数据分辨率好于400 nm,FA数据分辨率好于120 nm,SA数据分辨率好于70 nm,满足设计要求。

3.2 束流测试

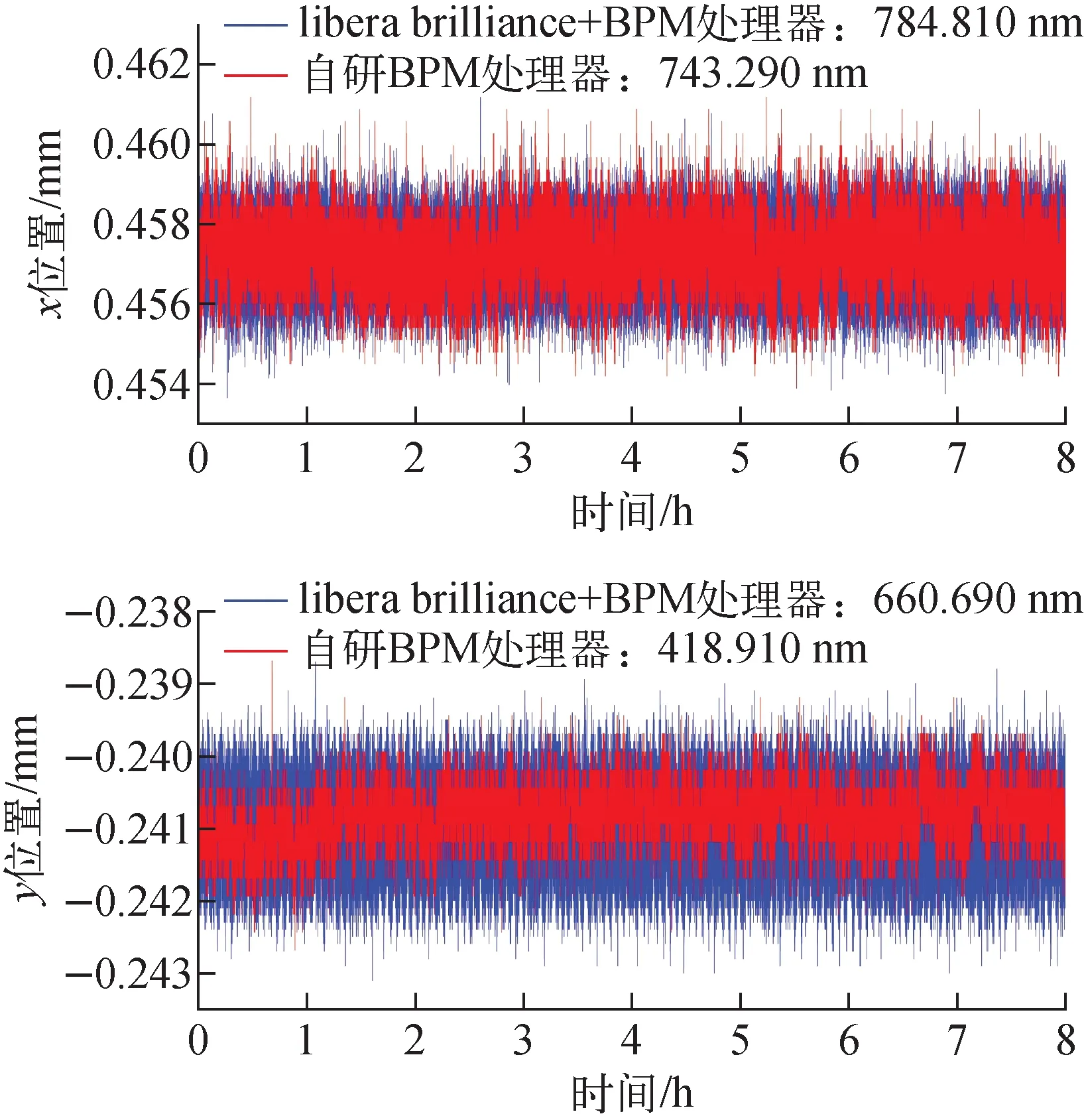

为验证BPM处理器在线监测储存环束流轨道的功能,基于HLS Ⅱ储存环进行了束流实验。 HLS Ⅱ运行在top-off模式,流强为400 mA,BPM位置系数Kx、Ky分别为20.088、16.381 mm[19]。将HLS Ⅱ的备份BPM信号连接到自研BPM处理器,记录8 h的SA数据,并将测试结果与附近IVU:BPM1使用IT公司libera brilliance+BPM处理器的测量结果进行对比。两者的测量结果及其分布直方图如图14、15所示。可见,自研BPM处理器测得的束流轨道在x、y方向的抖动RMS分别为743.290、418.910 nm;libera brilliance+BPM处理器测得的束流轨道的抖动RMS分别为784.810、660.690 nm。

图14 开启慢轨道反馈系统的SA数据测试结果Fig.14 Test result of SA data with slow orbit feedback system on

机器研究期间,关闭HLS Ⅱ储存环的慢轨道反馈系统,自研BPM处理器与libera brilliance+BPM处理器测量结果如图16所示。libera brilliance+是IVU:BPM1的测量结果,自研BPM处理器是附近备用BPM的测量结果,可见两者束流的变化趋势与变化范围一致,进一步验证了自研BPM处理器在真实束流测试中可有效监测束流轨道变化。

4 结论

本文基于HALF的技术需求,自主设计研制了基于国产化芯片的带有导频补偿机制的BPM处理器,并完成了离线测试与束流测试。分辨率测试结果表明,输入信号在-55~5 dBm之间时,BPM处理器的FA数据和SA数据的分辨率分别好于120 nm和70 nm,满足HALF要求;离线测试结果表明,导频信号可有效补偿模拟通道之间的不一致性,提高BPM处理器的长期稳定性;基于HLS Ⅱ的束流实验结果,验证了自研BPM处理器满足储存环束流位置监测的日常运行需求。自研BPM处理器基于国产化芯片开发,其经验为未来更多电子学系统国产化提供了思路和技术积累。此外,导频模块需置于BPM附近,因而下一步需继续优化提高导频模块的抗电磁干扰与抗辐射能力。

图15 开启慢轨道反馈系统的SA数据分布直方图Fig.15 Distribution histogram of SA data with slow orbit feedback system on

图16 关闭慢轨道反馈系统的SA数据测试结果Fig.16 Test results of SA data with slow orbit feedback system off