基于蚁狮算法的整流器高速信号完整性检测方法*

唐思均李源彬

(1.宜宾职业技术学院电子信息与人工智能学院,四川 宜宾 644000;2.四川农业大学信息工程学院,四川 雅安 625014)

整流器是一种能够改变交、直流电的装置,能够为电气电路提供电能和无线电信号的侦测等。因为它被广泛地应用于各种各样的整流电源内,所以需要转变的电压也从几十至几千伏、电流从几安至几千安不等。将整流器应用在高速电路中时,它的信号完整性非常重要。通过检测信号传输路径质量,能够确定整流器信号的完整性是否良好。传输路径不仅是电路的连接金属线,还可以是整体电气元件,同时也可以是一些其他的媒质[1-2]。整流器高速信号的反射、串扰问题始终影响信号完整性检测效果,相关学者对此问题进行了研究,取得了一定的进展。

陈涛等人[3]提出一种双重化脉冲整流器多管开路故障快速诊断方法,通过StarSim 软件获取整流器电压变化,利用原型控制器分析门极信号突变情况,实现整流器多管开路故障快速诊断,此方法能够提升故障定位准确率,避免负载扰动影响。王英等人[4]提出基于改进谱峭度与电流均值的牵引整流器开路故障诊断方法,利用IGBT 开路计算电流均值,利用电流突变特征获取整流器故障类别,依据改进谱峭度实现整流器开路故障诊断。此方法能够获取较高的故障诊断准确率,但是诊断过程比较复杂,诊断效果较高。

高速信号如果不完整性,并不是某种单一因素造成的,而是整体系统内,通过多种不同因素所导致的。若信号不能正常响应,就不能让系统长期处于稳定的状态下进行工作,这时会发生信号完整性缺失问题[2]。而本文提出的基于蚁狮算法的整流器高速信号完整性检测方法,通过模拟蚁狮生物的行为生态,计算整流器内电阻值,通过置零整流器内的串扰以及反射系数,得到整流器内所接收信号向量的所有分量,从而明确整流器内高速信号是否完整。

1 蚁狮算法数据分析

整流器高速信号的不完整,会导致整体电路不能稳定地工作,而蚁狮算法作为一种启发式优化方法,极为适用非凸优化问题,可不断迭代搜索整流器内各信号信息。蚁狮在沙子表面挖好洞穴以后,坐等猎物出现。制作的陷阱形状能够影响到猎物捕捉,使其无法从洞口爬出,同时,便于下次捕捉,计算蚂蚁掉落陷阱的过程即计算整流器内真实信号和干扰数据的过程[3]。

(1)蚂蚁的随机行动分析

具体蚂蚁行动建模公式为:

式中:n代表最大迭代的个数,S代表累积和,t代表迭代的步长,r(t)代表随机的函数,具体公式为:

式中:rand 代表服从[0,1]内均匀分布的随机数。

蚂蚁行动位置是随机的,所以随机行走要对其归一化处理,方便搜索空间中寻求最佳解。具体公式为:

式中:ai以及di代表第i个变量最小以及最大随机的步数。分别代表第t次迭代的第i个变量最小以及最大值。

(2)蚂蚁行动到陷阱

蚂蚁随机行动至陷阱位置,或受到陷阱位置的蚁狮M以及d向量控制,具体公式为:

(3)满意滑落陷阱[4]

蚂蚁一旦滑落陷阱,这时蚁狮会从洞口的中心位置对外抛沙,从而使蚂蚁滑至洞底,使蚂蚁的随机行走半径降低,具体公式为:

式中:t以及T代表目前迭代次数以及最大的迭代次数。ω代表与目前迭代次数所相关常数值。

(4)更新陷阱

在蚁狮捕捉猎物后会在沙子下方食用猎物,而适应能力较强的蚁狮能够捕捉的猎物会更多,这就说明蚁狮捕捉完猎物后,要更新下个陷阱,具体公式为:

(5)蚁狮精英的选取

蚁狮精英的定义,是每次更新陷阱在最优区域的蚁狮,就是适应蚁狮,在每一次迭代的过程内,会影响蚁狮行为,具体公式为:

2 整流器高速信号的完整性检测

2.1 整流器的高速信号传输线分析

将整流器内各参数代入蚁狮算法中,计算整流器内电阻值,从而获得整流器内真实的特征阻抗Z0,设置点P作为整流器中任意的一个点。C1、L1、R1分别代表等效电容、电感、电阻。R2代表漏电流所体现出电阻,该阻值接近无限大。而传输线的静态电阻R1非常小,基本忽略不计,具体公式为:

该情况的特征阻抗是无损阻抗。某个信号10%~90%上升以及下降的时间是Tr,那么此信号在整流器内的走线延迟是D,此信号的有效长度是L,具体公式为:

信号处于导线上的传输端比L/6 大时,要采用传输线理论。这就说明在传输距离至一定程度时,才能够采用传输线理论,反之,认定此段线路上仅为一个点,将该信号当成普通信号进行处理[6]。

2.2 高速信号的完整性分析

高速信号的完整性,是作为整体系统的可靠性保障,因为高速信号内含有较高的频率,系统电气参数变化较大,出现许多高速信号的特有状况,其中包含:串扰、发射等[7]。

2.2.1 发射产生机制

实际传输线驱动器的输出阻抗并不是0,互连线传输与阻抗会形成分压器,而在互连线上的入射波,是驱动器电压的部分,具体公式为:

式中:Vinc代表入射电压,Vs代表驱动器内的电压,Rs代表驱动器的内阻,z0代表互连线的阻抗[8]。

在高速信号能够传输至负载端上或是任意阻抗的突变区域时,分界面的电流以及电压会以连续的形式构成。而对于阻抗分界面的两侧,存在V1=V2,I1=I2,且V1/I1=Z1,V2/I2=Z2,因此在阻抗产生突变时,就是Z1≠Z2时,那么5 个等式不会同时成立,而为了令系统保持整体平衡,要在分界面位置生成反射回源端电压[9]。

在入射电压Vinc通过互连线进行传输,直到负载端时,由于阻抗突变情况,会生成反射电压Vrefl,这时的传输电压Vtrans则会继续向前传播,而分界面的两侧电压则要满足公式为:

相同的是,分界面两侧的电流要满足条件具体公式为:

分界面两侧的电压以及电流,需要满足的关系公式,分别为:

把式(16)、式(17)以及式(18)代入式(15)内,具体可以得到公式为:

将(14)代入式(19)内,取消Vtrans且进行整理获得公式为:

可将入射电压和发射电压比,定义成反射系数,这时就能够求出传输系数,具体公式为:

2.2.2 串扰产生机制

2.2.2.1 容性串扰

设置cm代表单位长度互容,是沿着两条传输线进行分布的,在两条导线距离足够近的时候,电容会变得非常大,且令攻击线的耦合能量影响到受害线[10]。

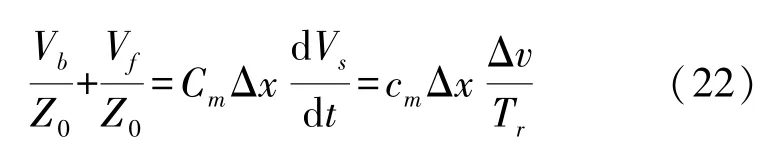

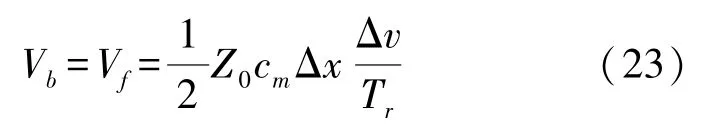

在传输线中间截取一段Δx,而高速信号的上升沿在经过该段时,将位移电流注入受害线内。能够获得公式为:

式中:Δx代表驱动波形的幅度,Tr代表波形上升的时间,通过电压连续性可以获得Vb=Vf,具体公式为:

因为前向串扰传播的方向以及速度和信号自身的相同,在受害线中的所有点前向串扰相加,而且要在相同的时间内抵达远端。通过式(23)能够获得,长度是VFE传输线,处于远端总噪声公式为:

信号上升时间是Tr一半。式(23)内距离为Δx=,Vp代表相速度,将其代入至式(23),获得近端的噪声公式为:

根据上述过程可知,信号串扰能够影响电容值与脉冲信号时宽,而且远端以及近端脉冲的极性全是正向的。

2.2.2.2 感性串扰

截取传输线中的一段,这时攻击线经过电流,互感线路会感受到串联电压,获得串联电压的计算公式为:

上述两种串扰的推导方法基本相同,其中,感性耦合能够随攻击信号上升沿持续传播,而在相同的时间内会抵达至远端,此时攻击信号传播的方向则会与反向串扰位于相反状态,进而生成积累噪声的幅度,具体公式为:

感性串扰处于近端以及远端的波形上,与容性串扰的机制类似。

2.2.2.3 总串扰

通常情况下,感性串扰和容性串扰在同一时间出现,将式(26)和式(31)相加,能够获得近端串扰公式:

将式(24)和式(30)相加,能够获得远端串扰公式:

通过上述公式能够看出,近端串扰是一直存在的,无法清除。而远端串扰,由于二者的串扰极性相反,所以会相互抵消一部分,而当时,则会全部抵消,而实际的整流器,不会存在理想状态,所以远端串扰无法清除[11]。

2.3 信号检测方法

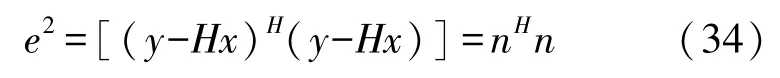

通过强制将整流器信道串扰以及反射进行干扰置零。通过迫零矩阵实现线性加权,处理高速信号的向量,再对加权后接受信号向量所有分量进行检测,获取发射符号的向量。

利用最小二乘法准则,对噪声误差e2定义,具体可得到公式为:

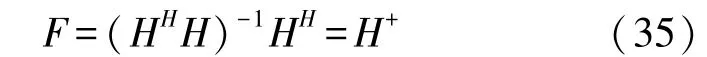

求导上式,令一阶导数是0,二阶导数比0 大,以此能够获得e2极小值估计,从而获得高速信号迫零矩阵公式为:

式中:H+代表已知信道矩阵H广义的逆矩阵。

利用F左乘接收信号的向量y,能够获得利用此迫零方法估计接收高速信号的向量,具体公式为:

利用式(34)确认估计矩阵F,能够完全去掉内发射向量的所有分量间互相干扰。以此可以完成高速信号的完整性检测[12]。

3 实验仿真证明

3.1 实验1

实验环境选择CPU 为2.3GHz、内存为4GB、操作系统为Window10,直流母线的电压是220 V、帧数为2 000 帧、发射功率为1、开关的频率是1.75 kHz的三相量电平的PWM(Pulse width modulation)整流器系统进行实验,该整流器的高速信号为周期性的,在脉冲为线性的调频信号。具体整流器的高速信号幅值变化曲线如图1 所示。

图1 整流器高速信号幅值变化检测

从图1 能够看出,在一定时间内,整流器的高速信号幅值呈周期变化。本文方法与实际信号幅值变化情况基本一致,而双重化脉冲方法的整流器高速信号幅值变化明显落后于实际情况,表明本文方法进行整流器高速信号完整性检测时的实时性更好。这是因为引入蚁狮算法,确定传输线间的能量耦合串扰,获得加权接收信号向量的所有分量,使得检测过程中即使出现冗余干扰也能不断迭代搜索最优解,可靠性高。

3.2 实验2

为了进一步证明本文检测方法的效果,将该信号通过人为的方式进行外界干扰,使其发生轻微故障,然后采用本文方法,对其进行检测,验证高速信号是否完整。具体如图2 所示:

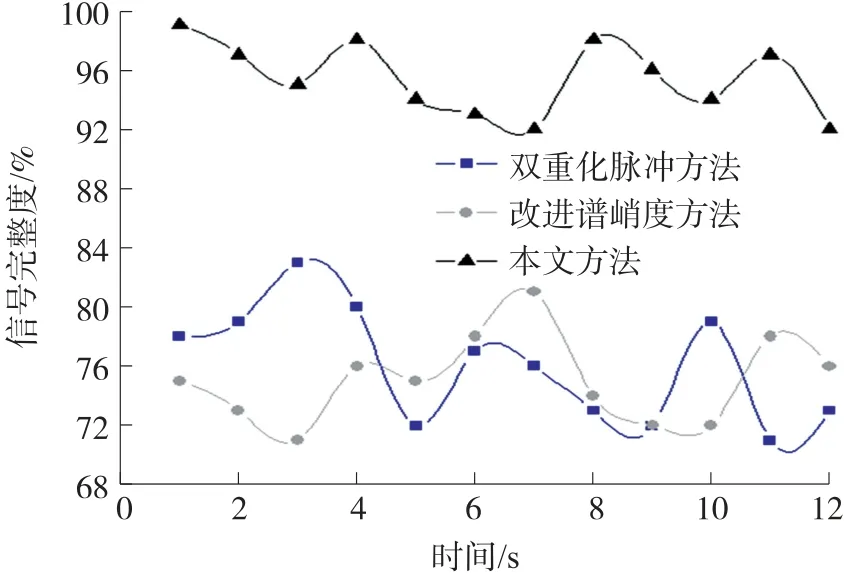

图2 不同方法下检测高速信号完整度

通过观察图2 能够看出,随着运行时间的增加,不同方法下高速信号完整度随之变化。当运行时间为2 s 时,双重化脉冲方法的高速信号完整度为79%,改进谱峭度的高速信号完整度为73%,本文方法的高速信号完整度为97%。当运行时间为8 s 时,双重化脉冲方法的高速信号完整度为73%,改进谱峭度的高速信号完整度为74%,本文方法的高速信号完整度为98%,说明本文方法能够获得完整的高速信号。这是因为本文引入了蚁狮算法分析相邻传输线接近时磁场边缘与信号电场的相互影响,准确计算整流器内的电阻值以获取特征阻抗,实现不同频域的干扰信号对消,减少了高速信号传输完整性检测干扰因素,使得高速信号的完整度得到提升。

4 结论

本文提出基于蚁狮算法的整流器高速信号完整性检测方法,通过置零反射系数以及串扰系数,使用迫零矩阵完成线性加权,处理高速信号的向量,通过加权后接受信号向量的所有分量,实现信号检测,不过由于整流器造成信号不完整的方式有很多,所以本文还需要进一步努力,研究其他造成信号不完整的原因,从而完成检测。