高介薄型陶瓷芯片电容制备工艺研究

王春富 ,黎俊宇 ,李彦睿 ,王文博 ,张 健 ,秦跃利 ,钟朝位

(1.中国电子科技集团公司第二十九研究所,四川 成都 610036;2.中国移动通信集团海南有限公司,海南 海口 570000;3.电子科技大学,四川 成都 610054)

现代信息通信技术,要求实现电子系统中关键组成器件的小型化、轻量化以满足应用需求。高介薄型陶瓷芯片电容具有尺寸小、损耗小、容量大、温度稳定性好等特点,其在元器件表面贴装技术和微电子电路中发挥着越来越重要的作用[1-2]。

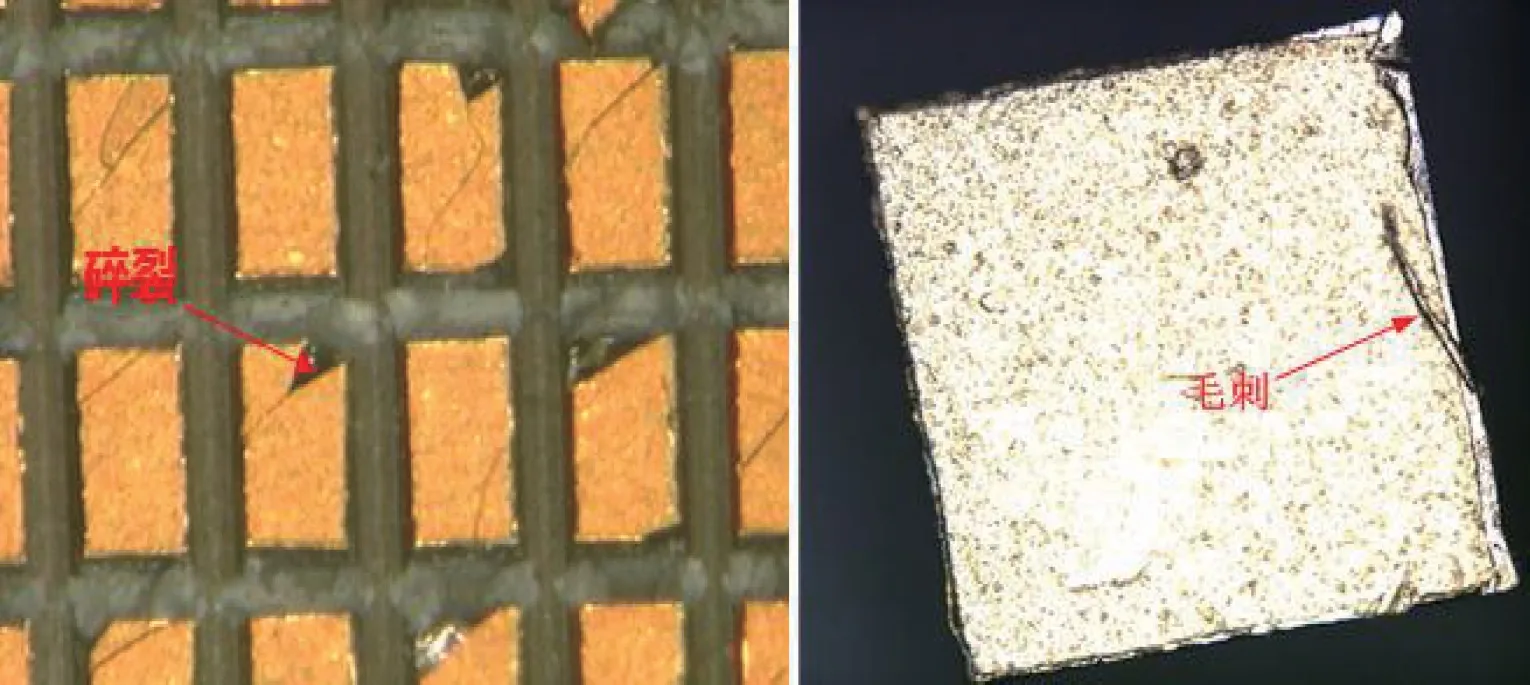

高介薄型陶瓷芯片电容的制备主要有三个关键的工艺环节,一是高介陶瓷介质基片的制备,陶瓷介质基片的特性与最终电容器表面微观形貌、电阻性能和介电性能密切相关;二是陶瓷介质基片表面的金属电极制备,也称薄膜金属化工艺,金属化工艺直接影响电容器电极的性能,对电容器性能影响非常大[1-3];最后是电容器件的精密切割,由于高介薄型陶瓷电容器基片薄、晶粒粗、脆性强,易出现碎裂、飞晶、卷边、毛刺等严重影响器件质量的现象。针对高介薄型陶瓷芯片电容的三个关键工艺环节,作者在前面的工作中已经报道了不同成型工艺对陶瓷芯片电容性能的影响[4],而本文将针对金属化工艺和电容器精密切割工艺对薄型陶瓷芯片电容性能的影响进行系统研究。

金属化工艺中,高介薄型陶瓷芯片电容的电极一般采用薄膜工艺制备,为了防止电容电极中的金属离子在电压的作用下迁移至介质内部产生漏电流导致性能恶化,通常会在陶瓷与金属之间选择合适的材料充当过渡层,过渡层既可以阻挡金属原子的迁移,又可以提高金属电极膜层的附着力,保证在后续的切割和装配过程中不会发生电极卷翘和膜层起层的问题[4-5]。本文选用高介薄型陶瓷介质材料,研究了其在金属化工艺中过渡层材料、过渡层厚度对产品绝缘性能和介电性能的影响,通过测试分析优选出较优的膜系结构,为高介薄型陶瓷芯片电容生产提供了工艺基础。

此外,为实现高介薄型陶瓷芯片电容的精密切割,本工作还从切割固定方法、载片材料选择等方面入手,优化了切割工艺,为微小器件的精密切割提供了工程指导。

1 实验

1.1 陶瓷芯片电容电极金属化

选用绝缘电阻率大于1010Ω·cm(室温,25 V),介电常数(ε)为2000,电容温度变化率ΔC/C25≤12%(-55~125 ℃),介电损耗(tanδ)≤0.01 的高介陶瓷基片材料(记为HT)为研究对象,采用三种膜系结构制备电极,分别是TiW/Au 结构、TiW/Ni/Au 结构和TaN/TiW/Au 结构,对应样品标记为A、B、C。电极制备采用磁控溅射工艺,控制膜系结构中的过渡层厚度为400 nm。电极导体Au 采用电镀加厚的方式制备,控制厚度在2 μm。介质基片金属化完成后,进行精密切割,划切成芯片电容并进行性能测试。

为表征过渡层厚度对电容性能的影响,本工作选取温度稳定性较好、制备难度较低的TiW/Au 膜系作为过渡层,控制过渡层的厚度,制备完过渡层后观察表面覆盖情况,并进行绝缘电阻偏压特性测试。

1.2 陶瓷芯片电容的精密切割

选用高速高稳定的两英寸主轴的砂轮划片机,采用不同类型的切割刀、不同转速和行进速度、不同的固定方式进行切割,切割完成后进行观察和测量。

1.3 样品测试

采用绝缘电阻测试仪测试样品的绝缘电阻;使用LCR(Agilent 4284A)测试仪测试样品的介电性能;在样品介电性能测试过程中,采用temp850 型温控箱对测试环境温度进行控制;使用扫描电子显微镜(FEI Inspect F,United Kingdom)观察样品的表面微观形貌;使用电子测量显微镜(NR 8090)观察样品的形貌并测量切割卷边尺寸。

2 结果与讨论

2.1 膜系结构中过渡层对性能的影响

选用HT 作为陶瓷介质基片,不同过渡层材料的膜系结构如表1,膜系结构中的过渡层厚度为400 nm,按表1 设定的膜系进行金属化后,进行器件的精密切割,并分别测试了高介薄型陶瓷芯片电容绝缘电阻的偏压特性和温度特性、电容量和介电损耗的温度特性。

表1 不同过渡层的膜系选择Tab.1 Film selection of different transition layers

2.1.1 膜系结构中过渡层对绝缘电阻的影响

采用不同过渡层制作的高介薄型陶瓷芯片电容,在常温下,测得其绝缘电阻偏压特性如图2 所示。当过渡层厚度都为400 nm,但过渡层材料不同时,其对应的电容器样品的绝缘电阻存在着较大的差异。C 在各个电压点的绝缘电阻都比较大[6-7],A 和B 在各个电压点的绝缘电阻值差异较小。三种不同膜系制作的样品在50 V 以下的电压下进行测试,绝缘电阻下降趋势比较平缓,但随着测试电压的升高,所有样品的绝缘电阻都出现了比较大的衰减。但相对于A 和B,C在100 V 时的绝缘电阻仍然约有8000 MΩ。综合来看,在常温下采用TaN 和TiW 作为过渡层的TaN/TiW/Au膜系制备的样品C 具有更高的绝缘电阻。

图1 陶瓷芯片电容切割毛刺Fig.1 Cutting burr of ceramic chip capacitor

图2 不同膜系对器件绝缘电阻偏压特性的影响Fig.2 Effects of different film structure on bias voltage characteristics of insulation resistance of devices

2.1.2 膜系结构中过渡层对绝缘电阻温度特性的影响

设定测试电压25 V,不同过渡层对样品绝缘电阻温度特性的影响如图3 所示。随着温度的升高,不同过渡层对应的样品的绝缘电阻都呈下降的趋势,原因是温度升高时,带电粒子热运动加剧,使通过介质内部的漏电流增大,绝缘电阻下降[8-9]。C 在80 ℃以下的绝缘电阻大于A 和B,但是随着温度上升,C 的绝缘电阻衰减速度较大;温度高于100 ℃时,A、B、C的绝缘电阻的衰减规律基本一致;150 ℃时,A、B、C 的绝缘电阻值基本相同。值得注意的是,绝缘电阻偏压特性较差的A 样品的温度特性反而比较好。即采用TiW 作为过渡层的TiW/Au 膜系制备的样品,其绝缘电阻随温度上升衰减趋势较平缓,受温度变化影响较小,具有更好的温度特性。

图3 不同膜系对器件绝缘电阻的温度特性的影响Fig.3 Effects of different film structure on temperature characteristics of insulation resistance of devices

2.1.3 膜系结构中过渡层对电容温度特性的影响

设定测试电压为1 V,测试频率为1 kHz,不同过渡层对样品电容温度特性的影响如图4 所示,由图中曲线可以看出不同过渡层膜系制备的样品,其电容随温度变化的差异不大,基本控制在-10%~13%之间,都表现出了优异的性能,C 在0 ℃以下的电容变化率略小于A 和B,即采用TaN 和TiW 作为过渡层的TaN/TiW/Au 膜系制备的样品C 电容随温度的变化最小。

图4 不同膜系对器件电容温度特性的影响Fig.4 Effects of different film structure on temperature characteristics of capacitance of devices

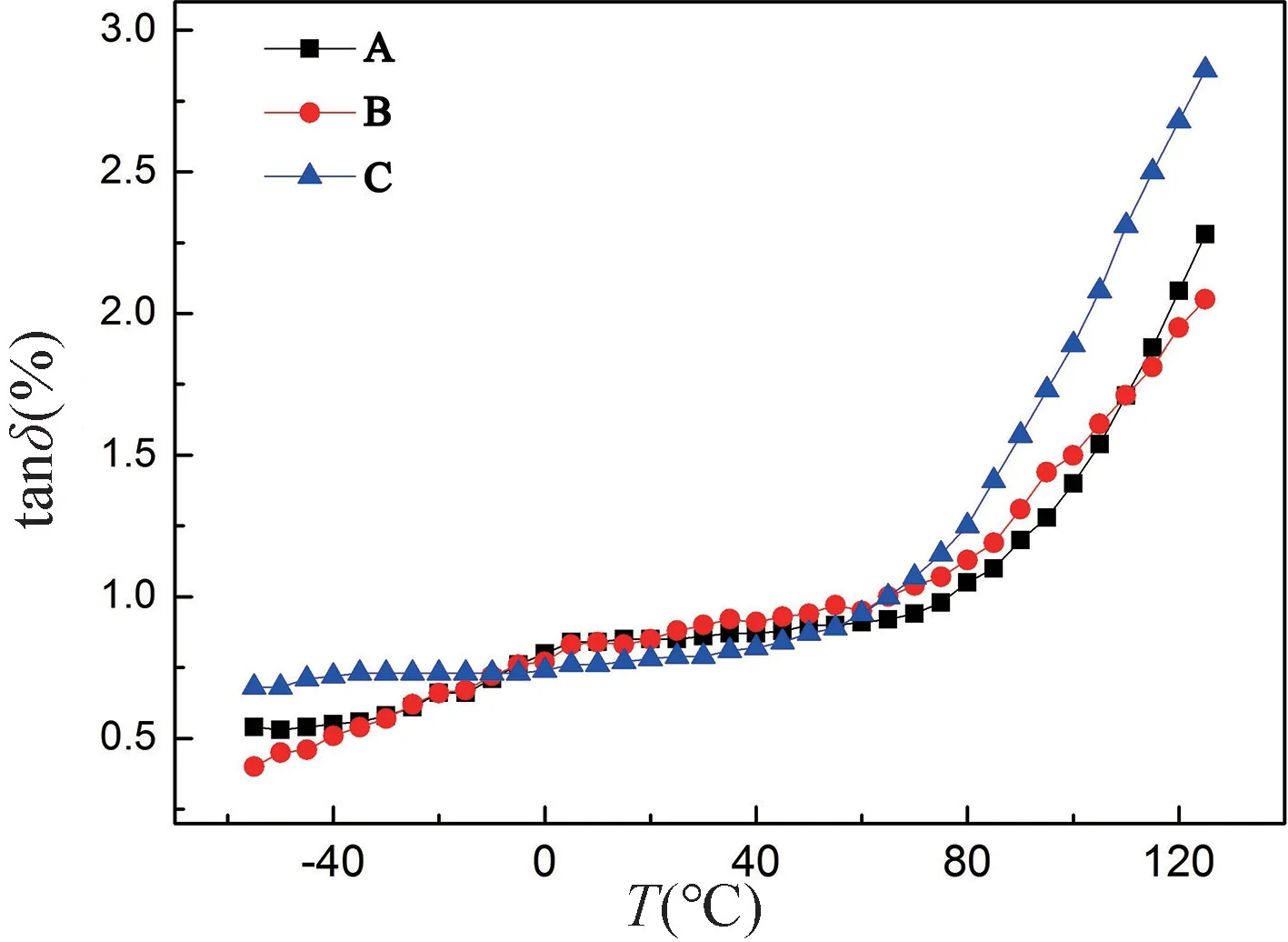

2.1.4 膜系结构中过渡层对介电损耗温度特性的影响

通过测试电容器在不同温度条件下的介电损耗,不同膜系对高介陶瓷芯片电容介电损耗的温度特性的影响如图5 所示。由图可知,不同膜系制备的电容器样品的介电损耗随温度的变化情况具有明显的差异,如样品C,在0~60 ℃的温度范围内,介电损耗在三种样品中最低,但在0 ℃以下和80 ℃以上时,介电损耗却最高。由此可知,在高介薄型陶瓷芯片电容的生产中,应根据产品的实际使用环境来选择不同的膜系结构制备电极,使高介薄型陶瓷芯片电容在电子系统中使用时有最低的介电损耗[10]。

图5 不同膜系对器件介电损耗的影响Fig.5 Effects of different film structure on dielectric loss of devices

2.2 过渡层厚度对器件性能的影响

选用HT 作为陶瓷介质基片,由于复合膜层(如TaN/TiW、TiW/Ni)不易准确分解各层的厚度,会使测试数据出现错误。因此针对过渡层厚度对器件性能影响的分析,高介薄型陶瓷芯片电容的制备选择温度稳定性较好、制备难度较低的TiW/Au 膜系,通过控制溅射的参数,使过渡层的厚度分别为80,400,600 nm,种子层溅射完成后观察表面覆盖情况,然后进行外金属电极制备和分片切割,最后测量高介薄型陶瓷芯片电容的性能。

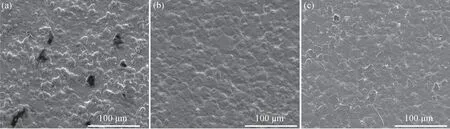

2.2.1 不同过渡层厚度样品表面覆盖情况

在溅射完成后,通过SEM 观察样品表面,不同厚度过渡层对应样品表面的SEM 图如图6。

从图6 (a)可以看出,采用80 nm 厚度过渡层制备的电容样品表面膜层覆盖不完全,表面有明显的陶瓷介质晶粒。当过渡层厚度增加至400 nm 时,电容样品表面覆盖情况有明显改善,TiW 层将陶瓷表面包裹完全,基本看不见裸露在外的陶瓷晶粒,充分阻断了表面金属电极与陶瓷介质的接触。再将缓冲层厚度提高到600 nm 后,电容样品表面包裹覆盖情况进一步提高,已经完全看不到裸露在外的陶瓷晶粒,而且也看不见晶粒的轮廓,整个缓冲层表面平整、光滑且致密。因此从膜层覆盖的情况来看,膜层厚度在400 nm 时已经能比较好地覆盖介质陶瓷,当增加到600 nm 后,表面覆盖更加完整,已基本看不到表面晶粒的轮廓。

图6 不同厚度过渡层对应样品表面的SEM 图。(a) 80 nm 厚度、1000 倍观察;(b) 400 nm 厚度、1000 倍观察;(c) 600 nm 厚度、1000 倍观察Fig.6 The surface SEM of the samples with different thicknesses of transition layer.(a) Thickness 80 nm,1000 times observation;(b) Thickness 400 nm,1000 times observation;(c) Thickness 600 nm,1000 times observation

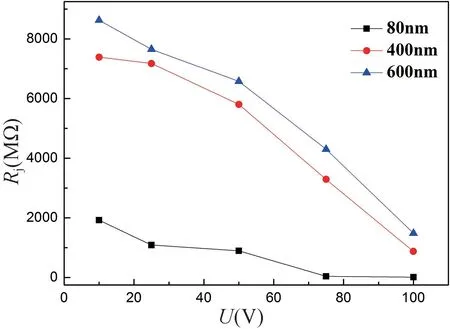

2.2.2 过渡层厚度变化对电容绝缘电阻偏压特性的影响

不同过渡层厚度对电容样品绝缘电阻偏压特性的影响如图7 所示。由图中曲线变化情况可见,当过渡层厚度在80 nm 时,绝缘电阻总体比较低,其原因是在测试电压的作用下,样品表面没有覆盖完全的区域与Au 电极接触,Au 离子在电压作用下可以直接迁移进陶瓷内部,形成漏电流,使测得的绝缘电阻值普遍较低。随着过渡层厚度由80 nm 增加至600 nm,各个电压点的绝缘电阻都呈增大的趋势。当过渡层厚度从80 nm 增加至400 nm 时,高介薄型陶瓷芯片电容的绝缘电阻提升很大,平均每个电压测试点增加了近3000 MΩ。而当过渡层厚度从400 nm 加厚到600 nm 时,绝缘电阻增加值幅度较小。因此,从膜系覆盖性和绝缘电阻偏压特性来看,400 nm 的过渡层已经能获得比较好的综合效果。

图7 厚度变化对绝缘电阻偏压特性的影响Fig.7 Effects of thickness variation on bias voltage characteristics of insulation resistance of devices

2.3 薄型微小器件的精密切割

本文所述的高介薄型陶瓷电容器,采用的介质基片材料质地疏松、脆性强,分片切割时极易出现崩边、卷边、毛刺等问题,有时还会出现“飞晶” 现象。当器件单边尺寸小于1 mm 时,图形效应表现得尤为明显,每20 μm 的卷边或毛刺将使整个电路片的形状发生“扭曲” 而无法满足性能和组装的要求。砂轮切割行业比较成熟,设备的转速、切割速度等工艺参数已有比较可靠的经验可以借鉴,本工作着重从切割的固定方式、刀具选择方面进行优化,通过显微目检的方式对高阶薄型陶瓷芯片电容样品进行检测。

2.3.1 切割刀具对崩边和背金卷边的影响

有关研究指出,砂轮刀具金刚砂颗粒的大小直接影响切削品质。金刚砂颗粒较大的刀具在划切时每次带走的切削粉末较多,切削能力强,但由于撞击严重,容易产生较大的崩裂[11]。所以选择颗粒小的薄型刀具有助于减小介质陶瓷的崩边,本工作分别选用0.25,0.15 mm 的树脂刀(表面有金刚砂颗粒)和0.05 mm 金属刀(表面无金刚砂颗粒),采用相同的切割参数进行切割,获得的效果如表2。

表2 不同刀具切割崩边与卷边情况Tab.2 Cutting edge broken and curling situation of different cutters

从表2 中数据可以看出,薄型金属刀因刀具较薄,表面没有粘附金刚砂颗粒,对样品的撞击比较小,崩边尺寸较小,获得了良好的介质边缘,但同时也可以看出,无论哪种刀具都造成了比较严重的背金卷边。总体来看,0.05 mm 的金属刀具在获得良好的样品边缘的同时,还能保持较小的背金卷边。

2.3.2 切割固定方式对崩边和背金卷边的影响

在工程应用中,为了规避背金卷边带来的困扰,常规的做法是在切割路径上去除金属,制作出切割道,避免金属粘连而发生卷边毛刺,由于高介薄型陶瓷电容器基片晶粒较粗,基片厚度薄,基片整体脆性强,极易出现碎裂,如果采用去除背金制作切割道的方式,需经过一整套图形转移制程,这在工艺过程中会导致片损严重。因此本工作通过解析切割过程中各材质之间的形变关系发现,背金卷边与固定物的硬度相关,其切割过程中的形变如图8 所示。

图8 砂轮切割背金属形变示意Fig.8 Schematic diagram of the deformation of the back metal when the grinding wheel is cut

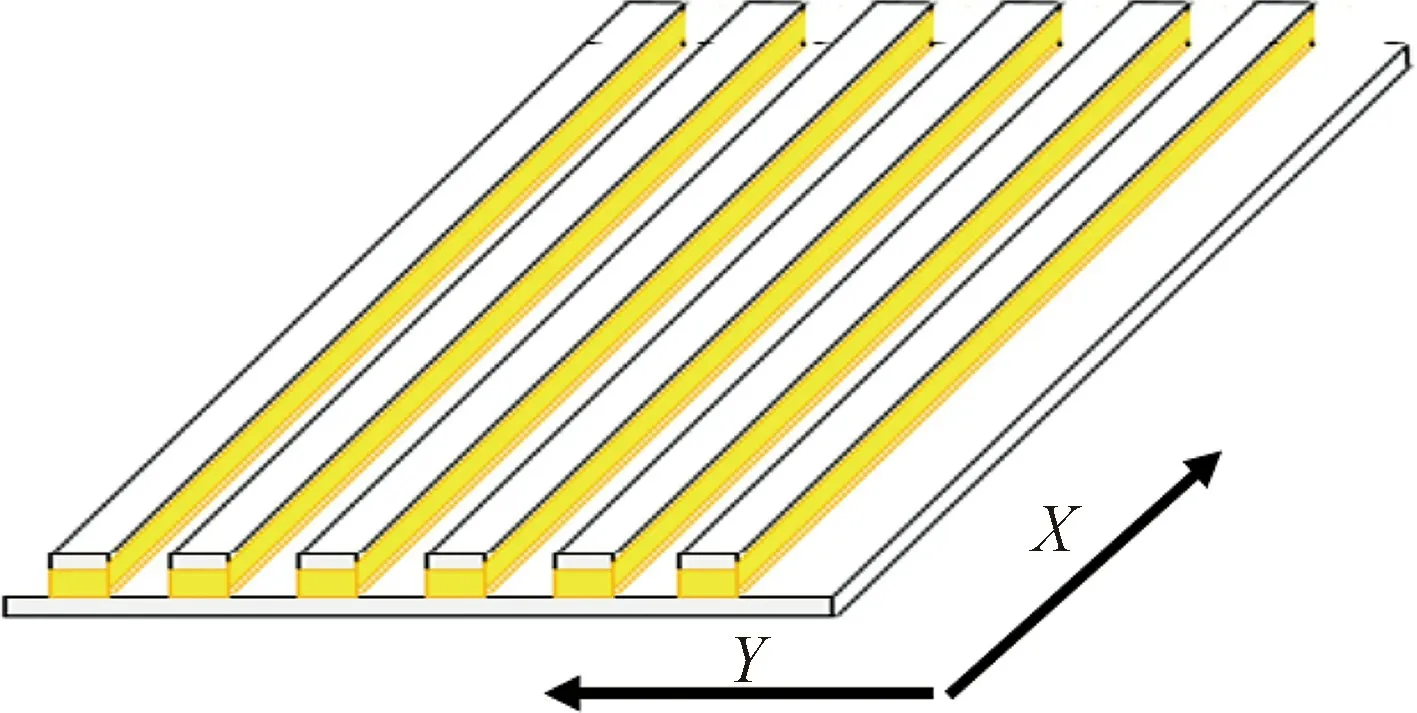

图9 为X、Y方向切割示意图。由图9 可以看出,当固定载体为常规的UV 粘接膜时,由于载体比较软,背金会随载体的形变进行延展而出现毛刺。为此,本工作用硬质材料粘接固定被切样件,有效避免了背金毛刺。另一方面需关注的是分片需从平面的X和Y两个方向进行切割,当完成其中一个方向(如X方向)的切割准备进行第二个方向的切割时,器件的另一个方向(如Y方向)处于悬空状态,正面金属会在平面方向延展形成毛刺。

图9 X、 Y 方向切割示意图Fig.9 Schematic diagram of cutting in X and Y directions

为了有效规避表面金属因平面延展出现的毛刺,本工作采用后填充的方式,在完成X方向的切割后,对切割道进行回填,使在Y方向切割时,表面金属不会出现延展拖边的毛刺。样品实物如图10,经测试,样件崩边小于5 μm,没有明显可见的毛刺,获得了良好的切割效果。

图10 高介薄型陶瓷芯片电容Fig.10 High dielectric thin ceramic capacitors

3 结论

本文系统地研究了金属化工艺对薄型陶瓷芯片电容性能的影响,得到了最佳的膜系结构及过渡层厚度。通过对高介薄型陶瓷芯片电容精密切割工艺的研究,解决了切割时极易出现崩边、卷边、毛刺等问题。

在TiW/Au、TiW/Ni/Au 和TaN/TiW/Au 三种膜系结构中,TaN/TiW/Au 膜系结构能有效地提高高介薄型陶瓷芯片电容的绝缘电阻偏压特性,且在室温附近的介电损耗最小,综合性能最佳,比较适宜用作高介薄型陶瓷芯片电容的电极膜系。

当膜系结构中过渡层的厚度为400 nm 时能很好地覆盖高介薄型陶瓷基片的表面,可有效地隔绝陶瓷层与电极层的接触,提高高介薄型陶瓷芯片电容的绝缘电阻值,降低介电损耗。

针对高介薄型陶瓷芯片电容切割分片,使用薄型切割刀,采用硬质载体固定,切割回填的方法可减少金属平面延展产生的卷边和毛刺。

本工作通过对金属化工艺、膜系结构、过渡层厚度及精细切割的系统研究,为高介薄型陶瓷芯片电容生产提供了工艺基础。