一种NanEyeM 微型高速串行图像传感器解码方法*

何 鑫,景金荣,张会新,刘文怡,熊继军,洪应平

(中北大学仪器科学与动态测试教育部重点实验室,山西 太原 030051)

得益于大规模集成电路技术和精密加工技术的发展,越来越多基于CMOS 工艺的图像传感器诞生[1-2]。近年来,CMOS 图像传感器(CMOS Image Sensor)的大部分性能指标基本超过CCD(Charge Coupled Device,CCD)图像传感器,在医疗、工业、交通及航空等不同领域都得到了广泛的应用[3-6]。

NanEyeM 是艾迈斯半导体公司推出的微型串行CMOS 图像传感器,其面积大小只有1 mm2,通过LVDS(Low-Voltage Differential Signaling)接口可对外提供320×320 像素分辨率的图像,在65 MHz 时钟下最大图像输出帧率为49 FPS,可应用于医疗、科研等对传感器体积大小有严格要求的领域。但其内部未集成ISP(Image Signal Processing,ISP),数据输出为曼彻斯特编码的高速异步串行码流。因此,该传感器的图像数据解码较为困难,且无法直接输出RGB 图像。目前市面上也没有适用于该传感器的接口转换芯片,相关研究较为缺乏,国内只有华中师范大学的石汶奇等人[7]设计过基于FPGA 的NanEye 2D 图像传感器的数据采集IP,但该IP 无法适用于NanEyeM 图像传感器,且只具有数据接收功能,需要配合电脑才能对图像进行转换及显示,具有一定的局限性。

为解决上述技术难题,本文对NanEyeM 图像传感器的异步串行通信、图像数据特点进行了研究分析,提出了一种高速实时图像数据解码方法,设计和实现了基于动态脉宽匹配、边沿跟随的新型数据解码算法,该算法在对数据进行解码的同时可将Bayer图像转换为RGB 图像,实现了串行图像传感器直接输出RGB 图像的功能。并在Xilinx 公司的FPGA平台上进行了测试验证。该算法能够实现图像数据的解码,输出RGB 图像,对于NanEyeM 图像传感器的推广应用具有重要意义。

1 图像传感器工作原理

NanEyeM 图像传感器内部集成10 位分辨率模数转换器(Analog-to-Digital Converter,ADC),可通过2 线LVDS 接口以9 FPS~49 FPS 的帧率串行向外传输320×320 pixel 分辨率的图像数据。

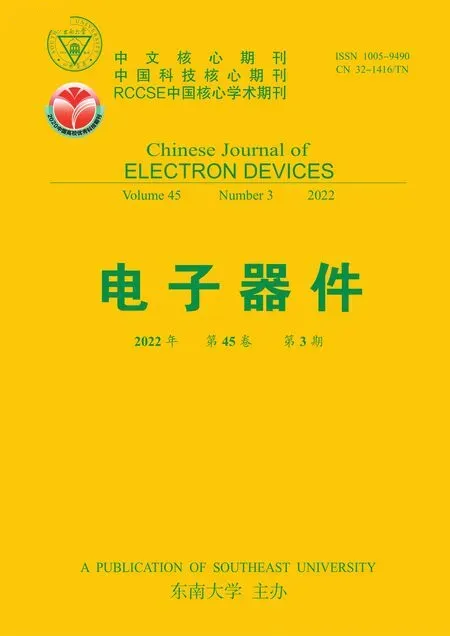

如图1 所示,该传感器共有四种工作模式,分别为配置模式、同步模式、延迟模式以及输出模式。初始上电时,传感器在时长为648 PP(1PP 为12 bit数据时长)的配置模式中循环,在该模式下控制端可通过LVDS 接口对传感器进行参数上的配置,通过对配置寄存器的空闲模式位写“1”可退出配置模式,进入四种模式的循环中。在同步模式和延迟模式下,传感器将持续输出同步字,数据接收端可从同步字中提取数据编码时钟信息,用于数据的解码以及采样。经过648 PP 的同步阶段以及2×328 PP 至498×328 PP 的延迟阶段后,传感器进入到输出模式,在该模式下串行输出320×320 pixel 分辨率图像数据,在每一帧图像数据尾部都附加有长度为7 PP的帧结束标志,用于检查图像数据传输的正确性。

图1 图像传感器工作模式转换图

该图像传感器使用异步串行方式进行数据传输,每个像素数据由12 bit 组成,其中有效数据位占据中间10 bit,高位在前,数据传输起始以电平“1”表示,传输结束以电平“0”表示。图像数据格式如图2 所示。

图2 图像数据格式

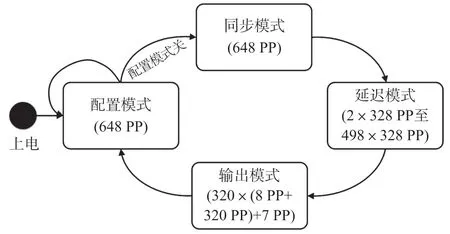

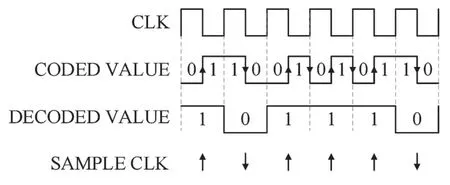

如图3 所示,图像传感器使用曼彻斯特编码方式对图像数据进行编码,即将数据与内部编码时钟进行异或操作,使用上升沿(“01”)表示数据“1”,下降沿(“10”)表示数据“0”[8]。例如原始数据“101110110010”,经曼彻斯特编码后则变为“011001010110010110100110”。

图3 曼彻斯特编码

NanEyeM 图像传感器内部未集成ISP 单元,其输出的是Bayer 格式的RAW 图像,需要进行图像格式转换,将Bayer 格式转为RGB 格式。

2 解码原理

2.1 串行数据解码原理

对曼彻斯特编码后的数据进行分析,编码后的串行数据可以分为两种电平数据,如图4 所示。一种为L_BIT(长周期高(低)电平),其电平维持时间为一个编码时钟周期;另一种为S_BIT(短周期高(低)电平),其电平维持时间为半个编码时钟周期。

图4 两种曼彻斯特电平码流

为了对图像传感器输出的曼彻斯特编码数据进行解码,需要对数据电平脉宽进行持续测量,并与编码时钟周期进行比较。L_BIT 表示原始数据电平值发生变化,S_BIT 表示原始数据电平值未发生变化。NanEyeM 图像传感器在每次数据传输前都会进入时长为648 PP 的配置模式,此时传感器的数据线维持低电平状态,即信号的初始电平已知,对数据的跳变沿进行跟随同时判断电平脉宽即可还原原始数据。

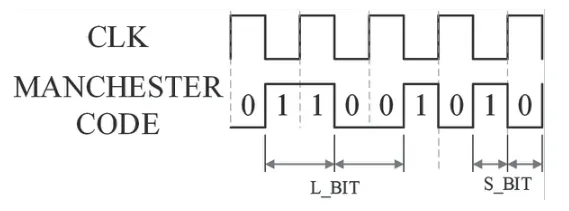

通过上述分析可知,对数据进行正确解码的前提是对原始编码时钟周期进行正确测量。在同步模式下和延迟模式下,NanEyeM 图像传感器会持续输出同步字,其格式如图5 所示。

图5 同步字格式

由曼彻斯特编码特点可知,数据“0”被编码为下降沿“10”,因此同步字在经曼彻斯特编码后波形与编码时钟保持一致,如图6 所示。此时的数据可认为是数据编码时钟,测量同步字的周期即可以得到数据编码时钟的周期。

图6 同步字编码后波形

2.2 串行数据采样信号提取原理

在一般的低速异步串行通信中,由于其速度较低,采样容差区间大,可由接收端按通信波特率生成采样信号对数据进行采样还原[9]。然而NanEyeM图像传感器的数据输出速率高达几MHz 至几十MHz,若直接由接收端生成采样信号,则对系统运行频率要求较高,实现难度大。另外虽然可以从曼彻斯特数据流中恢复出时钟信息,但由于传感器内部存在的时钟抖动、线路传输时延、数据耦合干扰以及系统运行频率受限等问题,由接收端恢复出的原始时钟始终与传感器内部的时钟存在周期误差及相位误差,且误差会随时间累积。误差的存在将导致数据解码错误,所以由接收端恢复的时钟不能用做数据采样信号。

如图7 所示,曼彻斯特编码后数据总是在原始数据的中间时刻发生电平跳变。而在串行通信中,为了确保采样电平数据的正确性、可靠性,往往在数据位时间的中间时刻对信号进行采样。因此,编码数据的跳变沿可作为解码数据的采样信号。另外,由曼彻斯特编码特点可知,电平“1”被编码成下降沿,电平“0”被编码成上升沿,则当解码数据为电平“1”时,使用编码数据下降沿采样,当解码数据为电平“0”时,使用编码数据上升沿采样。

图7 数据采样信号提取

2.3 图像转换原理

NanEyeM 在黑白图像传感器的基础上增加了色彩滤波阵列(CFA),从而使传感器可以输出Bayer格式的彩色图像[10]。该传感器内部使用的色彩滤波阵列如图8 所示,左下角为第一个输出像素。

图8 传感器内部色彩滤波阵列

Bayer 格式图像特点为每个像素点只含有RGB颜色空间中的一种分量,需要使用插值算法对像素点插值处理,补全缺失的另外两种颜色分量,将Bayer 格式转换为RGB 格式[11]。

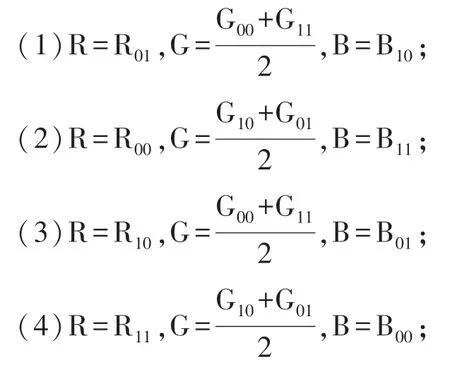

对Bayer 格式图像数据进行分析,可以发现,在对像素进行插值处理时,共有四种可能的情况,如图9 所示[12]。

图9 插值时四种情况

基于硬件可行性考虑,在设计中采用线性插值方式完成图像格式转换[13]。在图9 的每一种情况中,4 个像素点构成一个2×2 像素矩阵,以矩阵左下角第一个像素为零点,向右、向上像素坐标递增,则有Bayer 转RGB 公式:

式中:R、G、B 分别表示RGB 颜色空间中的三种颜色分量。

3 图像传感器解码算法硬件设计

NanEyeM 图像传感器图像解码算法使用Verilog硬件描述语言实现,采用自顶向下的设计方法[14]。算法由SerialSync(串行同步模块)、ClkExtract(时钟提取模块)、SensorDataDecoder(传感器数据解码模块)、Bayer2RGB(Bayer 转RGB 模块)共4 个模块组成。每个模块实现算法的特定功能,算法整体框架如图10 所示。

图10 算法整体框图

3.1 数据同步模块硬件设计

由于NanEyeM 图像传感器与FPGA 是两个完全独立的设备,其各自内部工作时钟在频率、相位上都是异步的。当异步信号直接输入FPGA 内部寄存器时,极大可能引起寄存器亚稳态问题,导致数据错误[15]。因此,使用数据同步模块将传感器输入的异步信号进行同步处理,最大限度降低寄存器出现亚稳态的可能性,保证数据的可靠性。同步模块采用双锁存器法实现,硬件原理如图11 所示。两个级联锁存器对输入信号连续锁存两次,研究表明该设计可以将亚稳态出现的机率降低到一个极小的程度[16]。

图11 双锁存器同步原理图

3.2 编码时钟周期提取模块硬件设计

编码时钟周期信息提取模块主要为移位寄存器、边沿检测模块及周期计数器组成。在配置模式下,传感器保持低电平输出,完成对传感器的配置并退出配置模式后,同步模式开始。在检测到第一个同步字的上升沿后,周期计数器在本地时钟信号的控制下开始计数,记为Tperiod_cnt,同时另一计数器开始统计数据的上升沿个数,记为Tpdg_cnt。当Tpdg_cnt=1 024,即统计了1 024 个编码时钟周期后,计数器停止计数,取周期计数器的平均值Tperiod_cnt/1 024 作为编码时钟周期,设计中使用取计数器值高位(Tperiod_cnt[23:11])的方式完成该计算。

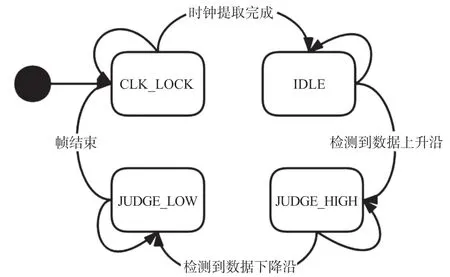

3.3 数据解码模块硬件设计

数据的解码首先需要对传感器输出的曼彻斯特编码的数据流进行还原,之后在采样信号的驱动下将串行数据转为并行数据。解码时使用有限状态机对码流跳变沿进行跟随,状态机状态定义及转换条件如图12 所示。系统初始状态为CLK_LOCK 状态,当时钟提取模块完成对时钟信息的提取后,跳转到IDLE 状态。检测到数据的上升沿后,跳转到JUDGE_HIGH 状态,对数据的高电平脉宽进行判断,解码出原始数据。若此时检测到数据下降沿,则跳转到JUDGE_LOW 状态,对输入数据的低电平时长进行判断,解码出原始数据。同时若连续10 次采样输入数据都为低电平,则可以判断本次数据帧传输完成,重新回到CLK_LOCK 状态。

图12 解码状态机

另外,为了解决传感器内部存在的时钟抖动、数据传输时延、信号耦合干扰等问题所带来的数据脉宽变化问题,设计引入了动态脉宽调节算法,每次接收数据之前都利用传感器的同步字对解码的脉宽阈值进行重新标定,以保证数据解码的正确性。

串行数据转并行数据的功能使用12 bit 的移位寄存器(RecvShiftReg)和位接收计数器(RecvBitCnt)实现。由传感器输出的数据格式可知,当检测到第一个高电平时,数据传输开始,移位寄存器开始在数据采样时钟(SampleClk)的驱动下对解码后的数据进行移位采样,同时位接收计数器(RecvBitCnt)开始统计接收到的数据位数。

如图13 所示,当移位寄存器的值与数据匹配模版“1XXXXXXXXXX0”匹配,且位接收计数器的位为12 时,提取出中间的10 位有效数据,同时数据有效信号(RawDataValid)置高一个时钟周期,清零位接收计数器,为接收下一个数据作准备。若移位寄存器中的值全为0,说明一行图像数据传输完成,复位所有寄存器,保证下一次的数据能被正确接收。

图13 数据提取原理

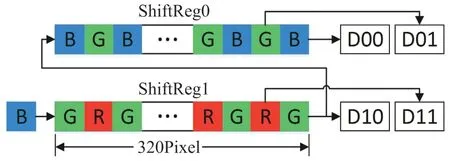

3.4 Bayer 转RGB 模块硬件设计

本设计中使用行列计数器PixelX、PixelY 分别对接收图像数据的行像素及列像素进行计数。NanEyeM 图像传感器的有效像素大小为320×320 pixel,因此,行计数器PixelX 在每320 个像素后清零,同时列计数器PixelY 加一。

如图14 所示,使用两个长度为320 pixel、位宽为10B 的线性移位寄存器缓存两行图像数据,实现线性插值算法。线性移位寄存器在数据有效信号(Raw-DataValid)的驱动下从尾部移入新数据,从头部移出旧数据。另外使用两个独立寄存器D00、D10 分别存储从两个线性移位寄存器移出的像素值,与两个线性移位寄存器的头部值D01、D11 组成2×2 大小的像素矩阵。最后由{PixelX[0],PixelY[0]}的值对比图9即确定当前状态,再依据Bayer 转RGB 公式完成图像格式转换功能。

图14 移位寄存器连接方式

在进行图像格式转换的同时,该模块也通过行列计数器PixelX、PixelY 的值在正确的时刻输出图像行同步和场同步信号,用于后续图像输出显示。

4 算法仿真与实验结果

4.1 算法仿真分析

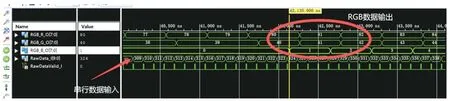

本算法使用Verilog 语言编写,并基于Xilix 公司的Spartan-6 系列FPGA 平台上实现,使用ISE14.7 内部自带的仿真软件ISim 进行算法的时序仿真,结果如图15、图16 所示。

图15 数据解码模块仿真图

图16 Bayer 转RGB 模块仿真图

由仿真图可以看出,数据解码模块和Bayer 转RGB 模块都能正确连续地输出结果,且各模块输出值与理论值相符,达到了本文设计目标。

4.2 实验结果

使用图像传感器对不同物体进行拍摄,经过算法解码后的图像为标准的RGB 视频流,可直接使用驱动模块将图像输出到显示器上显示,并使用截屏软件进行截屏。图17(a)为NanEeyM 图像传感器实物,图17(b)为手部皮肤纹理,图17(c)为拍摄订书针包装盒。从截取的图像中可以看出,该算法能正确地接收并解码传感器图像数据,且解码转换后的图像纹理清晰,色彩还原度较高,也能正确流畅地输出RGB 图像。

图17 NanEyeM 图像传感器外形图及其拍摄的图像

5 结论

本文提出了一种NanEyeM 微型图像传感器的数据解码转换算法,并基于Xilinx 公司的Spartan-6系列FPGA 在硬件上实现了该算法。测试结果证明,当传感器工作在高速模式下,以24 frame/s 的帧速率输出图像数据时,算法能够正确、连续地对数据进行解码并输出RGB 图像。结果表明,本算法很好地解决了NanEyeM 微型图像传感器高速异步串行数据的解码难问题及无内置ISP 导致的无法直接输出RGB 图像问题,为后续开发基于该图像传感器的应用奠定了重要基础。