一种改进型高速1553B 总线发送器斜率控制电路

刘士全,唐海洋,顾林

(中科芯集成电路有限公司,江苏 无锡 214072)

0 引言

MIL-STD-1553 数据总线因其高可靠性等诸多优点被广泛应用于武器装备,实现传感器、各个分系统的信息共享与传输[1-2]。但随着软件技术的革新和更快处理器的诞生,传统1553B 仅仅1 Mb/s 的数据传输速度已无法满足现代武器装备研发的需求[3],这也就催生了很多更高更快的通信方式,如时间触发网络(TTE)和FC-AE-1553。

近年来,时间触发网络的提出,在传统以太网的基础上增加了时间同步机制和流量调度算法,具有低误码率、低延时、高带宽、高速率等优势,能够适用于未来航天技术的需求[4-5],但时间触发网络还处在协议完善阶段,离投入实际应用还需要时间;FC-AE-1553 在光纤传输的基础上定义了对MIL-STD-1553 的上层协议映射,使其达到高速率的同时兼顾稳定性[6],但FC-AE-1553需要改变其物理层,不同形式的信道,其组网方式和连接介质均需重新选择和改变,这也就导致了研发成本的上升[7]。

因此,高速1553B 通信的设计是一个行之有效的方式,在提升通信速率的同时,保留了组网方式、连接介质的一致性,降低了武器装置研发的成本[8]。业内对高速1553B 总线的研究也日趋增多,文献[9]介绍了2 Mb/s 速率1553B 总线仿真卡的软硬件设计与实现;文献[10]提供了一种4 Mb/s 速率1553B 总线测试平台的实现方法,该测试平台能够支持4 Mb/s 速率1553B 的电气特性参数和总线协议功能测试。

本文设计了一种新型的收发器斜率控制电路,并应用于高速1553B 总线发送器芯片,提升了发送器的速率,改善了总线波形质量,并与1 Mb/s 收发器完全兼容,其通信介质、变压器、耦合器等组网设备完全保持一致,极大程度降低了装备升级的成本。测试表明,设计的总线收发器通信速率满足4 Mb/s 的性能要求,斜率控制电路有效保证了发送器性能。

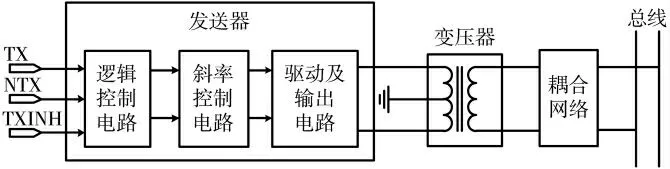

1 发送器功能与架构

如图1 所示,电压型1553B 发送器主要由逻辑控制电路、斜率控制电路、驱动及输出电路组成[11]。逻辑控制电路的作用是识别使能信号,当TXINH 使能信号为低时,发送器使能有效;TXINH 为高时,发送器处于关闭状态;保证输入信号TX、NTX 为一对曼彻斯特Ⅱ编码互补信号,如出现同时为高电平或低电平时,关断电路。输出及驱动电路将曼彻斯特Ⅱ编码信号转化为BUS 端总线符合1553B 信号特征的信号输出,驱动变压器,增强带载能力。斜率控制电路的作用是调节输出信号的上升时间、下降时间、总线幅值参数。

图1 发送器电路原理图

分析发送器的电路组成可知,发送器的逻辑控制电路由于都是由数字电路组成,不存在速率限制的瓶颈,其斜率控制电路因其负责总线信号关键参数的调节,在实现1553B 发送速度提升中起到关键的作用。

2 斜率控制电路

2.1 一种典型的斜率控制电路

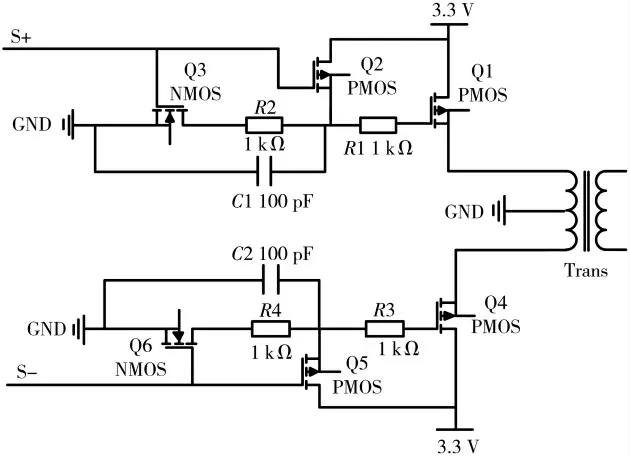

上升时间、下降时间、总线幅值是1553B 通信规范的重要参数[12]。斜率控制电路通过调节主回路PMOS 管驱动信号的上升时间和下降时间,并提供对主回路PMOS管的驱动能力,从而调节发送器总线输出信号的上升时间和下降时间,驱动能力越强,总线输出幅值越高。

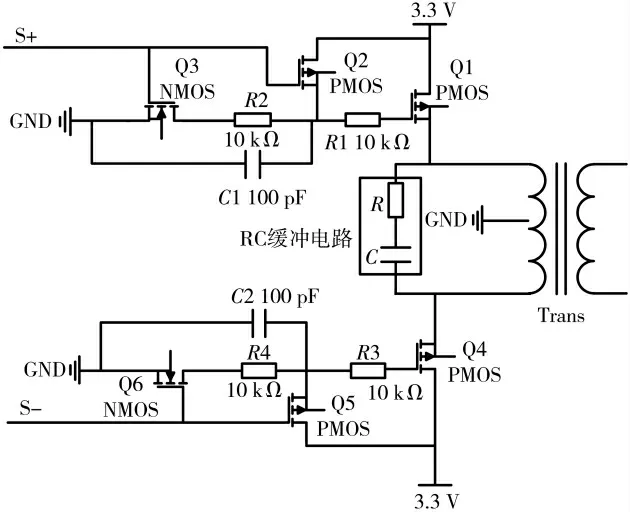

图2 所示为某型号的1553B 发送器的斜率控制电路,其工作原理是,输入控制信号S+、S-为曼切斯特Ⅱ编码互补信号,当输入控制信号S+为高电平时,下级NMOS管Q3 导通,上级PMOS 管Q2 截止,此时主回路PMOS管Q1 导通,电流为后级的变压器充电,从而在1553B 总线上输出信号;当输入控制信号S+为低电平时,下级NMOS管Q3 截止,上级PMOS 管Q2 导通,此时主回路PMOS管Q1 截止,关断输出。驱动信号的上升下降时间由两部分电路调节,分别是电阻R1、R2 的值和电容C1,电阻R1、R2 电阻值调节驱动电路的电流,决定主回路PMOS 管Q1 的开启关闭速度,电容C1 调节驱动信号的上升下降时间。同理,S-的作用机理与S+一致。

图2 典型的斜率控制电路原理图

该型斜率控制电路应用在1 Mb/s 标准速率下,能取得比较好的效果。但将其速度提高到4 Mb/s 及以上速度时,就会出现如下问题,如图3 所示。

图3 典型斜率控制电路仿真波形图

(1)驱动信号:低电平不到0 V,且具有很大的杂波,导致驱动能力不足;

(2)总线上波形幅值偏低,幅值为2 V,离1553B 规范要求6 V~9 V 有较大差距,且具有很大的杂波。

分析原因如下,驱动信号驱动能力不足主要原因是电阻R1、R2(也包括电阻R3、R4)的阻值过大。考虑到后端连接的是变压器负载,工作在高频高速率的工况下,变压器的电感储存能量,在主回路的PMOS 管Q1(也包括Q4,下文表述Q1、Q4 的原理一致)开启关断时刻得不到有效释放,引起变压器次级线圈输出信号形成振荡,所以体现为杂波,振动消耗了能量,体现为总线上幅值偏低,并引起上升时间和下降时间偏慢。

2.2 改进型斜率控制电路

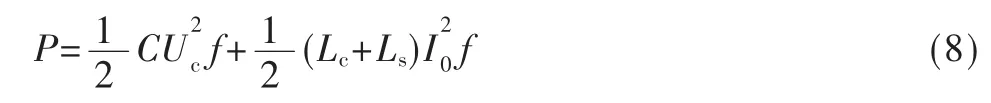

本文提出一种改进型斜率控制电路,如图4 所示。在图2 的基础上,减少了主回路PMOS 管Q1 栅极驱动回路R1、R2 电阻值,增强其驱动能力,有利于提升上升时间和下降时间,更适应高频高速率的工作场景。同时,在变压器的初级并联了RC 缓冲电路,在主回路PMOS管导通与关断的瞬间,及时地将电感线圈中的储存电能释放掉。采用本文设计的斜率控制电路构建发送器,可沿用1 Mb/s 接收器,其通信介质、耦合器均无需改变,保持与1 Mb/s 1553B 的兼容性。

图4 改进型斜率控制电路原理图

RC 缓冲电路的工作原理如下:在主回路PMOS 管Q1关断的瞬间,变压器绕组等效成一个电感,电感阻止电流发生突变,并产生感应电压,与直流电源电压Uc串联一起加在PMOS 管Q1 两端,此时,Q1 两端的尖峰电压Us为:

式中:Us为PMOS 管Q1 两端的尖峰电压;Uc为直流电源电压;Lc为变压器等效电感,Ls为电路杂散电感,di/dt为Q1 管源极和漏极电流变化速率。

RC 缓冲电路的作用是吸收Q1 管关断时产生的过电压,其本质是靠吸收电容C 来吸收掉变压器等效电感和杂散电感产生的能量,即能量的转移,因此确定吸收电容C 的容值大小[13]。电路中存储在总电感中的能量为:

吸收电容上需要吸收的能量为:

△U 为总电感产生的过电压,即△U=Um-Uc,其中,Um可通过示波器测试电感得到,Uc为直流电压。

假设关断前存储电感中的磁能在Q1 关断时完全转化为C 中电能。因此就有:

从而求得吸收电容的容值为:

因为吸收电容C 在Q1 管导通时存储的能量为:

其中f 为电路的开关频率。

存储在总电感上的能量为:

式中,I0为Q1 管的关断电流。

因此,消耗在吸收电阻R 上的功率P 为:

因为RC 缓冲电路是随着Q1 管的开关而循环工作的,因此在Q1 管导通期间,存储在吸收电容C 中的能量必须通过电阻R 消耗掉,只要满足τ=RC 小于1/4 的Q1管导通时间,就可以保证电容C 中绝大部分能量的释放,不会影响下一次吸收[14],因此吸收电阻可以通过下式来确定:

式中,τ0为Q1 管的导通时间。

但是R 也不是越低越好的,因为吸收电路中存大电流振荡,Q1 管导通时的电流峰值也会相应增加[15],因此在满足上式的情况下尽量使R 设得高一点,具体可参考式(10):

综上所述吸收电阻R 为:

根据图中器件所给出的参数按照式(5)和式(11)可得出吸出电阻大约为20 Ω,吸收电容大约为12 nF。

2.3 电路仿真与分析

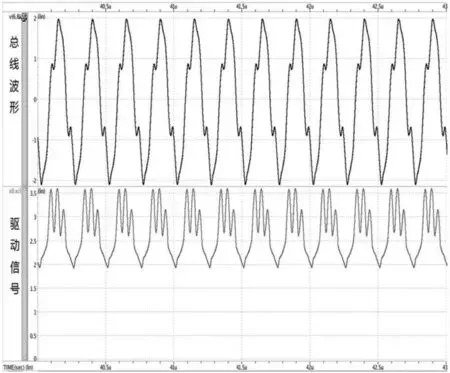

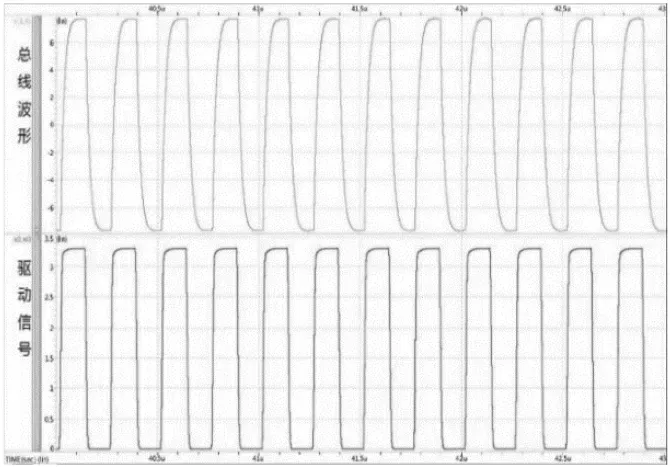

使用电路仿真工具,对改进型斜率控制电路进行仿真,得到总线波形和PMOS 管Q1 栅极驱动信号的仿真波形如图5 所示。

图5 改进型斜率控制电路仿真波形图

对比图3 和图5 可以看出:

(1)驱动信号:典型斜率控制电路在4 Mb/s 速率下,驱动信号低电平为2 V,体现对主回路PMOS 管的驱动能力不足,导致总线波形幅值不够,因为驱动信号具有很大的杂波,导致总线信号毛刺太大。图5 显示驱动信号波形平滑且低电平可以达到0 V,对于主回路的PMOS管驱动能力有了较大提高。

(2)总线波形:典型斜率控制电路总线输出幅值为2 V,改进型斜率控制电路输出波形幅值为7 V,且波形平滑无毛刺,说明RC 缓冲电路的引入,对总线波形的改善效果明显。

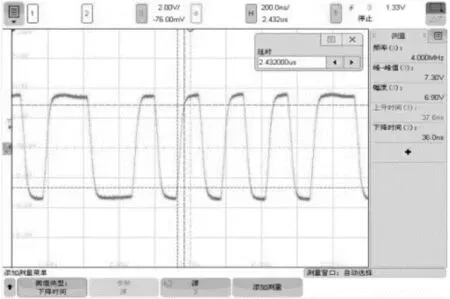

3 收发器性能测试

使用0.5 μm COMS 工艺流片,封装后按照1553B 规范对其进行测试。4 Mb/s 速率下总线波形如图6 所示。从图6 可以看出,在4 Mb/s 速率下,总线波形平滑无毛刺,跟仿真结果一致,说明改进型斜率控制电路,特别是RC 缓冲电路取得了较好效果。表1 列举了该发送器在4 Mb/s 速率下其主要电参数的值,各项指标符合规范要求。

图6 总线波形图

表1 发送器主要电参数表

4 结论

本文设计了一种新型的收发器斜率控制电路,并应用于高速1553B 总线发送器芯片,提升了发送器的速率,改善了总线波形质量,并与1 Mb/s 收发器完全兼容,其通信介质、变压器、耦合器等组网设备完全保持一致,极大程度降低了装备升级的成本。测试表明,设计的总线收发器通信速率满足4 Mb/s 的性能要求,斜率控制电路有效保证了收发器性能。