基于多核TMS320C6678 的数据处理与存储系统设计

周加谊,李 中,杨 波

(中国兵器装备集团自动化研究所有限公司特种计算机事业部,四川绵阳 621000)

数字信号处理在很多领域得到了广泛应用,逐步形成了一门独立的学科体系[1]。由德州仪器公司研发的TMS320C6678 数字信号处理器(DSP),可实现八核极高性能功耗比,适用于医疗、电信、军事以及工业领域的各种应用。TMS320C6678 是KeyStone架构的8 核DSP 处理器,提供了强大的定点和浮点运算能力,同时芯片内部集成了SRIO、千兆以太网等外设[2]。在众多科学大数据计算应用中,I/O 性能已逐渐成为制约应用程序性能的主要瓶颈[3]。在实际工程应用中,DSP 较多应用于CPU 密集型程序处理,对于I/O 型程序处理并不擅长。其中,算法运算程序属于典型的CPU 密集型程序,硬盘存储程序属于典型的I/O 型程序。在嵌入式领域,当需求既存在算法处理程序,又存在硬盘存储程序时,设计者通常会将算法处理部分放在DSP上完成,而硬盘存储部分交由额外的硬件设备完成,如交由搭载Linux 系统的ARM 设备完成,但这样的设计需要额外的硬件开销,不利于成本控制。该文将介绍一种基于TMS320C6678数字信号处理器,利用多核协同处理方式,实现数据算法处理与数据存储功能。

1 系统概述

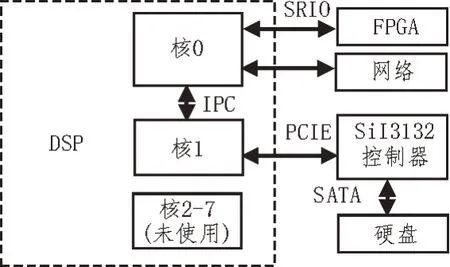

系统使用TMS320C6678 数字信号处理器作为主处理器,该处理器拥有8 个处理核心单元,单核主频为1 GHz,用于完成数据算法处理、外围接口控制及数据存储等功能[4-5]。使用Xilinx 公司的现场可编程门阵列(FPGA)Kintex-7 作为信号处理器,用于完成外部原始数据采集。DSP和FPGA之间使用高速通信接口SRIO(Serial RapidIO)实现数据传输,SRIO 是面向嵌入式系统开发的高可靠、高性能新一代互联技术[6-7]。SRIO 链接宽度配置为4x,传输速率配置为3.125 Gbps。硬盘通常使用SATA接口,TMS320C6678数字信号处理器不提供SATA 接口,但拥有PCIExpress 接口,因此文中采用一个PCI-Express 转SATA 控制器,型号为SiI3132。SiI3132 控制器一端连接DSP 的PCI-Express 接口,另一端连接硬盘的SATA 接口,实现DSP 控制硬盘功能,达到数据存储的目的。DSP 核0 完成与FPGA 和网络之间的数据通信功能,DSP 核1 完成数据存储功能,系统框图如图1 所示。

图1 系统框图

操作系统选用TI 公司的可扩展实时操作系统SYS/BIOS,该系统具有抢占式、多线程、实时调度、内存管理等功能特点,并提供多核通信开发包。结合SYS/BIOS 操作系统提供的信号处理函数库,能够十分方便、快捷地开发出实时应用软件,大幅减小了软件开发难度,提升了软件开发效率[8-9]。

2 数据处理及存储设计

2.1 数据处理

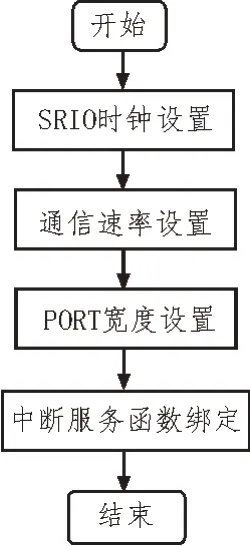

外部数据由FPGA 采集,FPGA 通过高速通信接口SRIO 传输至DSP。在系统上电后,DSP 完成SRIO接口初始化功能,SRIO 接口初始化工作包括:SRIO时钟设置、通信速率设置、PORT 宽度设置和中断服务函数绑定。SRIO 初始化流程如图2 所示。

图2 SRIO初始化流程

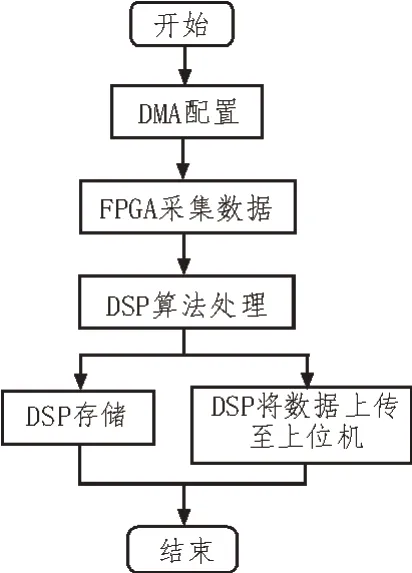

系统初始化完成后,DSP 软件向FPGA 发送DMA配置命令,包括DMA 地址和DMA 大小等信息,DMA地址可使用DDR3 地址,也可使用DSP 处理器的片上内存MSMCSRAM 地址。在完成DMA 配置之后,DSP 向FPGA 发送开始采集命令,FPGA 进入数据采集模式。外部数据到来时,FPGA 通过SRIO 接口以DMA 方式将数据写入DDR3,同时产生中断信号告知DSP 有数据到来。为提升中断服务函数的处理效率,中断服务函数直接将数据从DDR3 中取出放入FIFO 中,而不作任何处理,数据处理功能由数据处理模块完成。

数据处理模块以任务方式运行,数据处理任务实时查询FIFO 状态,当FIFO 不为空时,取出FIFO 数据,完成算法处理。经算法处理后的数据分两路处理,一路直接存储,一路通过网络方式发送至上位机。数据处理流程如图3 所示。

图3 数据处理流程图

2.2 数据存储

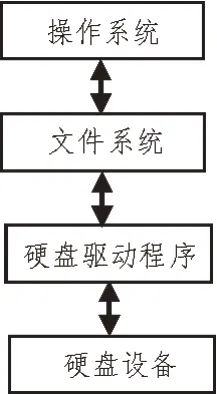

一个健全的储存系统包含文件系统和硬盘驱动程序,存储系统框图如图4所示。TI公司的SYS/BIOS操作系统虽然包含文件系统,但都是基于Nand-flash存储器。考虑到Nand-flash存在坏块管理、容量、性能等问题,该方案采用SATA 固态硬盘替代Nand-flash作为存储介质。SATA固态硬盘与DSP之间使用PCIE转SATA 控制器互联,实现硬盘控制功能。使用硬盘方案需要移植硬盘驱动程序和文件系统。

图4 储存系统框图

TI 公司所提供的软件开发套件不包含硬盘驱动程序,硬盘控制部分属于难点。硬盘驱动程序可参照VxWorks 系统和Linux 系统的硬盘驱动进行移植,最后将硬盘驱动的读写接口封装成文件系统一致的读写接口。

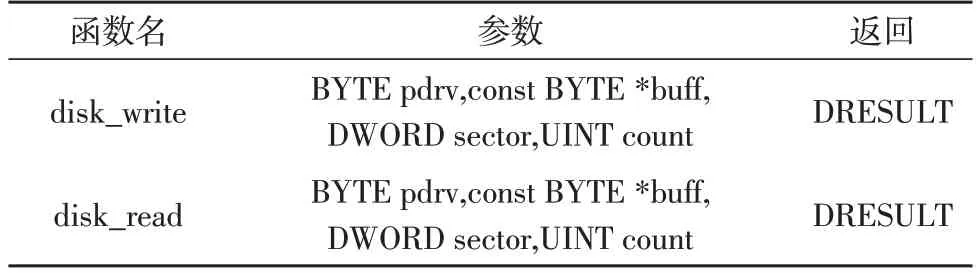

在文件系统上,使用开源操作文件系统模块FatFs。FatFs 是一款完全免费开源的FAT 文件系统模块,专门为小型的嵌入式系统而设计,它完全使用标准的C语言编写,因此,具有良好的跨平台特性,可以非常方便地移植到8051、PIC、AVR、SH、Z80、ARM、DSP 等嵌入式处理器上,移植工作量较小[10-12]。FatFs不仅提供文件夹及文件创建、删除、修改和查找等基本功能,还提供容量查询及格式化功能。在移植FatFs文件系统时,需完成disk_read 函数和disk_write 函数的实现。其中,disk_read函数有4个参数分别如下:pdrv表示驱动器号,对应某一硬盘设备;buff 为读取数据的缓存区指针;sector为需要读取的扇区号;count为读取扇区的个数。在移植文件系统时,还需要适配文件系统与硬盘驱动程序的读写接口。FatFs文件系统的读、写函数原型如表1所示,可以看出,disk_write函数与disk_read函数的参数类型和返回值基本一致。在具体代码实现中,将硬盘驱动程序的读函数封装成disk_read 函数,将硬盘驱动程序的写函数封装成disk_write 函数,这样就实现了文件系统与驱动程序之间的对接。

表1 文件系统读写函数原型

3 多核通信设计

该系统主要包括数据处理和数据存储两大功能模块,其中,数据处理功能主要消耗处理器资源,而存储功能大部分时间花费在外设硬盘的I/O 操作上。结合DSP 的特性和实际应用需求,为充分发挥DSP 拥有多核心的优势,软件设计上将使用两个处理器核心,分别用于数据处理和数据存储,达到资源最大利用率和性能最优的设计目的。

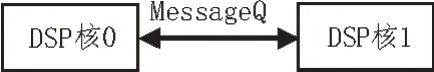

TI公司提供了多核软件开发包MCSDK(Multiple CoreSoftware Development Kit),具体内容涵盖对各种可用软件套件以及实用程序及工具链的概述,可为编程人员开发实时操作系统SYS/BIOS助一臂之力[13-14]。MCSDK 主包括实时操作系统SYS/BIOS、芯片支持开发包、处理器核间通信IPC 开发包、网络协议栈、算法库及调试工具等组件。该系统主要使用IPC 开发包,实现处理器核间的数据传输和消息同步。IPC开发包提供了MessageQ 和Notify 两种核间通信方式[15-16]。MessageQ 方式支持可变数据传输,而Notify 不支持携带数据通信。系统在完成数据采集和处理后,需要将处理后的数据由一个核传输至另外一个核,因此选择MessageQ 方式进行多核通信。核间通信模型如图5 所示。

图5 核间通信模型

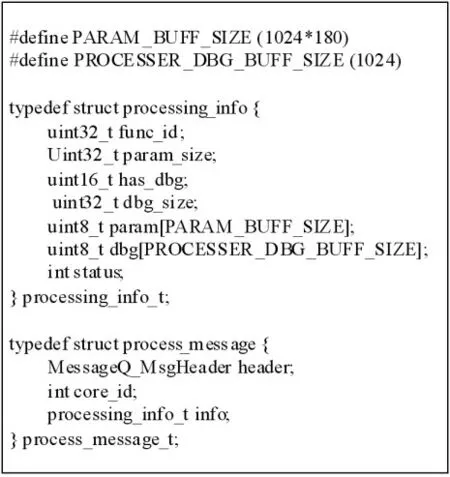

MessageQ 方式支持自定义数据结构完成多核通信,多核通信数据结构如图6 所示。在process_mes sage_t 结构体中,header 和coreid 两个数据成员为多核通信约束结构体头信息,一般情况下不作改动,info 成员为软件开发者自定义数据结构,其定义见processing_info_t 结构体。在processing_info_t 结构体中,func_id 字段表示此次通信的功能号,如当func_id=0,则表示此次传输的信息为第0 通道采集的数据;param 字段表示此次通信携带的数据,最大支持180 kB;param_size 表示携带数据的长度;dbg 字段存储调试信息;dbg_size 表示调试信息长度;has_dbg表示调试信息是否有效。DSP 主核使用Message Q_put 函数发送process_message_t 结构体,从核调用MessageQ_get 函数接收该结构体[17-18],从核读取结构体中的func_id,由此判断此次请求的具体功能,随后执行相应功能代码。

图6 多核通信数据结构

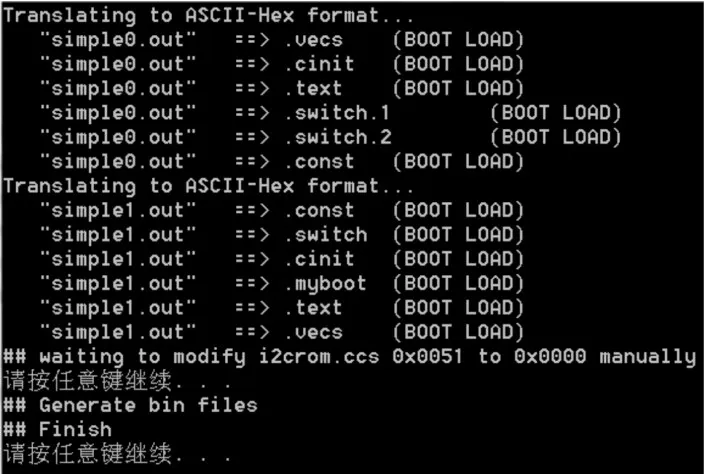

在该系统中,使用DSP 的两个处理器核心分别完成数据采集处理和存储功能。其中,核0 设计为主核,完成数据采集和处理功能,核1 设计为从核,完成数据存储功能。为方便代码管理,为两个DSP 核独立创建应用工程,最终使用多核合成工具将两个工程编译出的out 文件转换为一个bin 文件,多核合成界面如图7 所示。

图7 多核合成界面

数据采集开始命令和结束命令由上位机通过网络接口向DSP 核0 下发,当核0 收到开始采集命令后,核0 向FPGA 发送开始采集指令,同时向核1 通过MessageQ 方式发送文件创建命令。FPGA 收到开始采集命令后,以DMA 方式将数据传输至DDR 内存,并以中断方式通知核0。核0 在中断服务程序中取出数据后存放至FIFO,随后数据处理任务会取出数据,进行算法处理,并将处理后的数据发送至核1。核1 将数据进行存储,直到上位机发送停止命令时,FPGA将停止采集,此时核0告知核1关闭文件并停止存储。若数据存储过程中未收到上位机停止命令,且存储文件大于等于4 GB,核1 将自动关闭文件并重新创建文件继续存储,直到硬盘存满,终止存储。

4 性能验证

为对比单核处理与多核处理之间的性能差异,按该文所述的多核软件架构编译出的软件命名为APP_A.bin。与此同时,将所有软件功能都集成在单核上面,编译出的软件命名为APP_B.bin。分别在目标板卡上运行APP_A.bin 程序和APP_B.bin 程序,对比执行两个程序在DSP 核0 上的资源利用率。

使用最低优先级线程执行占比的方式计算处理器的资源利用率,具体计算方式为,DSP 不执行任何线程,统计1 s 时间最低优先级线程执行的次数,记为countFull;DSP 正常运行所有功能时,统计1 s 时间最低优先级线程执行的次数,记为countNormal;则处理器资源利用率dspUsage 的计算公式为count Normal/countFull。

测试结果显示,在外部输入数据速率相同的情况下,运行单核程序时,DSP 核0 资源利用率为69%,运行双核程序时,DSP 核0 资源利用率为43%,多核程序的处理器资源利用率比单核程序的处理器资源利用率降低了26%。

5 结论

该文设计的多核数据处理与存储系统解决了信号数据处理过程中数据量大、存储性能慢的问题。经实验证明,使用多核协同处理完成数据处理和存储功能,有效降低了26%单核资源利用率,提升了系统的整体性能,系统工作稳定可靠。