基于Xilinx UltraScale+VU9PFPGA的SoC原型验证系统研究

丁 岩,王一鸣

(中国电子科技集团公司第四十七研究所,沈阳 110000)

1 引言

随着SoC设计规模的与日俱增,其功能日趋复杂,芯片的验证阶段占据了整个芯片开发的大部分时间。更多利用成熟IP核可减少SoC设计时间,但SoC验证仍然非常复杂与耗时。与一般ASIC验证的最大不同之处在于它的系统特性,SoC除了通常拥有更大的规模以外,往往有固件和软件的需要,如操作系统、驱动程序、通讯协议以及应用程序等,这使得软件仿真的速度会非常慢。因此需要在设计早期阶段使用FPGA原型来验证SoC中嵌入的软件,对系统进行软硬件的集成验证,以此大大加快芯片整体的验证速度[1]。从这一思路出发,提出一种基于Xilinx UltraScale+VU9PFPGA的原型验证系统。

2 系统架构

2.1 SoC系统架构

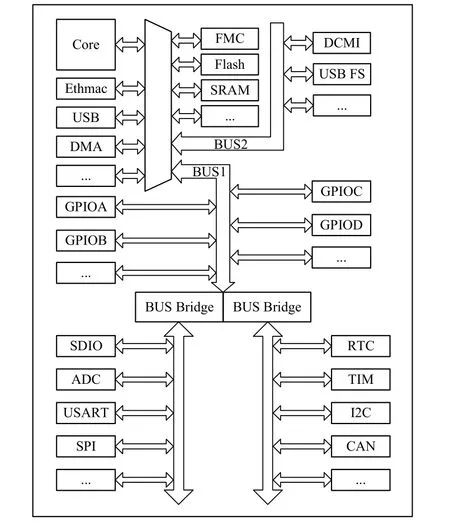

本FPGA原型验证系统所要验证的是一个SoC项目,其内部集成了Flash、SRAM及多个内部总线。总线上连接有DMA控制器、定时器、看门狗、RTC、CRC,以及丰富的通信接口,包括GPIO、AD转换器、DA转换器、I2C、I2S、SPI、USART、CAN、Ethernet MAC、USB、SDIO、FMC、DCMI、DMA2D、LTDC等模块。详细架构图如图1所示。

图1 待验证SoC的系统架构

2.2 FPGA原型核心板资源架构

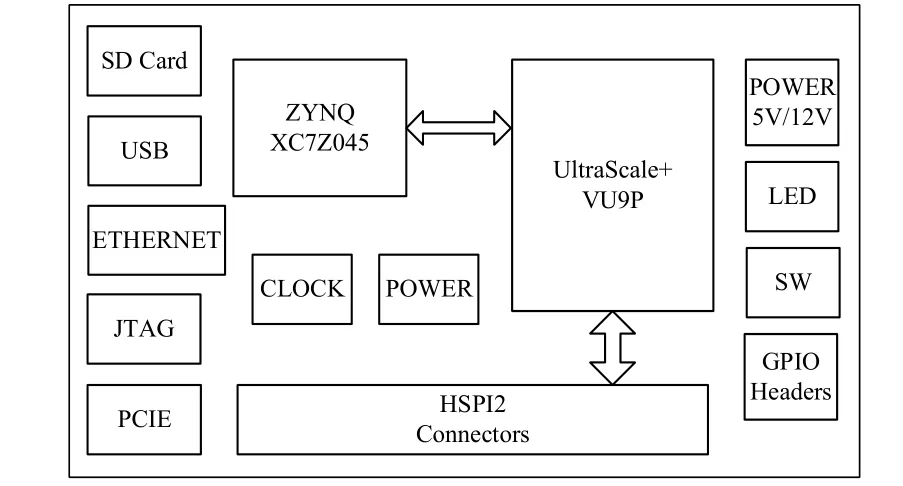

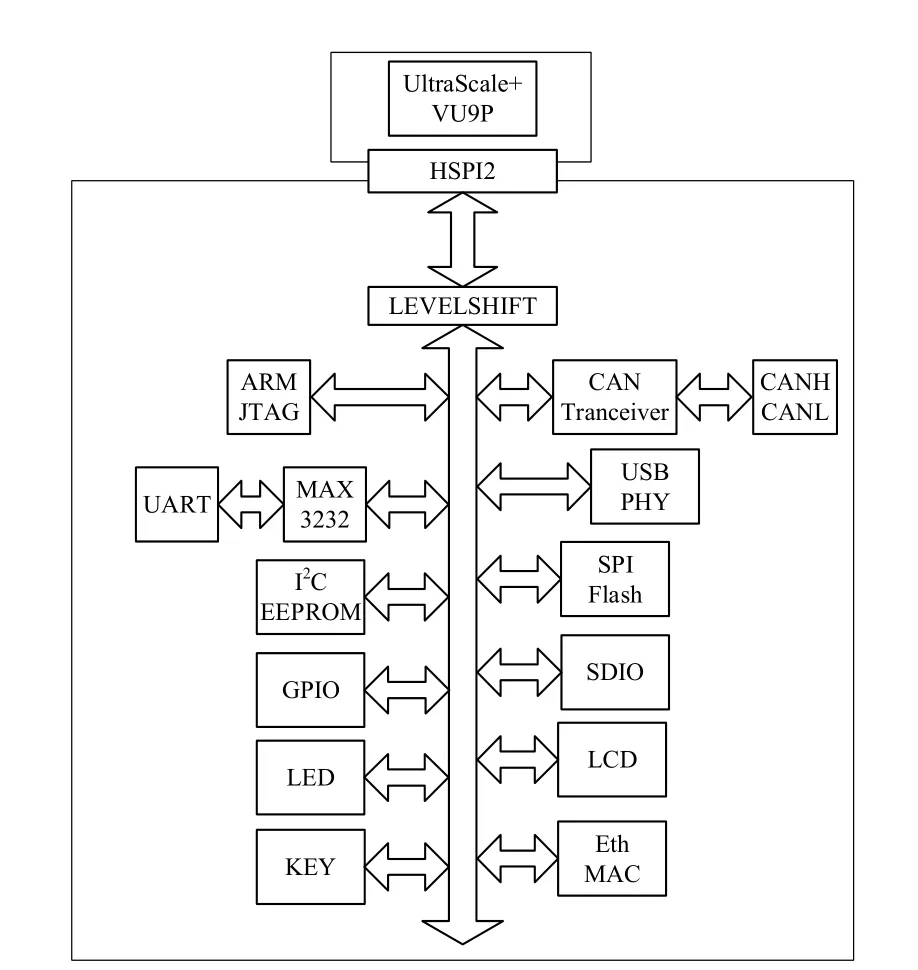

研究选用Xilinx UltraScale+系列的FPGA原型系统。该系统包含1片XCVU9PFPGA,1片ZYNQ XC7Z045用作系统控制器,另有丰富的外设和IO资源。VU9PFPGA核心板的结构如图2所示。

图2 VU9PFPGA核心板结构图

3 从ASIC到FPGA的移植

为了更高效更真实地验证SoC芯片的设计,需要将SoC芯片的数字逻辑部分以及模拟电路的数字控制部分移植到FPGA工程中实现。由于FPGA与ASIC在物理结构上的不同,ASIC的代码必须进行一定的转换后才能作为FPGA的输入。FPGA及第三方厂商已经实现并优化了很多典型的IP核,例如Xilinx提供了基础逻辑、总线接口与IO、数字信号处理、存储器接口、微处理器、控制器等大量IP核,在代码转换时可以充分利用这些资源。

在从ASIC向FPGA版本转换时主要需考虑三个因素:时钟、存储单元、IO单元。将SoC电路的全部功能引脚、GPIO、接口模块引脚映射至FPGA原型板的外部IO引脚上。根据各个引脚的具体功能,设计外接拓展子板,在子板上对电路的功能进行充分验证。

3.1 时钟移植

在ASIC中,用布局布线工具来放置时钟树,利用代工厂提供的PLL进行时钟设计。

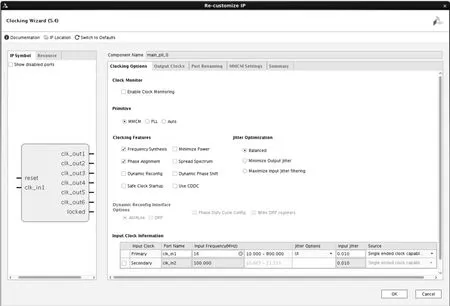

FPGA中通常已经配置一定数量的PLL宏单元,并有针对时钟优化的全局时钟网络,一般是经过FPGA的特定全局时钟管脚进入FPGA内部,再经过全局时钟BUF适配到全局时钟网络。这样的时钟网络可以保证相同的时钟沿到达芯片内部每一个触发器的延迟时间差异最小。对时钟的处理方法是使用FPGA内部PLL替换ASIC版本中的PLL。所设计FPGA的PLL由Xilinx提供的Vivado工具所生成[2-3],其时钟配置界面如图3所示。

图3 时钟配置界面

3.2 RAM资源替换

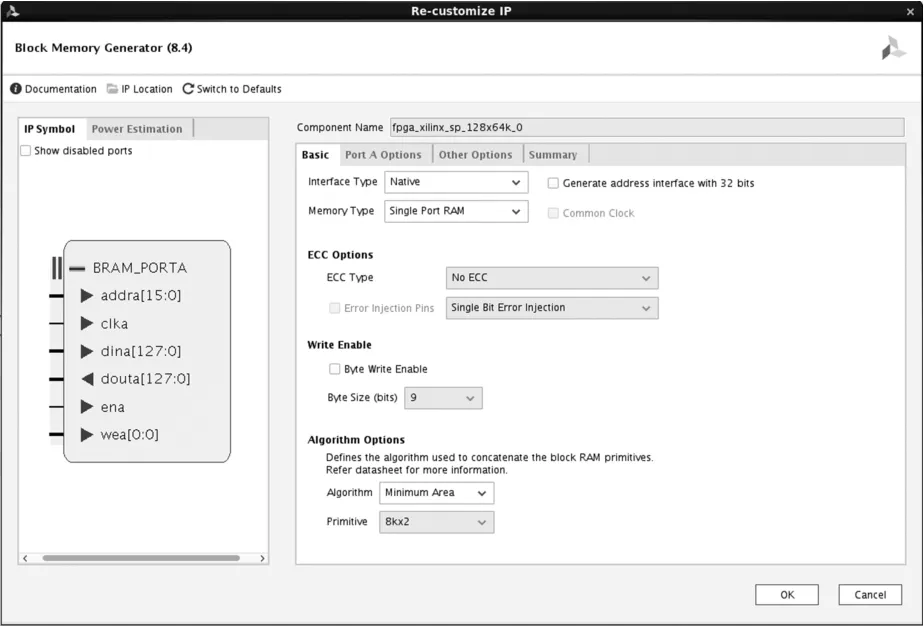

存储单元在ASIC向FPGA版本转化时,是必须进行代码转换的。ASIC中的存储单元通常用代工厂所提供的Memory Compiler来定制[4]。如果直接将ASIC代码中的存储单元作为FPGA的输入,通常无法直接综合,因此存储单元要进行代码转换。研究中SRAM的替换方法是使用Vivado工具中的Block Memory Generator。存储器配置界面如图4所示。

3.3 IO资源替换

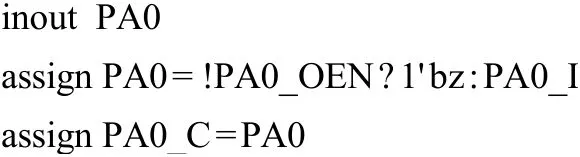

ASIC项目中的IP一般使用的是由Foundry提供的IOPAD,而在FPGA验证过程中,需要使用FPGA的PAD资源对其进行替换。FPGA中的双向IOPAD使用方法[5]为:先在顶层代码中使用双向IO的代码写法例化IO接口,以PA0管脚为例,代码为:

然后在工程XDC约束文件中定义管脚的pins约束以及电平标准。本项目中外设接口的电平标准为LVCMOS33。FPGA原型核心板的电平统一设计标准为LVCMOS18。最终IO电平约束方法如下[6]:

图4 存储器配置界面

4 FPGA原型子板设计实现

FPGA原型验证系统的选型应考虑待测产品的逻辑规模和硬件接口需求等因素。一方面,SoC设计规模的不断增大,对应着FPGA器件容量需求的增加。另一方面,FPGA器件的制造工艺也在不断提升,Xilinx UltraScale+系列FPGA现已进入16nm以下芯片工艺,FPGA的HP IO BANK电平标准只支持低电压电平标准[7]。因此,在子板的设计上使用电平转换器(Level Shifter)芯片对接口的IO电平进行转换。原型系统及子板系统结构如图5所示。

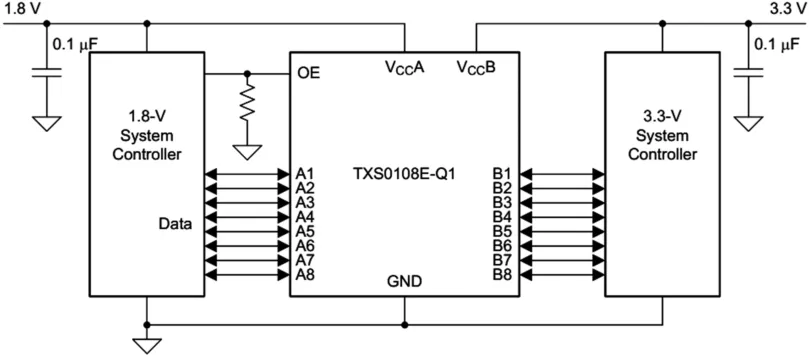

电平转换器电路选用的是TI的TXS0108芯片。这款8位非反向转换器使用两个独立的可配置电源轨,A端口跟踪VCCA引脚的电源电压,引脚可接受1.4V到3.6V范围内的任意电源电压;B端口跟踪VCCB引脚的电源电压,引脚可接受1.65V到5.5V范围内的任意电源电压。这两个输入电源引脚可实现1.5V、1.8V、2.5V、3.3V和5V电压节点之间的任意低压双向转换。TXS0108芯片电路原理图如图6所示。

图5 FPGA原型系统及子板系统结构图

图6 TXS0108芯片电路

5 软硬件协同验证

SoC软件开发环境基于MDK5实现。MDK是RealView MDK的简称,源自德国KEIL公司。MDK5由两个部分组成:MDK Core和Software Packs。其中Software Packs可独立于工具链进行新芯片支持和中间库的升级[8]。Real MDK支持多种SoC处理器内核,自动配置启动代码,集成Flash烧写模块,拥有强大的设备模拟、性能分析等功能。

本研究SoC项目中包含有MCO时钟输出引脚,可以通过程序选择内部PLL时钟、系统时钟(SYSCLK)输出以及配置时钟频率等。使用MCO管脚输出50MHz SYSCLK时钟。验证步骤为:首先在PC机上实现SoC系统的FPGA移植工程,经过综合、实现、生成比特流文件,通过JTAG-FPGA将比特流下载到FPGA中;在PC机上编写软件测试程序,通过JTAG-SoC由子板通道下载到SoC的存储器中,SoC核心读取并执行存储器中的指令,控制外围模块工作,从而验证SoC的设计功能是否正确。

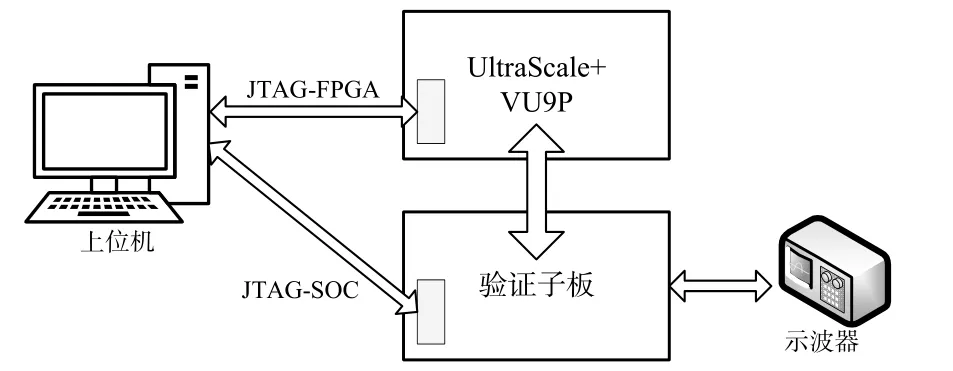

基于上述原理,搭建如图7所示FPGA原型系统环境,验证50Mhz时钟IO测试。

图7 FPGA原型系统环境

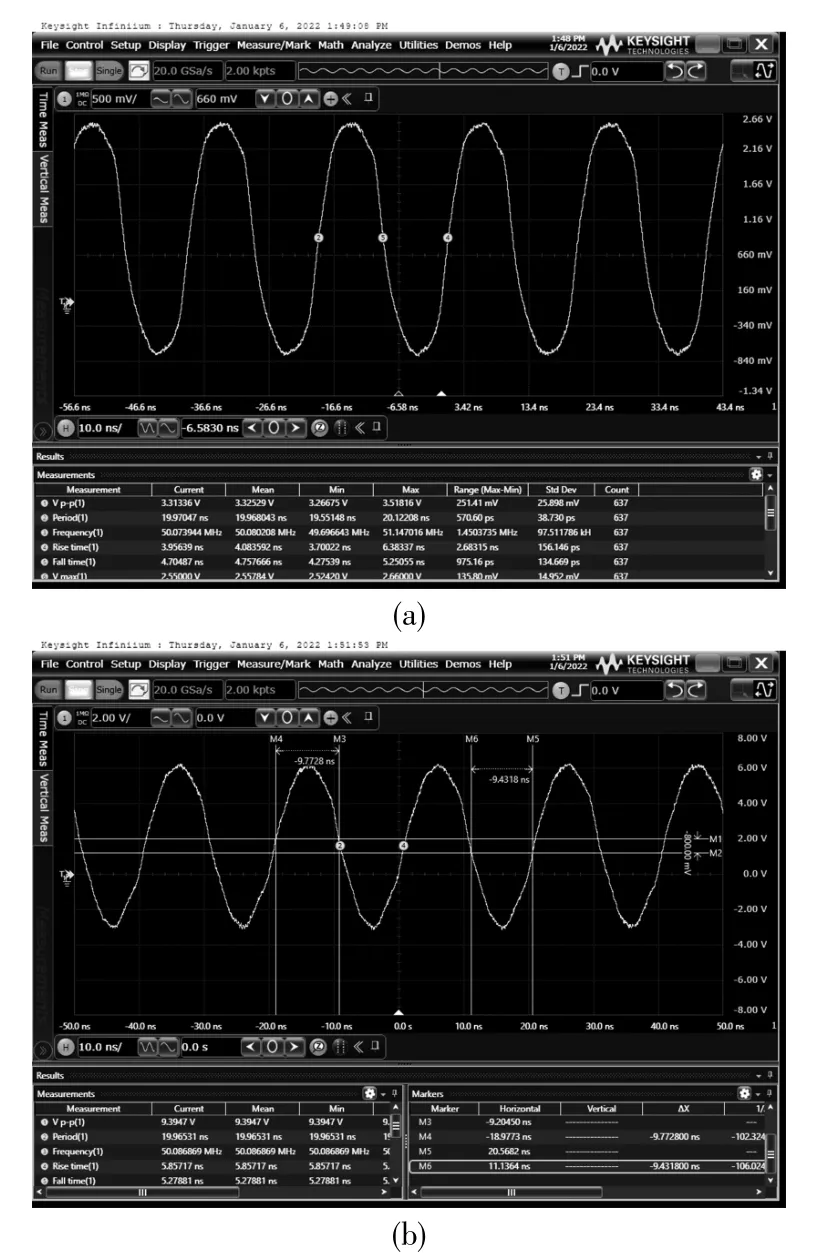

通过上述设计验证子板实验测试,使用以上电平转换电路,可以有效地将VU9P的核心板FPGA的原1.8V电平转换到3.3V标准电平。

TXS0108芯片电路信号实测结果如图8所示。图8(a)为在FPGA端1.8V电平下50Mhz频率的示波器实测信号;图8(b)则为在经过TXS1018芯片进行电平转换后3.3V电平下50 Mhz频率的示波器实测信号。根据示波器采样信号可以看出,信号转换功能正确,实现了设计的预期。

图8 TXS0108芯片电路信号实测结果

6 结束语

通过对Xilinx UltraScale+VU9P器件FPGA的原型系统的搭建,实现了研究SoC项目的软硬件协同验证。根据对实际信号的测量,电源转换电路的可行性也得到了验证,另外还在此平台上完成了部分其他通信协议的验证。研究为使用UltraScale+系列器件的FPGA进行3.3V电平下SoC原型验证提供了实测参考。基于FPGA的SoC原型验证是一项非常复杂的系统工程,其中还有诸多技术领域在未来有待更进一步的深入研究与提升。