数字化变电站合并单元自动误差校验技术及应用

王智,杨茂涛,杨静,孟卓,唐璐

(1.国网湖南省电力有限公司供电服务中心(计量中心),长沙 410000;2.湖南大学 电气与信息工程学院,长沙 410082)

0 引 言

智能变电站是衔接智能电网输-变-配-用等环节的关键设施[1-2]。合并单元是智能变电站中屏蔽互感器异构性的标准设备,能够完成电压、电流互感器输出信号的合并和数字化传输,实现信息采集与感知。合并单元的准确性直接影响智能变电站甚至智能电网的安全稳定运行[3-5]。

实际工作中,合并单元校验主要以互感器校验检定规程或标准为基础,一般整体测量和分析互感器与合并单元的综合误差,尚未建立单独针对合并单元校验的国家标准。国家电网公司于2017年制定了企业标准《数字化计量系统检测规范:合并单元》,为合并单元性能检测提供了依据[6-7]。文献[6]提出了一种分别独立对电子式互感器、合并单元进行误差测试及溯源的方法。为了克服频谱泄漏的影响,文献[7]提出一种基于加Hanning和Blackman窗插值FFT的算法用于合并单元校验中的信号分析。文献[8]提出一种基于ARM+FPGA+ADC的合并单元校验系统,并采用了基于定频采样高精度幅值和相位算法实现高精度测量。文献[9]为提高合并单元测试的通信报文处理能力和同步性,提出了一种基于FPGA+DSP的光数字量校准方案。文献[10]采用Hilbert变换实现相位微差算法,建立了合并单元校验溯源系统。这些工作有力地推动了合并单元校验技术的发展。但是,随着智能变电站技术的不断发展,合并单元已经同时具备继保和测量功能,如何在不停电前提下,运用一套合并单元校验系统中同时完成继保和测量功能的校验,是实际应用中面临的重要技术挑战之一。

因此,文中采用STM32微处理器和FPGA+DDS的硬件方案,运用GPS定时信号产生时间同步模拟信号,提出基于最小旁瓣卷积窗频谱相位校正的比差和角差计算方法,建立合并单元校验系统,完全保障合并单元的各项性能指标及其输入至保护、测控、计量装置的数据的准确性和可靠性,从而确保在发生保护、测控、计量装置输出数据误差过大时,能够快速判断变电站过程层和间隔层设备是否处于正常工作状态。测量实验结果验证了方法的准确性和有效性。

1 合并单元校验系统硬件设计

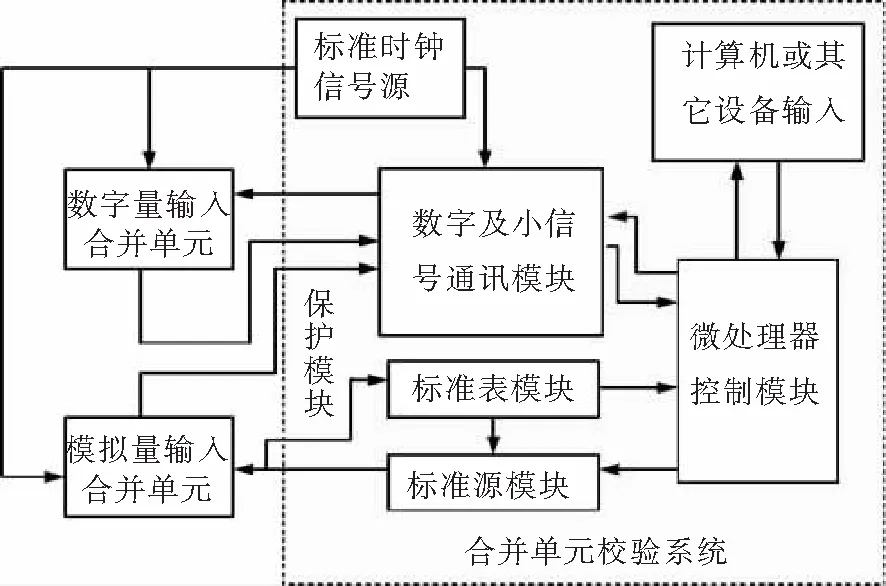

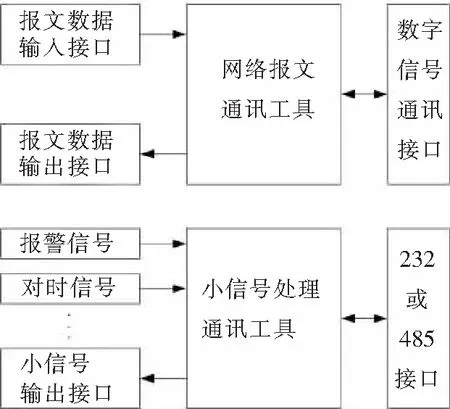

如图1所示。

图1 合并单元校验系统硬件功能框图

采用STM32微处理器和FPGA+DDS的硬件方案,设计的合并单元校验系统包括6个模块。

(1)微处理器控制模块:以ARM平台STM32的7系列微处理器为系统核心,STM32微处理器通过SPI与FPGA通信,FPGA直接连接数字分频DDS芯片。STM32微处理器进行实时测量、计算和控制,并实现IEC61850报文组包和解析。FPGA实时测量输出电量并计数,且控制电压电流量程切换和保护电路等。DDS产生同步信号,用于同步整个系统采样和输出。

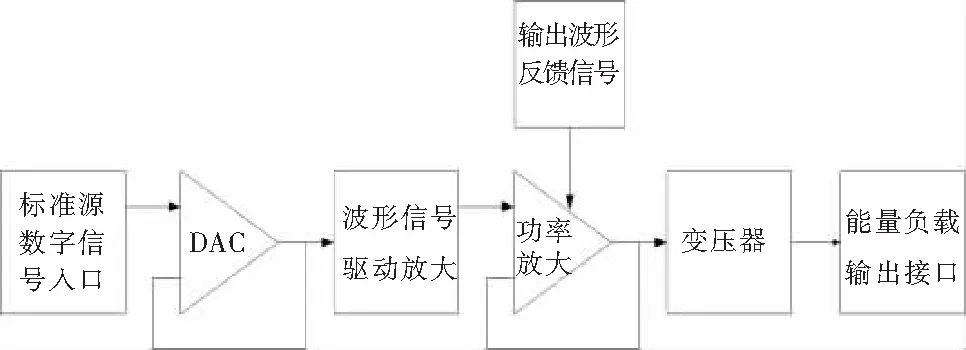

(2)标准源模块:由24位高速数模转换芯片(DAC)接收STM32微处理器的数字信号并转化为模拟量输出,经过精密运放的功率放大,再由电压/电流隔离输出变压器同步输出特定波形,其结构如图2所示。

图2 标准源模块电路功能框图

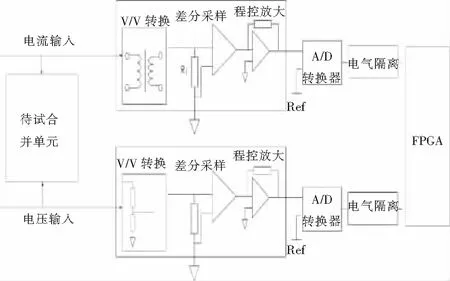

(3)标准表模块:对合并单元输入端的模拟电量进行采集测定,通过I/V和V/V转换电路将电压和电流统一转化为低电压。一方面用于标准源模块的反馈稳压,一方面送入32位高速模数转换芯片(ADC)进行精密采样。其电路详细结构图如图3所示。

图3 标准表模块电路功能框图

(4)数字及小信号通讯:合并单元的输出为SV和GOOSE报文,是基于IEC 61850或FT3协议的以太网或光串口通讯方式。该系统内置的网络报文通讯工具可以对于报文信息进行翻译和解读,同时对于报警一类的小信号进行响应。小信号同时包括带GPS的标准时钟基准和告警信号等,以测定单元的时钟功能。其电路详细结构图如图4所示。

(5)标准时钟信号源模块:能够通过接收GPS卫星信号,使用GPS定时信号产生相应的时间同步模拟信号,产生的同步模拟信号称之为标准时钟信号,主要分为IRIG-B码和1 pps信号两种,频率均为1 Hz。标准时钟源输出具有以下特点,以满足合并单元的对时需要:每秒1帧,包含100个码元,每个码元10 ms;脉冲上升时间不超过100 ns;秒准时沿的时间准确度优于1μs。

图4 数字及小信号通讯模块电路功能框图

(6)保护模块:包括过热、过载、断路和过量程保护。保护系统自身和外部的合并单元在各种异常情况下不会被破坏。保护模块中大量应用到了二极管整流,将需要被保护的信号整理为直流信号,一方面可以消除波形的抖动对保护的影响,另一方面增加系统的稳定性。一旦当被监控量超过阈值,微处理器会立即停止输出,并将大量模拟或数字量输入输出接口关闭,并显示出相应的错误代码给维护人员提示。

2 最小旁瓣卷积窗频谱相位校正比差和角差计算

2.1 最小旁瓣卷积窗频谱相位校正算法

设合并单元以采样间隔Ts=1/fs对电压或电流信号进行采样,且信号包含2-H次谐波:

(1)

式中第h次成分(h=1为基波,其余为谐波)的幅值、频率和初相位分别为Ah、fh和φh。文中采用长度为N的2阶最小旁瓣卷积窗wD(n)对采样信号进行加权,以抑制谐波成分对基波频谱的干扰[11-15]。其中wD(n)为两个相同的长度为N/2的最小旁瓣窗wMD(m),m=0,1,…,N/2-1,进行卷积后,在末尾补一个零得到:

(2)

其中,最小旁瓣窗wMD(m)为:

(3)

式中ai=[0.338 946, -0.481 973 , 0.161 054, -0.018 027]。2阶最小旁瓣卷积窗wD(n)的旁瓣峰值电平达到了-166 dB,具有优异的频谱泄漏抑制能力。因此,加窗后获得的序列xw(n)=x(n)w(n)的离散频谱中,可以忽略谐波成分的干扰影响,简化为:

(4)

式中WD(*)为2阶最小旁瓣卷积窗的离散傅里叶变换;k0=Nf1/fs为基波频率在离散频谱中对应的归一化位置。

XN中第l根谱线对应的相位为:

φ=φ1+πζ

(5)

式中ζ=k0-l0为非同步采样引起的偏差;l0为基波频率在离散频谱中对应位置附近的局部最大谱线序号。

设延后L个采样点后,选择长度的为N的连续采样点,同样采用2阶最小旁瓣卷积窗wD(n)进行加权,并进行离散傅里叶变换后,得到的离散频谱为XN-L。根据相位-频率的对应关系,在XN-L中第l根谱线对应的相位为:

φ′=φ1+πζ+2πf1L/fs

(6)

结合式(5)和式(6),两段不同起点的序列的相位差直接存在线性关系:

Δφ=φ′-φ=2πf1L/fs

(7)

f1=Δφfs/(2πL)

(8)

ζ=l0-ΔφN/(2πL)

(9)

进而将式(10)代入式(4),可计算得到基波幅度和初相位分别为:

(10)

φ1=arg[XN(l0)]-arg[WD(l0-k0)]+π/2

(11)

运用上述最小旁瓣卷积窗频谱相位校正算法,可以实现合并单元输出电压、电流离散序列频率、幅度和初相位的准确计算,为后续比差和角差计算机误差分析奠定基础。

2.2 比差和角差计算及误差分析方法

合并单元输出为电压、电流瞬时值,并以数字量的形式传输。在计量和测量功能方面,可将合并单元视为互感器的延伸,只需计算、校验合并单元的比差、角差。但考虑到合并单元需为智能变电站的保护、测控、计量装置等二次设备提供数据来源,文中设计的校验系统还进行了合并单元输出信号的频率、相位差、功率误差分析。这样不但能验证相对应的电压、电流之间的同步性,解决跨间隔两组电量的不同步性超过一个整周波而无法通过稳态绝对延时的方法检测的难题。在变电站发生量值超差时,所设计的系统可快速确定是否为合并单元的稳定性能出错,从而对智能变电站的故障诊断提供了更加便捷的手段。

对合并单元的数字量进行N点的FFT运算,并最小旁瓣卷积窗频谱相位校正算法计算得到的被校验的合并单元电压有效值UJ、频率fUJ和初始相位角φUJ,电流有效值IJ、频率fIJ和初始相位角φIJ。设校验系统中标准表模块给出的电压和电流的幅度、频率和初相位的真值分别为US、fUS、φUS和IS、fIS、φIS,则被校验合并单元的电压比差URE和角差UAE、电流比差IRE和角差IAE分别为:

(12)

(13)

(14)

(15)

电压和电流的频率误差分别:

2.2.1 迎接患者 核对无误,建立有效静脉通路,协助麻醉医师行全麻插管、桡动脉穿刺测压和深静脉穿刺等。

(16)

(17)

各次谐波的比差、角差和频率误差,合并单元的功率计算误差也可以同理计算。

3 合并单元时钟误差校验

由于合并单元存在多个环节(采样、处理、传输等),各环节的造成的延时各不相同,不可避免地对合并单元输出结果产生附加的相角差,直接影响保护装置的正确动作。因此,需要对合并单元时钟误差进行校验,以对合并单元的延时补偿方式、方法进行分析和调整,确保数据采样同步。

根据相关标准要求,合并单元应该能接收1 pps、IRIG-B(DC)或GB/T 25931(IEC 61588)协议的对时信号,合并单元正常情况下对时精度应不大于±1 μs。

合并单元的时钟误差校验一般用标准时钟源对被校验合并单元和合并单元校验系统进行授时,同时读取被检合并单元输出的时间信号,与校验系统读取到的标准时钟源信号进行对。参见图5,被测合并单元经校验仪输出光B码对时信号,待对时稳定时,然后撤掉对时信号,进行守时功能测试。在撤销标准时钟源授时之后继续监测被检合并单元输出的时间信号,并记录它能保持在规定范围的时间,即为该合并单元的有效守时时间。

图5 对时、守时误差校验原理

例如使用20 M标准时钟去测量被测合并单元送过来的PPS信号,计数得到P个脉冲,则误差=(1-P/20 M)*1 000 000(μs)。

在合并单元的绝对延时计算时,合并单元校验系统分别输出频率为f1和f2的标准模拟电压,用最小旁瓣卷积窗频谱相位校正算法计算进行分析,得到电压角差为UAE1和UAE2,则被校验合并单元的固定延时为:

(18)

4 实验及结果

文中首先通过三相标准功率源产生含有谐波的电压信号,通过数据采集卡采集后,运用最小旁瓣卷积窗频谱相位校正算法进行计算分析,验证算法的有效性;然后开展合并单元实际应用,计算比差、角差,测试合并单元时钟误差。

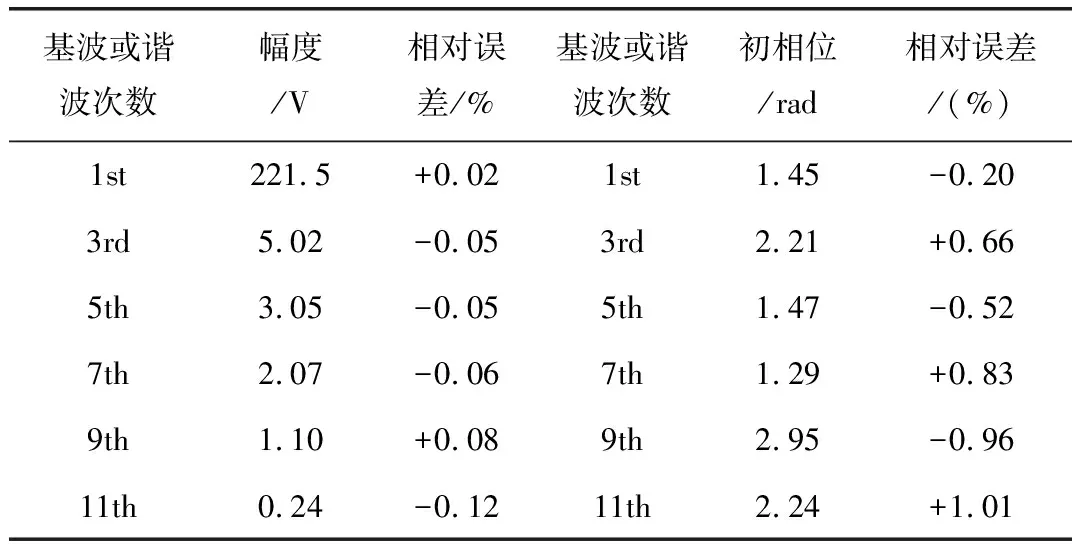

实验中使用的三相标准功率源为CL303B,其电压输出稳定度为10 ppm,采样频率为2.5 kHz,离散傅里叶变换的长度为512,基波频率设置为50.1 Hz。基波及谐波实验参数及幅度与初相位计算误差如表1所示。表1中所列的幅度和相位参数均为0.01级标准表所测结果。

表1 基波谐波实验参数及幅度与初相位计算误差

运用所开发的合并单元校验系统对湖南省某变电站合并单元进行测试。实际测试接线如图6所示。在1 h的传输延时测试中,最大传输延时为1 762.1 μs,最小传输延时为1 761.5 μs,传输延时变差为0.599 976 μs。

图6 对时、守时误差校验原理

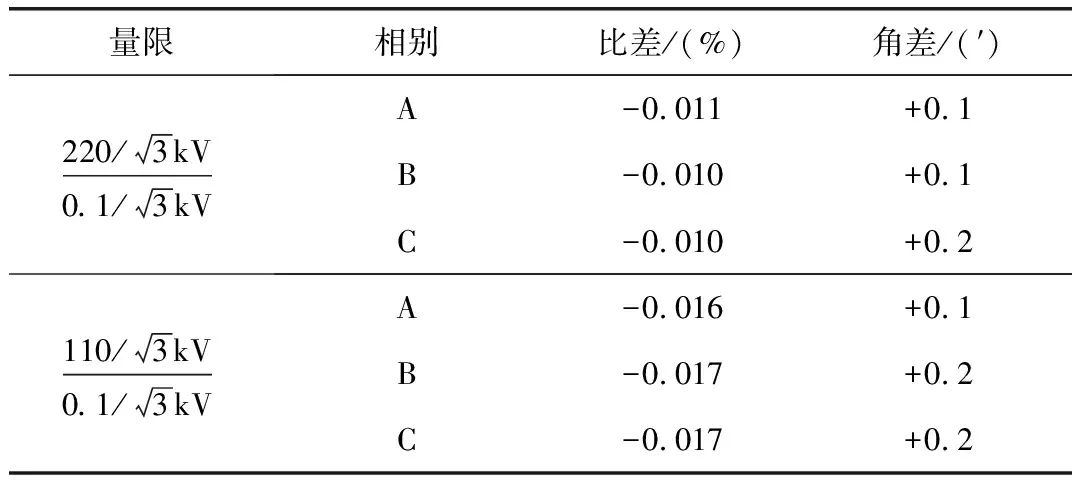

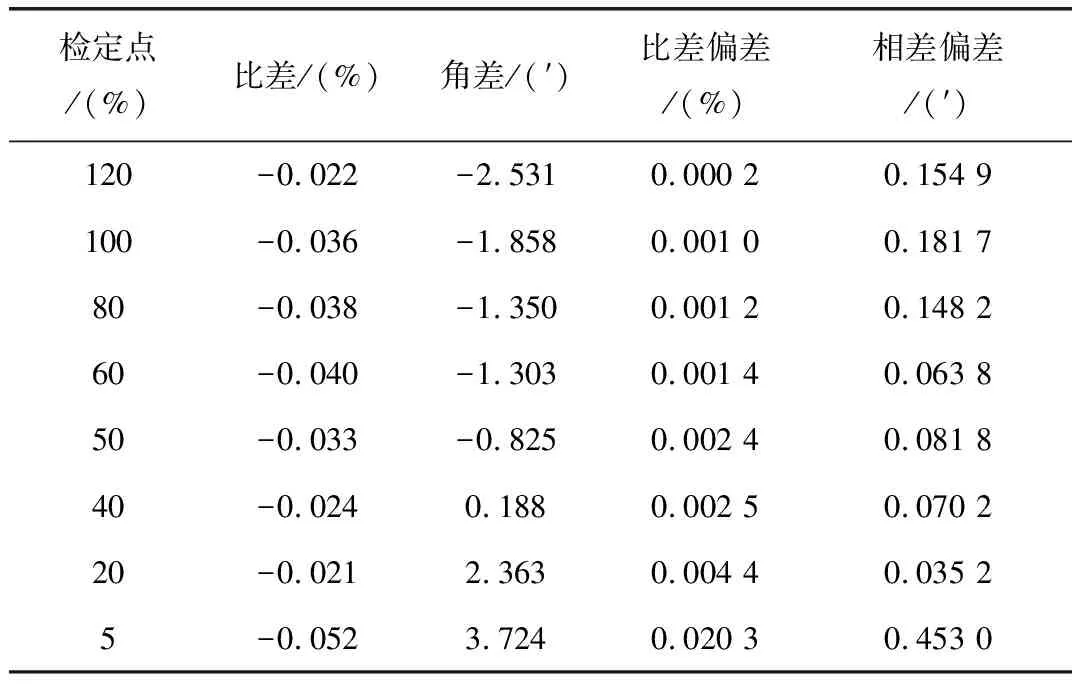

额定电流的百分数为100%时,某变电站合并单元电压通道30次测量的校验误差平均结果如表2所示。不同负载电流情况下,合并单元A相电流通道校验误差如表3所示。·

表2 某变电站合并单元电压通道校验误差

表3 某变电站合并单元A相电流通道校验误差

经过现场测试和功能验证,所设计的合并单元校验系统对合并单元的比差、角差等的校验或监测功能达到了国网企标的要求。

5 结束语

针对智能变电站对合并单元校验的迫切需求,文章设计可同时完成继保和测量功能校验的合并单元校验系统。提出基于最小旁瓣卷积窗频谱相位校正的比差和角差计算方法,设计的系统采用STM32微处理器和FPGA+DDS的硬件方案,运用GPS定时信号产生时间同步模拟信号实现合并单元校验功能。文中的工作为解决跨间隔两组电量的不同步性超过一个整周波而无法通过稳态绝对延时的方法检测难题提供新的途径,对智能变电站的故障诊断提供了更加便捷的方法。