p型4H-SiC单晶衬底表征及第一性原理计算

罗 东,贾 伟,王英民,戴 鑫,贾志刚,董海亮,李天保,王利忠,许并社

(1.太原理工大学,新材料界面科学与工程教育部重点实验室,太原 030024;2.中国电子科技集团公司第四十六研究所,天津 300220;3.山西烁科晶体有限公司,太原 030024;4.太原理工大学材料科学与工程学院,太原 030024)

0 引 言

碳化硅(SiC)作为第三代半导体,具有禁带宽度大、临界击穿场强高、电子饱和漂移速度快、热导率高、化学性能稳定等诸多优点,是制备高温、高频、大功率半导体器件的优质材料[1-3]。根据导电性质不同,SiC材料可以分为:半绝缘SiC、n型SiC和p型SiC。其中p型SiC单晶衬底作为一种导电型SiC衬底,在电力电子技术领域具有广泛应用,如SiC基肖特基势垒二极管(Schottky barrier diode, SBD)、金属-氧化物半导体场效应晶体管、结型场效应管等。此外,p型SiC衬底是制备SiC基n沟道绝缘栅双极型晶体管(insulated gate bipolar transistor, IGBT)器件的关键原材料,p型SiC制备的n沟道SiC IGBT器件在高压领域中具有开关速度快、功耗低等优点,已成为智能电网的核心器件[4-7]。

美国Cree公司最早开始对p型4H-SiC单晶衬底进行研发生产,制成了第一个采用p型4H-SiC衬底的IGBT,2008年报道了13 kV的n沟道碳化硅IGBT器件,比导通电阻达到22 MΩ·cm2,显示了其在高温、高压下应用的潜力,证明了p型4H-SiC衬底的可靠性[8];德国Enlangen-Nurnberg大学Hens等[9-10]采用改进的物理气相传输(modified physical vapor transport, M-PVT)法生长了1019cm-3载流子浓度的p型SiC单晶,通过生长p-n-p结构研究了6H-SiC中基平面位错形成动力学过程,显示p型掺杂对基平面位错有抑制作用;Sakwe等[11]优化了熔融KOH腐蚀n型和p型6H-SiC的腐蚀条件并计算了腐蚀反应能,提供了可靠的SiC缺陷表征程序;瑞典Ellison等[12]采用高温化学气相沉积 (high temperature chemical vapor deposition, HTCVD) 已实现了0.5 Ω·cm的小尺寸p型SiC衬底的生长;日本学者Mitani等[13]研究了Al和N共同掺杂的情况下,Si-Cr-C溶液中生长4H-SiC的电学性能,证明Al掺杂浓度的增加对电阻有明显的降低作用。张智[14]通过第一性原理方法计算并分析了掺N对于4H-SiC在形成能、能带结构、态密度、光学性质等方面造成的影响,结果表明N掺杂会导致体系禁带宽度变小,同时4H-SiC在高能端的吸收谱整体向低能端移动,使其在紫外波段有一个更大的透过窗口。作为制备高功率电力电子器件的理想衬底材料,p型SiC单晶衬底的电阻率却很难降低,由于工艺技术的制约,国内还无法大规模生产高质量、大尺寸、低电阻的p型4H-SiC单晶衬底,p型高效掺杂技术仍在研究阶段。因此,开发高质量、大尺寸、低电阻的p型4H-SiC单晶衬底迫在眉睫。

Al在SiC禁带中产生的受主能级相对较浅,使其成为最理想的p型SiC掺杂剂。本文使用物理气相传输(physical vapor transport, PVT)法制备了直径为4英寸(1英寸=2.54 cm)的Al掺杂p型4H-SiC单晶衬底。通过KOH腐蚀后计算位错密度,使用HRXRD、拉曼光谱面扫描和非接触电阻率测试等对衬底的结晶质量、晶型和电阻率等进行表征分析。利用第一性原理平面波超软赝势方法对本征4H-SiC和Al掺杂4H-SiC的电子结构进行计算,分析并解释相关机理,为制备高质量低电阻的p型4H-SiC单晶衬底材料提供理论基础。

1 实 验

1.1 样品的制备

本文通过PVT法生长p型4H-SiC单晶,使用的设备为中国电子科技集团公司第二研究所自主研发的单晶生长炉。图1为PVT法SiC单晶生长系统原理示意图,将SiC粉末和Al4C3粉末按25∶1的质量比混合后置入石墨坩埚中,粉料装置于坩埚底部,籽晶位于坩埚顶部,在坩埚的外部设有石墨环。生长开始前将生长室抽真空,在氮气、氩气混合气体的保护下进行高温生长,生长温度为2 000~2 200 ℃。对生长出的单晶进行滚圆和定向处理,获得直径为100 mm的标准晶锭,然后经过切割、研磨、抛光得到SiC衬底。

1.2 样品的结构表征及性能测试

利用游标卡尺、螺旋测微仪测量p型4H-SiC单晶衬底样品的直径、厚度。采用原子力显微镜(AFM, SPA-300HV, NSK)对样品表面粗糙度进行测试。经过KOH腐蚀后用显微镜(DM8000M, Leica)观察统计其位错密度。采用高分辨X射线衍射(HRXRD, D8 Discover, Bruker)仪测试样品(004)面的摇摆曲线,表征晶体结晶质量。采用拉曼光谱仪(Raman, LabRAM HR800, HORIBA JOBIN YVON)在532 nm激发光源下对样品进行检测,光斑大小直径为721 nm。采用非接触式电阻测试仪(RT, EC-80P, Napson)测试整片衬底的电阻率。

1.3 第一性原理计算

本文所有的计算工作采用Materials Studio软件包中的CASTEP模块完成。计算选用的参数为:广义梯度近似(generalized gradient approximation, GGA)下的超软赝势以及交换关联函数PW91,平面波截断能Ecut取为280 eV;布里渊区K点选择为5×5×7;自洽精度为1.0×10-6eV/atom。

2 结果与讨论

2.1 结构表征

如图2所示,样品为透明薄片状,呈现出p型4H-SiC单晶衬底典型的深蓝色,其直径(100.0±0.5) mm,厚度为(375.0±25.0) μm。通过强光灯及肉眼观察,衬底无裂纹、六方空洞、崩边等宏观缺陷。

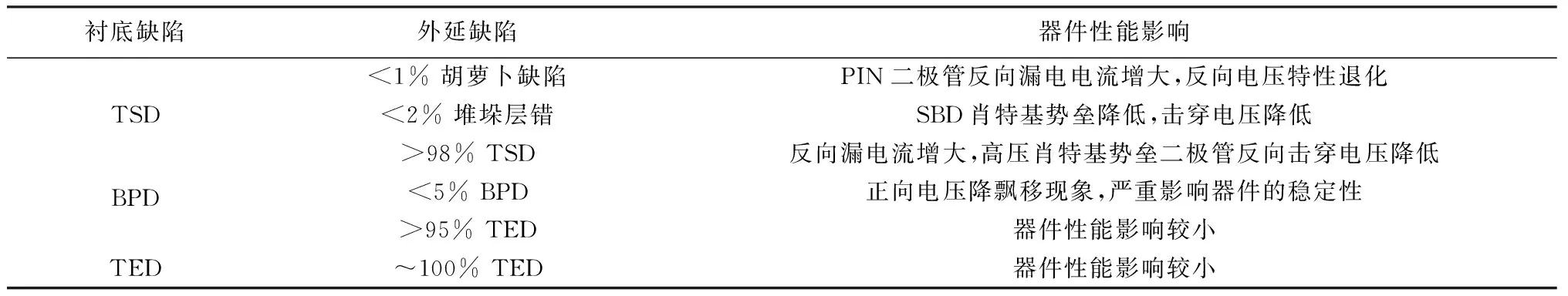

本文样品Si面经过化学机械抛光处理,通过AFM多点测得表面粗糙度小于0.2 nm,如图3(a)所示,其表面均方根粗糙度为1.309 nm。SiC单晶衬底中的缺陷会传递到外延中从而影响器件性能,具体影响如表1所示[15]。将本文所制备的p型4H-SiC衬底放入500 ℃的KOH熔融液中腐蚀10 min[16],检测p型4H-SiC的(0001)硅面,如图3(b)所示,较大尺寸的六方形腐蚀坑为螺位错(TSD),腐蚀坑形貌为大的六角形,有尖的底且稍微偏向一边,衬底的TSD缺陷会导致外延产生少量胡萝卜缺陷、堆垛层错以及大量的TSD,从而严重影响器件的性能。较小的六方形腐蚀坑为刃位错(TED),腐蚀坑形貌为小的六角形,有尖底且稍微偏向其中一边,该类型的位错会导致在外延中产生TED缺陷,但这种缺陷对器件的性能影响较小。椭圆形腐蚀坑为基平面位错(BPD),腐蚀坑的形貌为椭圆形,有底且严重偏向椭圆的一边,该种类型的位错大部分导致外延时出现TED位错,同样对器件的影响较小[17-18]。碳化硅单晶片平均位错密度按照公式(1)进行计算:

表1 SiC中的位错缺陷及其对器件性能影响[15]Table 1 Dislocation defects of SiC and their influence on device performance[15]

(1)

通过HRXRD对p型SiC单晶衬底的结晶质量进行表征,如图4所示,该衬底(004)衍射面摇摆曲线的半峰全宽(full width at half maximum, FWHM)为31.9″,整个摇摆曲线为一个近乎对称的单峰,且无多峰出现,说明整个衬底具有良好的结晶质量,并且没有小角度晶界缺陷。

图5是本文制备样品的拉曼测试图,拉曼峰对应简约波矢x=0.5的折叠横声学(FTA)模,样品去除边缘3 mm后均匀选取286个点进行测试。图5(a)所示为p型SiC衬底拉曼特征峰强度面扫描结果示意图,颜色越接近代表衬底的结晶程度越好,从图中可以看出颜色较为均匀,表明该样品结晶程度很好。按照样品测试点位置从边缘到中心再到边缘的顺序对286条测试谱图进行排列对比分析,结果如图5(b)所示,发现其与文献[19]所报道的4H-SiC特征峰204 cm-1相比的最大偏差为0.67 cm-1,无其他杂峰出现,且样品中心特征峰强度高于边缘,测试结果表明本文制备的p型衬底无异型,为均匀的4H-SiC晶型。

通过二次离子质谱对样品中的Al浓度进行表征,结果显示本文所制备的p型4H-SiC单晶衬底中的Al掺杂浓度为4.441 3×1018cm-3。

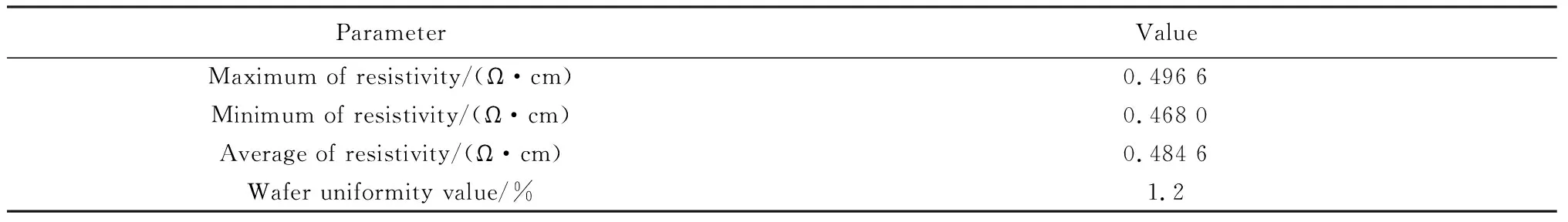

2.2 电阻率测试

本文采用非接触式低阻测试仪对p型4H-SiC单晶衬底进行电阻率测量,取点数量为55个。如图6所示,电阻率等值线图直观显示出衬底的电阻,表2给出了样品详细的电阻率最大值、最小值及平均值,可以发现Al掺杂的4H-SiC衬底全部面积电阻率小于0.5 Ω·cm,均匀度低至1.2%,表明p型4H-SiC单晶衬底样品的电阻率非常均匀。

表2 p型4H-SiC衬底样品电阻率Table 2 Resistivity of p-type 4H-SiC substrate

2.3 第一性原理分析

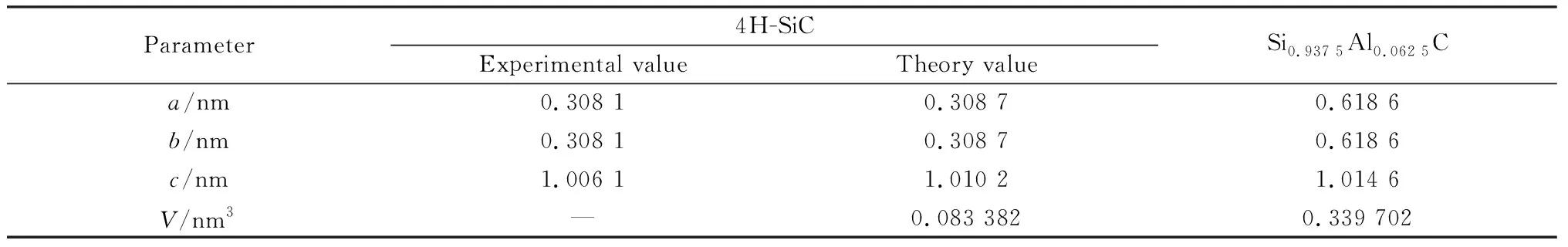

4H-SiC属于六方相结构,空间群为P63mc,晶格常数是a=b=0.308 1 nm,c=1.006 1 nm,α=β=90°,γ=120°,由此建立起4H-SiC单晶胞框架,如图7(a)所示。由于计算能力的限制,超晶胞不能无限扩大,结合计算能力并参考本文样品中Al的掺杂浓度,选取了2×2×1(32原子)的超晶胞模型进行计算。

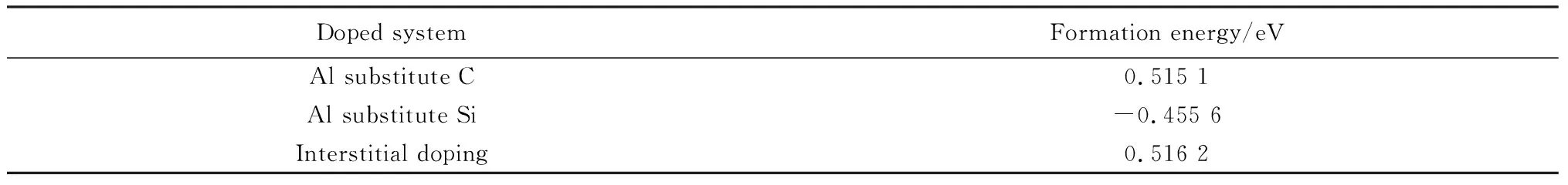

Al掺杂4H-SiC有替位C、替位Si和间隙掺杂三种形式,本文首先对三种体系的形成能进行了计算,形成能越低则表示体系越稳定。形成能的计算公式[20]如式(2)所示:

Eform=E′tot-Etot-EAl+EC(Si)

(2)

式中:E′tot表示Al掺杂后超晶胞体系的总能量;Etot表示本征超晶胞体系的总能量;EAl表示掺杂原子Al的能量;EC(Si)表示被替换原子C或Si的能量。当对间隙掺杂体系的形成能进行计算时,因未有原子被替换,故公式中的EC(Si)不存在。不同体系下的形成能如表3所示。

表3 不同体系下的形成能Table 3 Formation energy under different doping conditions

通过表3可以看到,三种掺杂体系中Al替位Si时能量最低,且Al与被替换Si的原子大小和价电子壳层结构更为接近,整个体系相比其他两个更加稳定。故本文超晶胞模型中用一个Al原子取代一个Si原子,形成Si0.937 5Al0.062 5C,所建立的超晶胞如图7(b)所示。

表4是4H-SiC本征单晶胞、Si0.937 5Al0.062 5C超晶胞的晶格常数及晶胞体积的对比,从数据中可以看出,Al掺杂后4H-SiC的晶格发生畸变,由于Al原子半径大于Si原子,替位掺杂后键长变得更长,因此晶格常数增大,晶胞体积也随之变大。

表4 晶格常数与晶胞体积Table 4 Lattice constant and unit cell volume

基于第一性原理平面波超软赝势方法,对六方相4H-SiC本征体系和掺杂Al元素体系的能带结构、电子态密度进行了计算分析。图8是本征4H-SiC的能带结构,GGA方法导致模型中激发态电子间的关联作用被低估,计算所得本征4H-SiC的禁带宽度为2.242 eV,低于实验值3.27 eV[21]。GGA计算法作为一种有效的近似方法,其计算结果的相对值对能带和态密度的分析并不会产生影响,具有一定的可靠性[22]。如图8(a)所示,价带顶位于0 eV,导带底位于2.242 eV,禁带宽度为2.242 eV,其价带顶与导带底不在同一K点,表明本征4H-SiC为间接带隙半导体。而Al掺杂后能带结构与本征4H-SiC相比,导带底和价带顶均位于G点,看似转变为直接带隙,实际是超晶胞的能带相对于原胞发生了折叠[23-24],这是由于表达方式的变化引发的假象。Al掺杂后的超晶胞能带结构发生偏移,如图8(b)所示,该体系下能带结构整体向上移动,导带底上移了0.122 eV,价带顶却上移了0.289 eV,价带上移程度大于导带,所以Al掺杂后禁带宽度减小为2.075 eV,这是由于Al掺杂后替代了Si的位置,Al原子最外层只有三个电子而Si原子最外层有四个电子,从而在价带顶附近Al原子提供了可以接受电子的受主能级,产生的空穴导致费米能级进入价带,因此体现出p型掺杂半导体材料的特征。

图9(a)是本征4H-SiC的电子态密度(density of states, DOS)图,从总的电子态密度图中可以看出,导带主要位于费米能级以上2.242~11.8 eV的能量范围中,主要由Si的3p态贡献,而Si的3s态和C的2s态、2p态的贡献则相对很少。可以从图中明显看到价带被分成两个子价带。其中-15.7~-9.8 eV低能区的价带主要由Si的3s态、3p态和C的2s态共同构成;而价带高能区中-8.85~-5.82 eV主要由Si的3s态和C的2p态贡献,-5.82~0 eV主要由Si的3p态和C的2p态贡献。Al掺杂4H-SiC的电子态密度图如图9(b)所示,导带主要位于费米能级上方2.364~6.27 eV的能量范围内,由于一个Si原子被Al原子替代,导带变为主要由Al的3p态,Si的3p以及C的2p态共同贡献。和本征4H-SiC电子态密度一样,价带被明显分为低能区和高能区两部分。其中-15.3~-9.7 eV的价带低能区主要由Si的3s态、3p态以及C的2s态构成,而-8.5~0.29 eV的价带高能区主要由Al的3p态、Si的3p态以及C的2p态共同构成。在导带底和价带顶都有Al的3p态参与,且从能带图中也可以看出Al掺杂后能级数明显增加,可见Al的3p态在Al掺杂的体系中发挥了非常重要的作用。

3 结 论

本文采用PVT法成功制备了Al掺杂p型4H-SiC单晶衬底,通过AFM、HRXRD、拉曼和电阻率测试等对其进行表征,结果表明现阶段制备的p型4H-SiC衬底晶型稳定,缺陷较少,结晶质量也得到了很好的控制,但电阻率依然相对较高,影响相关器件的性能。通过CASTEP软件计算分析了本征4H-SiC和Si0.937 5Al0.062 5C体系的能带结构和态密度变化,发现Al掺杂后晶格发生畸变,禁带宽度明显变小,费米能级穿越价带,体现出p型半导体的特征。研究结果为Al掺杂的p型SiC材料高效掺杂技术发展提供了思路,从而进一步降低p型4H-SiC衬底的电阻。