基于Zynq的16通道高精度数据采集系统

曹尚斌,韩建宁,马瑜涓,郝国栋,卫国倩

(中北大学信息与通信工程学院,山西 太原 030051)

0 引言

数据采集作为现代信息处理的首要问题,显得越来越重要。随着工业、农业和医疗等行业的不断发展,需要进行数据监测的对象逐渐增多,而数据采集是进行数据监控的重要部分,如何高效地获取数据成为一个关键的问题。随着嵌入式技术的提高,越来越多的嵌入式系统被应用在高精度数据采集系统中。在实际应用过程中,单一的FPGA或者ARM在某些领域不能满足使用者的需求,所以自赛灵思公司的Zynq系列产品问世以来就广受关注,赛灵思公司的Zynq系列是集成了双核ARM Cortex-A9处理器以及纳米级工艺的FPGA 的可扩展处理平台[1]。在Zynq系列芯片中,FPGA与ARM通过AXI4传输协议进行数据的交互,可以很好地降低系统的延迟,提高处理性能。在系统软件流程的设计方面,计划使用赛灵思公司开发的集成设计环境Vivado设计套件进行设计,此集成设计环境工具把各类可编程技术结合在一起,并且提供了可供多种类型实验的IP核,可以满足各种实验设计的需求以及多种复杂算法的设计。

1 系统结构

Zynq-7000系列可扩展平台是整个数据采集系统的核心,以1片赛灵思公司的Zynq-7000系列芯片以及2片AD7606采集芯片进行16通道的并行数据采集[2-4],通过HDMI在上位机显示采集结果。该系统通过40针(实验只用到其中的34个针口)的扩展口实现AD7606与Zynq-7000芯片的数据通信,每个扩展口上为了完成不同的工作要求设置了几个不同电压为电源的通路,同时有34路IO口可以进行通信传输。IO口在芯片内部连接到芯片PL端的BANK35上,为了防止芯片PL端在电压过高时损坏芯片,在2个扩展口J10和J11与PL端相连接的中间都加入了33 Ω的排阻。由于所使用的是2片AD7606板卡,所以需要分别在Zynq-7000芯片的J11和J10扩展口分别接1片AD7606。该扩展口位于PL(可编程逻辑)端,使用硬件描述语言进行AD采集控制代码的编写,并且将编写好的程序通过Vivado开发软件封装为1个后期可以随意调用的IP核,加入 IP 核以后,系统会自动使用 AXI 接口将 IP 核与处理器连接起来[5-6]。

该采集系统的整体工作流程如图1所示,2路模拟信号分别从2片AD7606的信号输入端输入,连接在Zynq-7000开发板2个扩展口的AD7606数据采集芯片,接收到进行采集的命令后进行1次8通道全部打开的并行数据采集,然后将有效通道的数据进行1次A/D转换,并且将数据放入到PL端进行储存,通过DMA控制器来进行数据传送的管控可以减少系统资源的损耗,为了防止在进行数据传输时出现信息传输不稳定的问题加入先进先出(FIFO)寄存器,先进先出寄存器可以实现跨时钟域的数据传输, 解决AD控制器与AXI4总线时钟频率不一致的问题。将PL端的数据传输至PS端的DDR3存储器中。经过ARM驱动后,将数据从HDMI端口传出最终显示在终端上位机[7-9]。

2 数据采集系统的硬件设计

2.1 XC7Z010-1CLG400C

Zynq作为全新的全可编程和系统芯片(SoC)体系结构,由最新系列的28 nm FPGA和Xilinx的双核高性能高级RISC机器(ARM)Cortex-A9处理器组成,在此基础上整个处理平台搭建的核心都是处理器,并且由于处理器之中集成了大量外设以及内部控制装置,使得在不使用Zynq-7000系列的FPGA部分时,该开发板的ARM区仍然可以独立使用,这更体现了Zynq的优势所在。在基于Zynq的读出模块中,具有可编程逻辑(PL)和处理系统(PS)之间的高速数据传输同时包含了低功耗(HPL)、高性能等优点。

本实验所使用开发板是ALINX的7010开发平台,其核心控制器型号为XC7Z010-1CLG400C,芯片为BGA封装。Zynq-7000系列的开发板在此芯片的外部搭载了大量的通信外设,以及上百个引脚,同时极小的引脚间距大大缩小了开发板的体积,使得其更加灵巧。此开发板的2片DDR3芯片的内存为512 MB,还具有1 066 Mbit/s的最高运行速度,极大地满足了客户的需要,并且可以进行多种功能的实验。1片EMMC和1片QSPI Flash,这些与系统的CPU、内存、Flash、SDRAM以及AD7606组成了本实验的高速存储最小系统[10]。

2.2 A/D转换单元设计

使用2片AD7606进行信号的同步采集与显示。AD7606作为1款集成16位、同步采样、模数数据采集的系统(DAS),最大可以同时进行8通道的数据采集。AD7606包括了输入钳位保护、输入信号缩放放大器、二阶抗锯齿滤波器、跟踪和保持放大器、片上参考、参考缓冲器、高速ADC、数字信号滤波器以及可以高速数据传输的串口输出。多应用于电力线路监测和保护系统、多相电动机控制、仪表和控制系统、多轴定位系统以及数据采集系统。

AD7606采集芯片在进行数据采集时会将所有的8通道全部开启,BUSY信号在该芯片的8个通道完成数据转换之前会一直以高电平输出。只有在将8个通道的所有数据完成转换并且存入到输出寄存器之后,BUSY信号才会拉低并等待下一轮的信号采集。当CS和RD在并行模式下均为逻辑低电平时,输出总线启用,输出总线启动后进行8通道的数据读取,在数据读取完成后将所有读取到的数据进行存储。

为了精简设备以及使2片AD7606之间有良好的匹配性能,将2片AD7606采用对称分布,这种布局可以在高通道数的采样系统中保持高精度。在此布局的基础上,将2个采集芯片的A/D转换信号CONVSTA与CONVSTB分别相连,这样方便进行同步控制并实现同步采样。

设计中使用8个输入通道中的1个通道进行采样,DB0~DB15为16位数据总线。在进行数据采集时,为了实现2片AD7606芯片真正的同步采样,将2片AD芯片的采样使能信号与读数据触发信号由Zynq统一进行调配控制[11]。

3 数据采集系统的软件设计

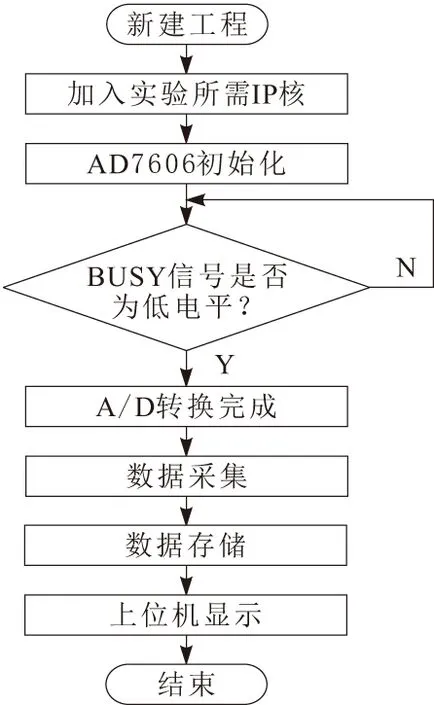

根据软件操作流程,首先新建工程,根据实验要求使用Verilog语言设计操作Zynq的程序以及根据实验所需加入IP核。在系统上电后利用开发板外部的RESET按钮进行系统的复位,按下该按钮后会产生1个脉冲复位信号,该信号被发送至AD采集芯片的复位点进行AD7606的初始化操作,进行完初始化操作之后进行BUSY信号的判断,只有当BUSY信号为低电平时,A/D完成转换,否则继续等待BUSY信号再进行下一次判断,在A/D转换完成之后进行数据的采集与存储,同时通过Zynq板卡的HDMI接口连接到上位机将采集到的信号进行显示。数据采集流程如图2所示。

图2 数据采集流程

3.1 数据传输

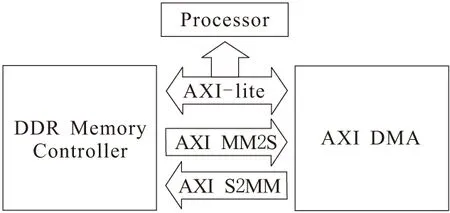

本设计中,在进行数据传输时首先进行时钟的设定,在Zynq的PS端设置50 MHz的输出时钟,然后为了减少逻辑单元的使用,使用轻量级地址映射单元传输接口进行DMA工作模式的配置,通过PS端将数据写入DDR3存储器。为了精准地控制AXI DMA与DDR的数据交互问题,设计加入HP高速接口,然后再将之前写入DMA模块的数据进行读出操作[12],将读出的数据写入配置好的FIFO寄存器,添加1个中断信号,最后通过控制DMA并通过AXI总线将写入FIFO的数据流再次发送回DDR之中,再添加1个中断信号,完成上述操作后PL端通过AXI总线进行1次DMA数据的读写操作,完成数据的传输。芯片内部数据传输如图3所示。

图3 芯片内部数据传输

3.2 上位机显示

进行上位机显示时,核心板内部直接将板子的3.3 V差分IO口与板子的外设HDMI接口进行连接,PL板块的FPGA完成TMDS与RGB的转换。在进行实验时,将HDMI转接线一端与核心板相连接,另一端与上位机相连接进行波形显示[13-14]。HDMI的工作流程如图4所示。

图4 HDMI工作流程

进行设计时,将HDMI的输出显示部分划分为7大工作模块。通过时钟模块进行硬件工作频率的设置,信号转换模块完成VGA信号与DVI信号的转换,画布背景生成模块以及叠加网格模块用来设置波形显示的背景以及网格间隙。在进行数据传输时通过设计1个接口模块完成与采集芯片AD7606的连接,主要完成8路信号的采集功能。采样模块在进行定量数据采集时,将每路输入的数据转换为无负数的无符号数,再进行高8位的数据读取。波形显示模块使用1个双口的随机存储IP核进行采集数据的读写,在进行波形显示时将该模块中存入的数据读出[15]。

4 实验结果分析

通过HDMI数据线将主控开发板与上位机连接,同时将2片AD7606分别连接在开发板的2个扩展口上,通过信号发生器将2路信号分别输入采集芯片,所设计的16通道数据采集系统整体如图5所示。

图5 设备总体

将信号发生器的A路设置为1 V、1.0 kHz的正弦波,B路设置为5 V、1.5 kHz的正弦波,分别输入2个采集芯片的第1通道。

串口打印数据如图6所示。由于本次实验只使用到第1个通道进行波形采样,所以可以从图6看到1通道的数据变化幅度是在-0.5~+0.5 V之间,符合所设置的正弦波幅度,其他通道的电压幅值变化为0.000 2 V,误差在0.01%,可以看出本文设计的采集系统精度达到预期水平。

图6 串口数据打印

AD7606的采样频率为200 kHz,采集时将2个板子的16个通道全部开启,但是只采集每个板子的1路信号。实验结果如图7所示,在HDMI上显示的正弦波信号即为该系统所采集到的信号。

图7 实验结果

为了充分实验验证,满足可重复性要求,进行了2路相同频率与幅值的波形测试,测试结果如图8所示。由图8a可知,经过显示部分代码调整,将2路波形分成上下2部分显示,上半部分1路波形幅值为2 V,下半部分1路波形幅值为5 V。由图8b可知,上位机显示波形与波形发生器输入波形对比完全一致。上述实验证明该系统可以完成全部通道的数据采集与显示功能。

图8 测试波形

经过测试表明,使用Zynq与2片AD7606所搭建的信号采集系统,可以完成16通道的高精度信号采集与波形显示功能。

5 结束语

针对多通道的数据采集与显示功能的问题,利用Xilinx公司的Zynq-7000系列开发板以及2片AD7606设计了一种16通道高精度同步数据采集与显示系统。本文系统设计中使用DMA进行数据的传输,通过锁相环调控频率,同时加入FIFO寄存器以避免出现AD控制器与AXI4总线时钟频率不一致的问题,后通过ARM将存储在DDR3中的数据通过HDMI接口在上位机显示出来。经多次实验证明,本文系统可以完成所需功能,在后期进行更多通道采集时可以作为基础模块,节省了开发时间。