数字信道化高效结构设计及FPGA实现

邓 强

(中国西南电子技术研究所,四川 成都 610036)

信道化接收机具有灵敏度高、频率分辨率高、截获概率接近100%、选择性和抗干扰能力强等优点,但传统模拟信道化接收机存在结构复杂和实现成本高等缺点,限制了它的发展和应用[1]。近年来,随着高速模数转换芯片(Analog-to-Digital Converter,ADC)和现场可编程逻辑门阵列(Field Programmable Gate Array,FPGA)等芯片性能的不断提高,使得数字信道化接收机工程化的实现成为可能[2],推动了宽带数字接收机技术的迅猛发展[3-5]。

目前的文献对数字信道化接收机的研究以理论为主,较少给出基于实际器件的工程化实现方法。针对以上问题,笔者首先从多相滤波和采样率等价交换原理出发,推导出数字信道化模型的偶型排列和奇型排列高效结构;在此基础上将高效结构进行模块划分,结合FPGA芯片特点,分析并设计了各模块的具体实现方案,给出了具体时序工作条件和逻辑资源消耗结果,从而保证数字信道化后输出信号工作频率适中,能够满足后续基带信号处理的要求;最后,对利用硬件描述语言(Hardware Description Language,HDL)实现的基于FPGA芯片八通道数字信道化接收机进行了充分的仿真验证与在线测试,验证了该数字信道化接收机实现方式的合理性,其可以对同时到达的多个信号进行实时处理,且逻辑资源消耗小。

笔者提出的基于FPGA的数字信道化接收机实现方式,具有时钟频率适应范围广、与具体器件耦合小和移植方便等特点,工程应用价值较高。

1 高效结构

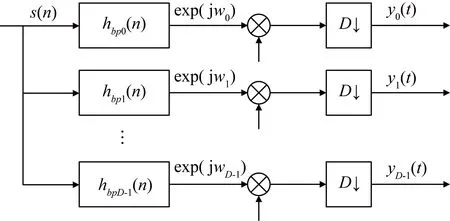

信道化技术的基本思想是把整个信号处理带宽划分成若干个均匀的子信道,并通过滤波器组提取出对应子信道中的信号[6],其模型的原理框图如图 1所示。

图1 信道化模型

滤波器的冲击响应分别为hbp0(t),hbp1(t),…,hbpD-1(t);通过滤波降样后,输入信号s(n)被分解为一系列子信号y0(t),y1(t),…,yD-1(t)。图中D个滤波器的功能是把宽带信号s(n)分成D个子频带滤波输出,覆盖整个频带,因此构成了一个信道化滤波器组。该滤波器组将整个无模糊采样频带划分为若干个并行的信道输出,使得信号无论何时在任何信道出现,均能加以处理。对信道的划分通常采用均匀划分方式,各滤波器间无频谱混叠。滤波器的理想低通原型滤波器频率响应为

(1)

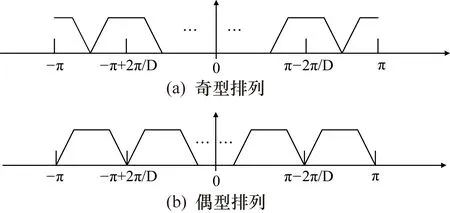

实际滤波器无法做到式(1)的理想截止频率,具有一定的过渡带,为了保证信号无盲区接收,对滤波器组频带进行划分。均匀信道划分的排列方式如图2所示,分为如图 2(a)所示的奇型排列方式和图 2(b)所示的偶型排列方式,两种方式结合可克服由于信号落入相邻信道之间造成的信号衰减,能够消除部分信道盲区的影响[7]。

图2 均匀信道划分的排列方式

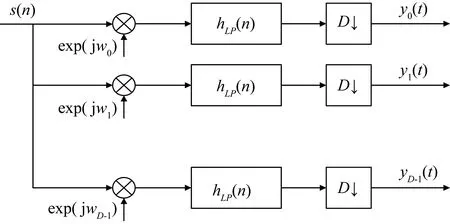

若采用图 1信道化模型,每1个子信道都需要1个高阶的FIR滤波器,会消耗很多资源,现有的逻辑器件无法满足要求。因此,采用如图3所示的等效低通实现形式,通过多相滤波原理[8]和采样率等价变换原理[9]可得到高效实现结构。

图3 信道化低通实现形式

其中,低通滤波器hLP(n)为FIR形式,转移函数为

(2)

式中:N为滤波器阶数,对式(2)做多相式分解,令N=DQ,D为子信道个数,Q为整数,则低通滤波器的多相式为

(3)

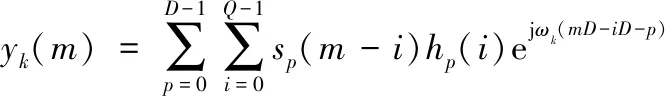

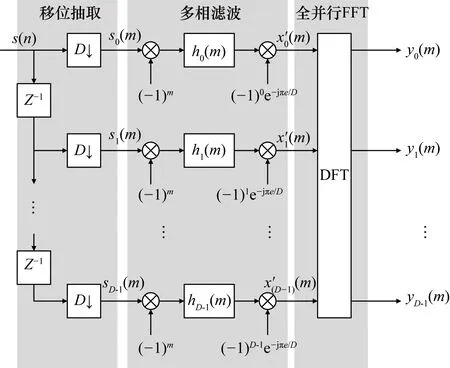

根据采样率等价原理,将滤波器多相分量与抽取操作进行互换,则滤波器的运算量减少为原来的1/D倍。图 3中第k个通道输出yk(m)为

yk(m)={[s(n)ejωkn]×hLP(n)}|n=mD

(4)

定义sp(m)=s(mD-p);hp(m)=hLP(mD+p);则有:

(5)

定义:

(6)

代入上式:

(7)

信道偶型排列时,第k个子信道中心频率为

(8)

代入(6)式得:

xp(m)=[sp(m)(-1)m]×hp(m)

(9)

则偶型排列时第k个子信道yk(m)输出为

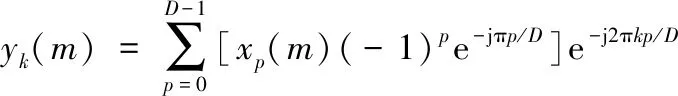

(10)

式中:x′p(m)=xp(m)(-1)pe-jπp/D。

信道奇型排列时,第k个子信道中心频率为

(11)

代入(6)式,得到:

xp(m)=sp(m)×hp(m)

(12)

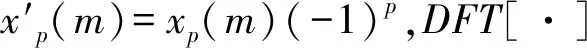

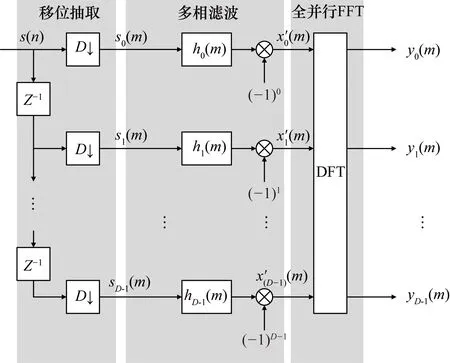

则奇型排列时第k个子信道yk(m)输出为

(13)

由式(10)和式(13)可以看出,采样抽取操作移到滤波运算之前,可显著减小后续处理时的工作时钟频率;同时仅用一个多相分解的滤波器代替了图 3中D个滤波器组,使逻辑资源降低D倍,得到极大优化。因此采用此方式实现的偶型排列和奇型排列数字信道化结构相当高效。

图4为数字信道化偶型排列高效结构, 图5为数字信道化奇型排列高效结构。

2 高效结构FPGA实现

针对数字信道化高效结构基于FPGA芯片特点开展设计,以偶型排列为例进行说明,奇型排列类似。整个高效结构由3个部分组成,分别是移位抽取模块、多相滤波模块和全并行FFT模块。

图4 数字信道化偶型排列高效结构

图5 数字信道化奇型排列高效结构

2.1 移位抽取模块

如图4所示,移位抽取模块主要完成对高速采样数据移位寄存与D倍速降样抽取操作,得到式(5)中的sp(m)数据,作为后续多相滤波模块的输入。其中移位操作由具备存储功能的触发器完成,工作时钟与高速采样时钟同源,工作频率达GHz级别,且D路子信道需要移位存储D次。然后通过降低工作时钟方式,在每一级移位之后完成对采样数据的D倍降样抽取,降样后时钟工作频率为100 MHz级别,该时钟也是后续多相滤波模块和全并行FFT模块的工作时钟。

针对移位抽取模块的FPGA实现,根据文献[10]和文献[11]所述,如果利用FPGA内部的逻辑资源(Fabric),完成GHz级别的采样数据移位存储和跨时钟域的抽样处理,实现较为复杂,资源消耗也较大,因此需研究利用FPGA特定资源完成移位抽取。

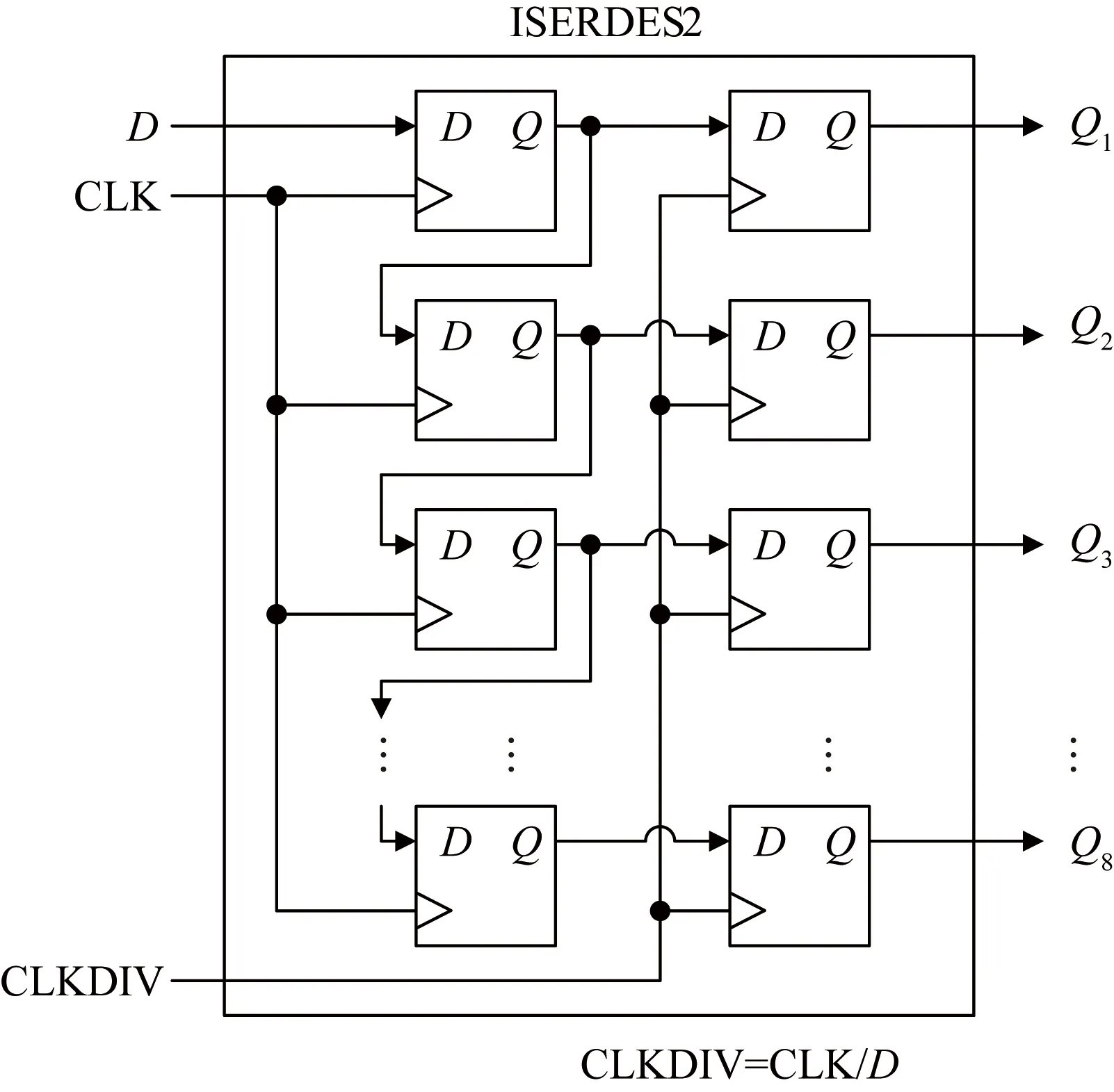

FPGA自带的ISERDES2模块位于其接口单元中,工作频率可高达GHz级别,主要功能是进行串并变换[12]。当配置为单数据速率(SDR)模式时,ISERDES2模块原理框图如图6所示,工作过程是:首先通过高速时钟CLK对高速采样数据进行串行移位寄存,当达到要求的并行宽度后,再利用降样后的CLKDIV时钟输出并行数据。可见ISERDES2模块可实现移位抽取模块功能,工作频率完全满足要求,并且不占用FPGA内部逻辑资源,无需进行复杂的跨时钟域操作。

图6 ISERDES2原理框图

2.2 多相滤波模块

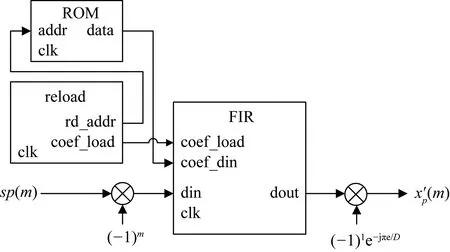

多相滤波模块的首要任务是将高阶的原型FIR滤波器按式(3)分解成D组较低阶的FIR滤波器组,分别对移位抽取模块输入数据做FIR运算,同时对FIR运算之前和运算之后的数据按要求乘以相应的系数。1路多相滤波的实现框图如图7所示,由FIR滤波器模块、滤波器系数存储(ROM)模块和滤波系数加载(reload)模块组成。初始化时reload模块从ROM中取出系数,并顺序写入FIR模块中,完成系数的装载工作。工作时FIR模块则利用系数对输入数据进行乘累加运算,实现相应的滤波操作。

图7 1路多相滤波实现框图

在滤波器阶数的选择上,根据经验公式,原型FIR滤波器阶数与归一化的通带和阻带的关系[13]为

(14)

2.3 全并行FFT模块

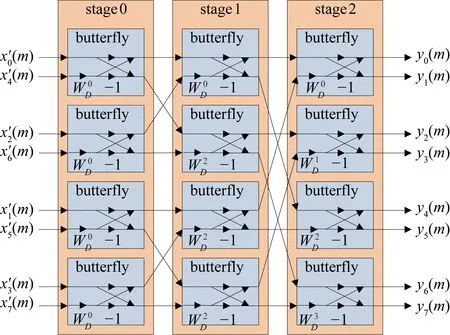

全并行FFT模块的功能是实现式(13)中的离散傅里叶变换。而由式(13)的计算可知,其对运算吞吐率具有较高要求,需要1个时钟周期内完成1次D点的DFT运算,因此要求该模块必须进行全并行运算。目前FPGA提供的FFT IP核不具备全并行模式,其完成D点DFT运算至少需要D个时钟周期[14],无法满足需求,需设计全并行FFT模块。

为了实现全并行运算,采用资源换时间的方法[15],即不但FFT的每一级要并行实现,而且每一级中的蝶形运算单元也要并行实现。对于D为8个子信道的情况,总共需要并行实现3级12个蝶形运算单元,图 8为时间抽取基——2 FFT算法的全并行实现框图。

图8 全并行FFT实现框图

由图 8可以看出,该模块每个时钟周期可同时处理D个数据,只是从数据输入到运算完成需要一定的运算延时,其运算吞吐率完全满足式(10)和式(13)的要求。

3 高效结构仿真

对完成代码编写的数字信道化模块进行仿真,仿真工具为Modelsim,仿真激励产生和仿真响应分析采用的工具为MATLAB。

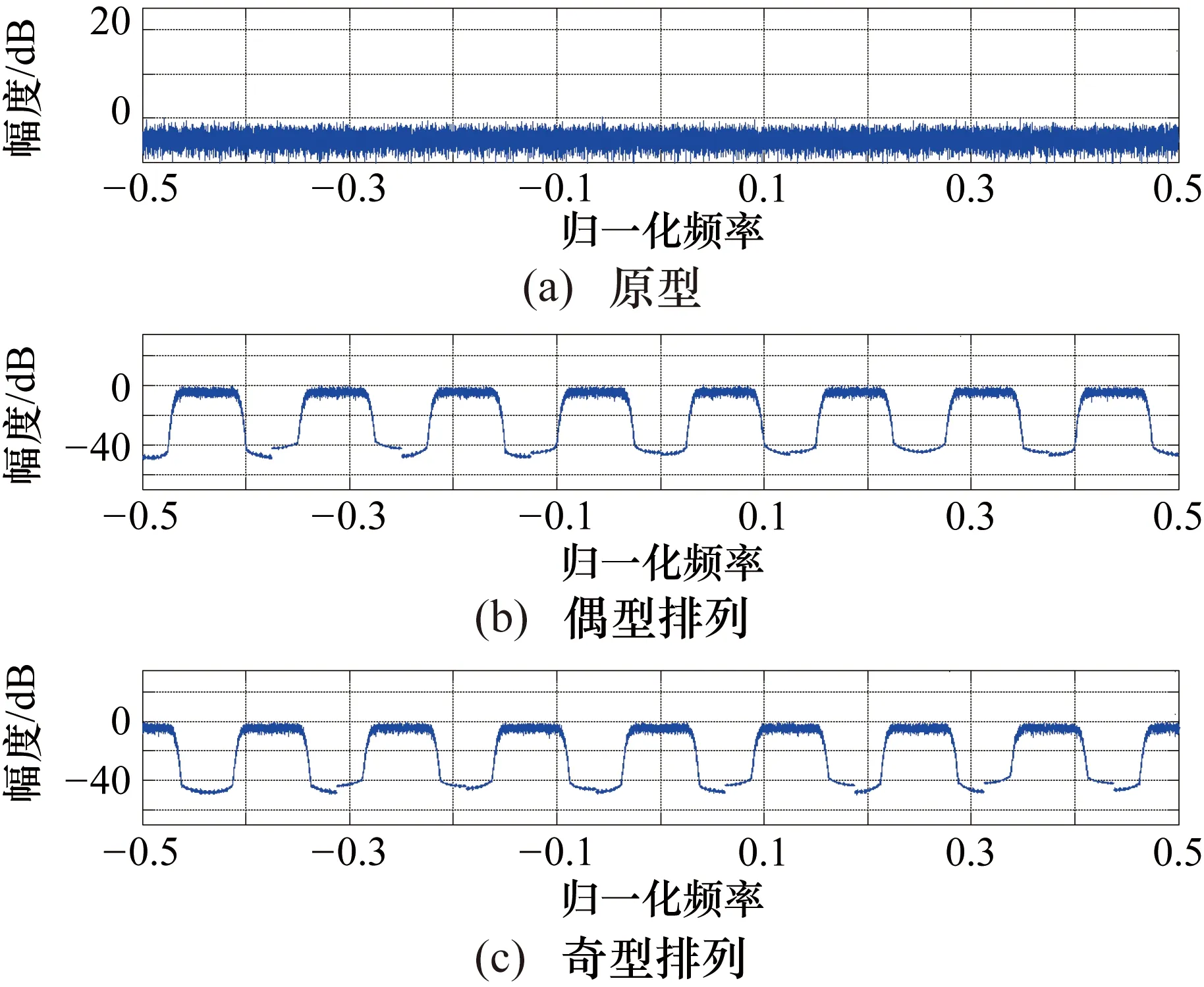

仿真条件1:采样率1.2 GHz,输入激励仅为噪声,无信号输入时奇偶信道幅频响应如图9所示。图中横轴为归一化频率,纵轴为信号幅度,各子信道拼接到一张图上显示。其中,图9(a)为未经过数字信号化处理原始输入信号的幅频响应,图9(b)为经偶型排列时数字信道化处理后的信号幅频响应,图9(c)为经奇型排列时数字信道化处理后的信号幅频响应。由图9可知,各子信道带宽与带外衰减与设计的原型滤波器一致。

图9 无信号输入时奇偶信道幅频响应

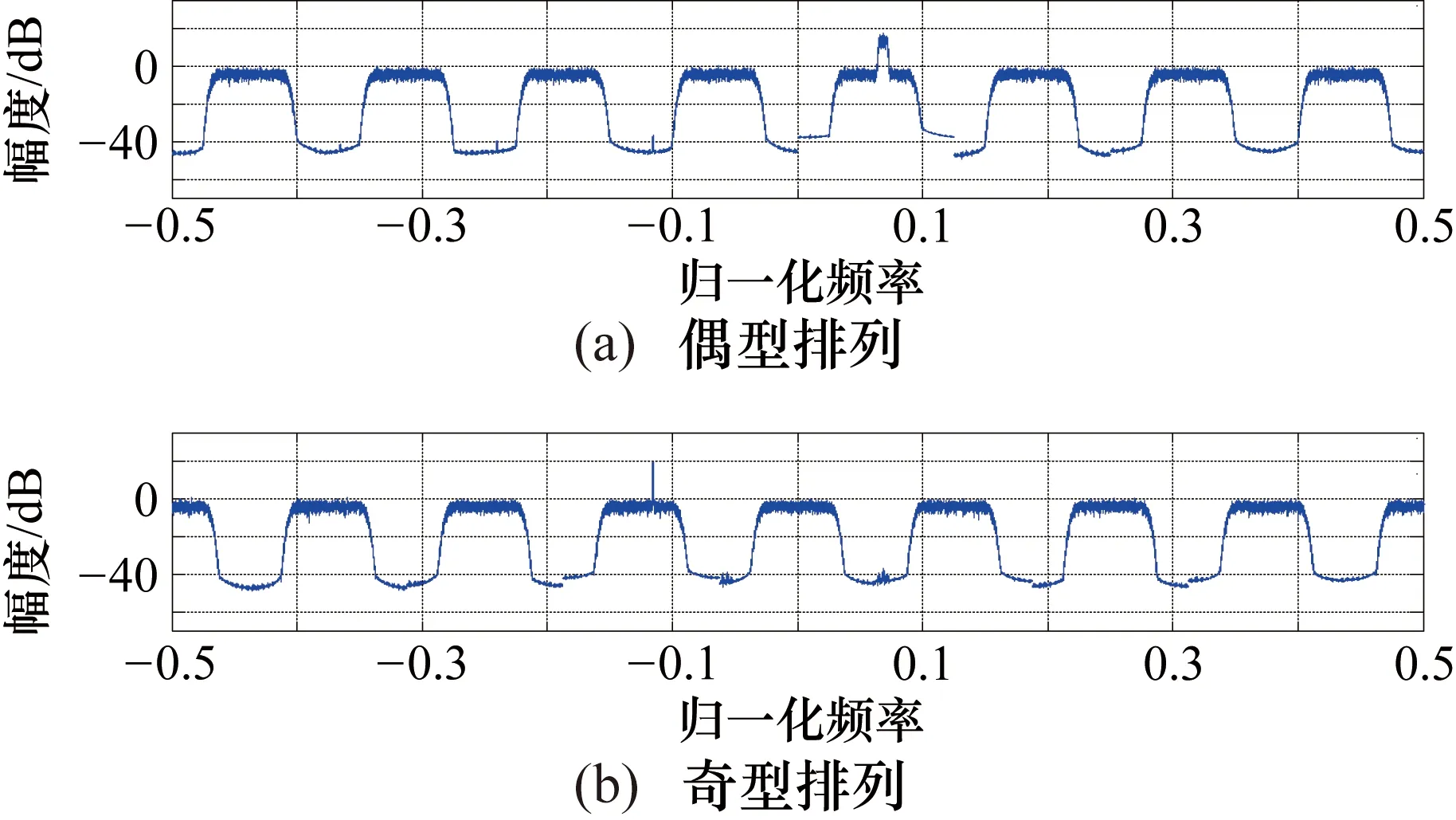

仿真条件2:采样率1.2 GHz,输入激励为噪声+信号,其中信号有2个。信号1的参数为中心频率82 MHz,调制方式QPSK,信息速率10 Mbit/s;信号2的参数为中心频率-13.8 MHz,调制方式BPSK,信息速率1 Mbit/s。2个信号同时输入时奇偶信道幅频响应如图10所示。

图10 2个信号同时输入时奇偶信道幅频响应

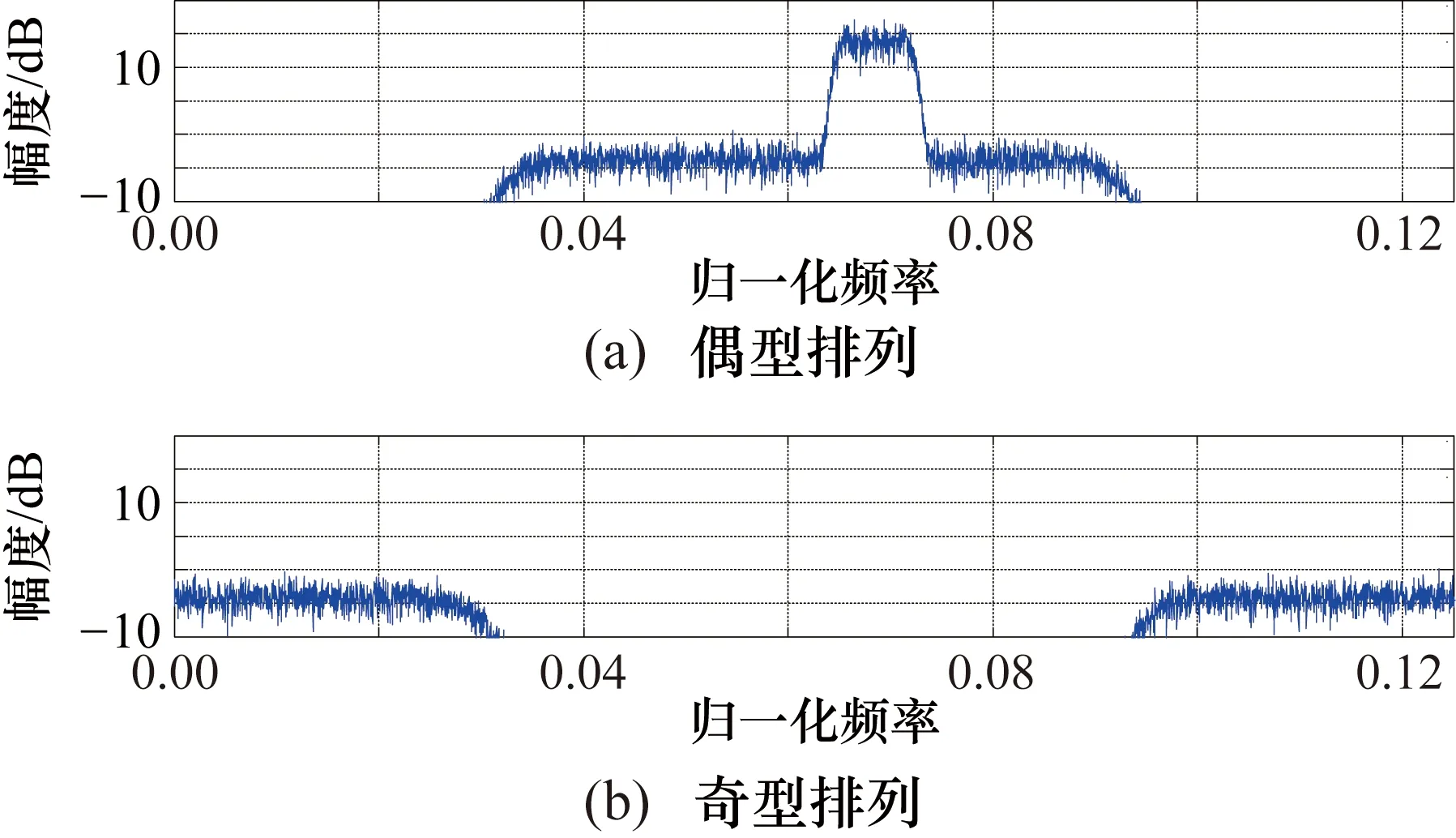

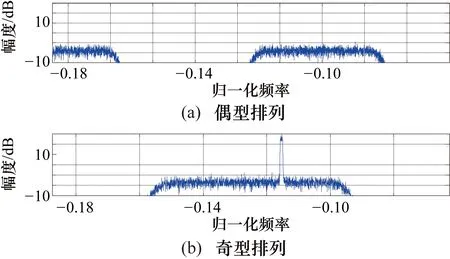

分析可知,信号1应位于偶型排列的第5个子信道,信号2应位于奇型排列的第3个子信道,仿真结果与分析一致。图11和图12分别为第5个子信道和第3个子信道幅频响应细节图。由图11、图12可知,信道化输出可以较好地保留原信号信息,未造成信号失真。

图11 第5个子信道幅频响应

图12 第3个子信道幅频响应

4 结束语

结合工程实际给出了均匀分布数字信道化接收机的高效实现结构,通过设计移位抽取模块、多相滤波模块和全并行FFT模块得到高效结构;并基于FPGA的实现,进行仿真与在线测试,验证了该高效结构功能正确、性能稳定,且资源占用率得到极大优化。该数字信道化接收机已应用于某宽带接收机项目,仅占用全部FPGA逻辑资源约10%,为后续信号处理功能的实现提供了有力支撑,且实测结果与仿真结果一致,性能指标优于用户要求,具有一定的推广价值。