以太网与CAN总线通信的FPGA设计与实现*

潘忠英

(山西工程职业学院,计算机工程系,山西 太原 030009)

0 引言

工业智能化推进过程中,在采集不同设备的数据进行传输时,为了提高传输速率、降低功耗,需选定合适的总线进行信息交互。不同的总线进行信息交互时,由于数据传输格式存在较大的差异,无法直接通讯,因此需要对传输数据进行格式转化。综控机与其他设备互联时,一般采用计算机上特定有限的接口作为通讯方式,CAN 口通讯简单、纠错力度大、抗干扰能力强。当设备连接复杂度程度较高时,综控机需要扩展性更高的接口来实现通讯。以太网传输速率快,能够解决通讯节点增加导致的速率及功耗问题。目前对于CAN总线与以太网之间的通讯设计,一般采用ARM 芯片作为CPU 进行软件设计。但考虑到FPGA 芯片具有开发周期短,编程灵活且成本低的特点,系统选用FPGA芯片作为时序控制核心,实现各个总线的底层协议以及不同协议之间的数据转换交互。

1 系统总体设计

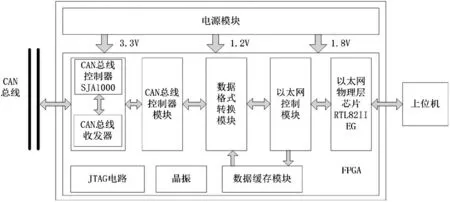

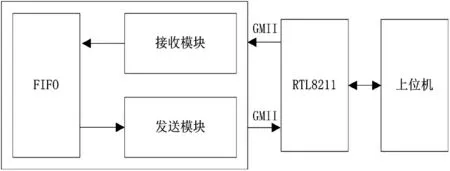

以太网与CAN 总线信息交互的总体设计框图如图1所示。

图1 系统总体设计框图

系统采用复旦微电子生产的国产FPGA 芯片作为逻辑控制核心,型号为FMK50。软件设计由以太网收发模块、CAN 收发模块、数据转换模块等构成。系统上电后,由综控机通过网口发送数据包给FPGA,FPGA 通过以太网控制模块不断查询线上是否有新的数据,为匹配数据传输速率,采用缓存模块对接收到的以太网数据报文进行暂存。FPGA 采用数据转换模块对UDP 报文进行数据提取,并按照CAN 总线通讯协议对数据重新进行打包封装,发送给CAN控制器模块实现数据的发送。为验证设计的正确性,对数据的双向传输均进行测试。通过比较发送端与接收端的数据及数据长度,表明数据双向传输均正确。

2 系统硬件设计

2.1 以太网模块设计

系统采用以太网物理层芯片RTL8211EG 进行网口数据的收发,该芯片传输数据的速率最快可达到1000Mb/s。FPGA 与该芯片在硬件上通过专用接口GMII 进行连接,具体硬件电路图如图2 所示。从图2中可以看出,当FPGA 发送数据给RTL8211EG 芯片时,FPGA作为主设备,依照时序手册提供数据TXD和时钟GTXC给从设备RTL8211EG。软件设计上FPGA主频为50MHz,通过时钟管理模块DCM 倍频出125MHz 作为GTXC,数据传输时按照时钟节拍对数据字节进行采样。

图2 以太网模块电路图

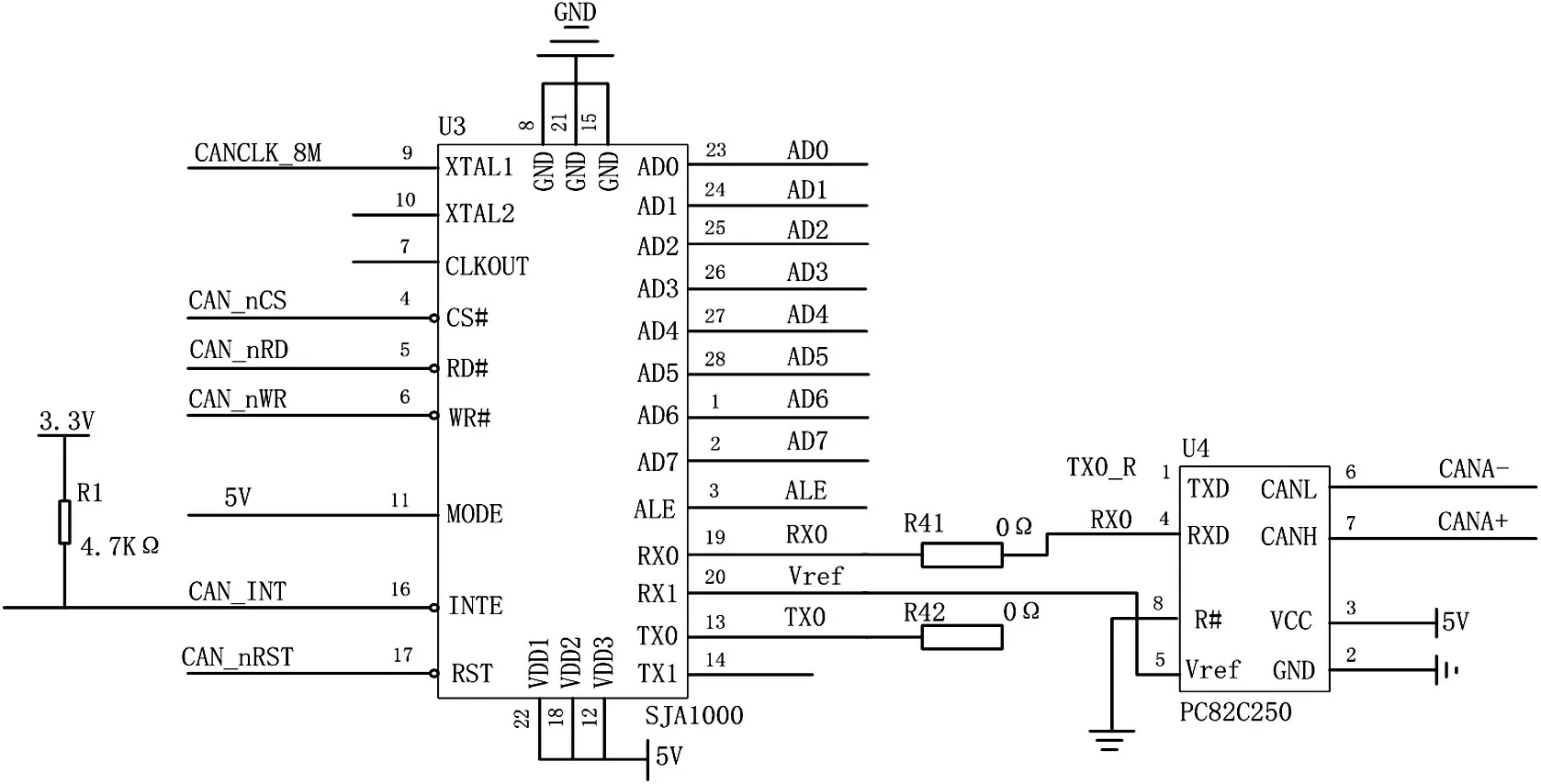

2.2 CAN模块电路设计

系统采用CAN 控制器SJA1000,配合独立CAN收发器实现CAN总线通讯。FPGA输入8MHz的时钟到CAN控制器芯片的XTAL引脚,与内部振荡电路相连。由于CAN 总线由差分电平CANH 和CANL 组成,CAN 控制器输出的数据不能直接与之通信,因此需要CAN 收发器来对数据进行电平转换,实现数据正常稳定的传输。由于FPGA 与CAN 控制器芯片的工作电压不同,两者在进行通讯时需要进行电压的匹配。CAN 模块电路设计图如图3所示,图中CAN 控制器芯片的RX1 引脚与CAN 收发器的Vref 引脚互连,降低数据在CAN控制器与CAN收发器之间的传输延时。

图3 CAN模块电路图

3 系统软件设计

软件方案设计上以国产FPGA 芯片FMK50 作为控制芯片,并在开发环境Vivado 和Procise 中对软件进一步开发。

3.1 CAN模块软件设计

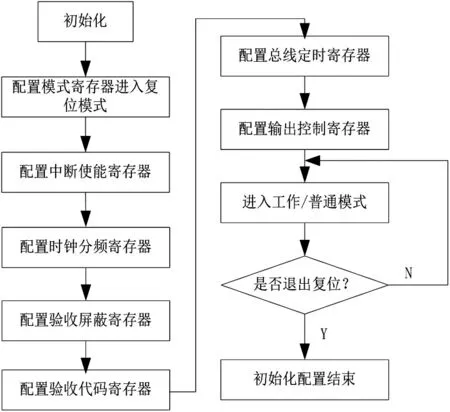

3.1.1 CAN初始化模块设计

FPGA 与CAN 控制器进行信息交互前,需要对其芯片内部的相关寄存器进行配置,由于FPGA 对CAN控制器的配置只能在复位模式下进行,因此系统上电后,软件设计上自动运行CAN 初始化模块,完成对CAN 控制器的寄存器配置后退出复位模式,进入正常工作模式后即可执行读写操作。该模块初始化流程如图4所示。

图4 CAN模块初始化流程

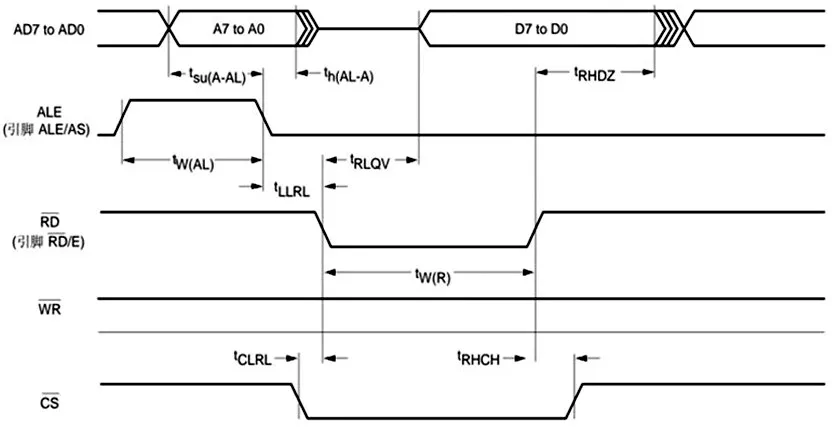

3.1.2 CAN接收模块设计

CAN 模块上电完成初始化后,可根据外部中断标志的沿触发的方式来读取CAN 控制器存中缓器内的数据。FPAG 主要通过8 路数据/地址线AD0-AD7、地址使能线ALE、片选信号/CS、读使能信号/RD、写使能信号/WR 来读取CAN 控制器中接收缓冲器内的13 个字节数据,FPGA读周期时序图如图5所示。

图5 读周期时序图

3.2 以太网模块软件设计

上位机通过网口发送数据至物理层芯片RTL8211,FPGA 内的以太网控制模块通过GMII 总线和该芯片进行信息交互,信息传输格式遵循UDP 协议,具体通信图如图6 所示。以太网模块主要由四部分结构组成,包括负责读取物理层芯片内接收FIFO中数据的接收单元、发送数据至物理层芯片发送FIFO 的发送单元、为匹配数据传输速率而进行数据缓存的缓存单元以及对报文中的数据进行校验的CRC校验单元。

图6 以太网模块和上位机通信图

3.3 UDP数据传输协议

UDP 协议作为网口通讯最常用的协议之一,建立通讯方式简单、传输过程可靠。UDP 发送的数据报中包含通讯双方的端口号,因此数据传输在总线上可依据指定MAC 地址实现正确接收与发送。同时该协议包含CRC 校验,若传输过程中数据受其他因素影响发生错误,通过CRC 模块验证,错误信息可被检测出并丢弃该包数据。UDP 数据包共分为两部分,为数据包头部和数据。其中,数据包头部分由通讯双方MAC地址、数据报长度以及校验和构成。UDP 报文的主要部分如图7所示。

图7 UDP报文构成

4 系统测试与验证

4.1 CAN模块仿真

CAN 控制器SJA1000 与FPGA 通过8 通道并行数据/地址线AD0-AD7 进行交互,当地址使能信号ALS有效时,总线上输出的数据表示地址;当写使能线/WR的电平为低时,总线上的信息为数据。为验证CAN模块软件设计的正确性,编写测试模块,对收发模块中的逻辑设计进行相应的仿真测试。当CAN 接收模块检测到外部中断信号的下降沿时,按照读时序读取SJA1000 中的接收缓冲器的13 个字节,接收完后需要释放接收缓冲器以临时清除中断位,否则将不会响应后续中断信号。接收模块的软件仿真如图8所示。

图8 CAN模块数据接收仿真测试图

4.2 以太网通信测试

为验证以太网模块的正确通信,采用chipscope 对以太网模块数据传输进行在线监测,如图9所示,以太网发送模块对输出数据进行封装,发送数据时首先发送7 个字节的前导码0x55 以及1个字节的帧开始符0xD5、然后6 字节目的MAC 地址28-D2-44-DC-6E-FE、6 个字节源MAC 地址00-0A-35-01-FE-C0以及2字节IP包类型,然后发送数据报及校验和。

图9 chipscope监测图

上位机利用网口数据抓取工具Wireshark 对线上数据进行实时监测,通过该方法可验证上位机与设备通讯连接正确,且通过观察数据验证收发地址及收发个数均正确。从图10 中可以看出,Wireshark 识别到源MAC地址为00-0a-35-01-fe-c0。

图10 网口监测图

4.3 CAN模块数据与以太网数据通信测试

为验证CAN 模块与以太网模块之间的正确通信,通过双向发送不同字节长度的数据,上位机完成数据的存储,通过对比数据长度来作为本次测试的依据。软件设计中CAN 总线传输速率为800Kbps,当以太网传输波特率设置为10Mbps 时,CAN 总线上的数据总能被以太网收到并发送。为匹配两模块的传输速率,不出现丢包的现象,以太网发送数据频率同样采用800Kbps 进行数据通信。如表1 所示,分别为CAN 模块收发的数据长度以及以太网模块收发的数据长度对比,由表可知两模块之间可以实现正确通信。

表1 CAN模块收发的数据长度以及以太网模块收发的数据长度对比

5 结束语

系统利用FPGA 强大的可编程能力,通过对CAN总线以及UDP 数据格式的拆解、提取、封装实现CAN总线与以太网之间的通信。由于两类总线应用领域的不同,且数据传输速率存在较大差距,为实现两者之间的正确通信,需对数据传输速率进行匹配。通过实际测试,降低以太网数据传输频率可达到正常通信,且不发生丢包现象。采用FPGA 芯片使得产品开发周期缩短,并能高效的实现总线间通信。系统满足设计需求,对不同总线间通信具有一定参考意义。