视频实时去雾的硬件优化设计

徐 山,伍世虔

(武汉科技大学信息科学与工程学院,机器人与智能系统研究院,湖北武汉 430000)

0 引言

目前智慧交通、无人驾驶等领域迎来了发展浪潮,对室外场景应用下的机器视觉系统提出了更高的要求。而室外环境中图像质量严重受天气影响,特别是雾、霾和雨等恶劣情况,会造成光线的散射和吸收[1],使得采集的视频流图像质量较差,最终导致高层视觉处理任务的精度下降。针对这些问题,本文对视频流雾天图像清晰化处理进行深入研究。

早在20世纪初,就有学者对雾天图像清晰化算法进行研究;理论研究发展至今,衍生出了基于图像增强、物理模型恢复和神经网络等3类去雾算法,如局部直方图增强算法[2],暗通道先验算法[3]和多尺度增强去雾网络[4]等。虽然这些算法在单幅雾天图像恢复的细节、色彩和可视性等方面有着较好的效果,但其时间和空间复杂度较高,在无人驾驶等嵌入式应用中就会导致成本高、实时性不足、灵活性低和功耗大等问题。

为了在保持去雾效果的同时解决上述应用中存在的问题,部分学者转向了硬件加速的去雾算法研究。文献[5]采用FPGA实现了高效的图像去雾,但它所提出的硬件架构时间复杂度较高,帧间依赖性较高,导致其灵活性较低,资源利用率低,存在较大的优化空间;文献[6]通过设计特定的硬件架构,使其在处理较低图像分辨率时,可以达到极高的实时性,但该架构的处理速度和效果会随着分辨率的增加而减少。

本文综合考虑时间、空间和硬件架构的复杂度关系,提出了一种硬件优化的视频图像去雾架构。该架构对环境光值和大气光值的计算方式进行硬件优化设计,通过简化算法和优化硬件架构,从而降低了计算复杂度,在保证去雾效果的同时,又能提高处理速度。

1 去雾算法及实现

1.1 雾天图像退化物理模型

通过对雾天图像退化的根本原因进行研究,文献[7]提出了大气物理散射模型,其表达式为

I(x)=J(x)e-rd(x)+A[1-e-rd(x)]

(1)

式中:x为图像像素的坐标位置;I为雾天退化图像;J为未退化的无雾图像;A为大气光值;r为大气散射系数;d为景物深度。

该模型解释了雾天图像失真是由场景光线的衰减和环境光的叠加造成的,为了简化模型,一般记为[8]

t(x)=e-rd(x)

(2)

L(x)=A[1-t(x)]

(3)

式中:t(x)为透射率;L(x)为环境光值,与景物深度有着相似的变化趋势。

将式(2)和式(3)带入式(1)可得

(4)

此时对无雾图像的求解过程,变成对环境光L(x)和大气光值A的求解。

1.2 简化的算法设计

根据暗通道先验知识可知,绝大多数无雾彩色图像的RGB三通道内至少有一个通道值无限趋近于零,其数学表达式为

(5)

式中:Ω(x)为以x为中心的像素窗口;Jo为无雾的彩色图像;Idark为无雾图像的暗通道数据。

将式(5)与式(3)结合得

(6)

(7)

根据文献[9]采用均值滤波近似估计透射率,并增设偏移项来弥补误差的方法,可以得到简化的透射率计算公式[9]为

(8)

式中:α为可调节参数,用于平衡图像亮度和去雾效果;mave为所有暗通道数据的平均值;Mave为暗通道值均值滤波后的数据。

联合式(3)、式(6)和式(8),可得简化的环境光值计算公式为

L(x)=min[αmaveMave(x),Jdark(x)]

(9)

因为均值滤波属于线性滤波器,它使得输出的环境光值与输入的暗通道数据有着唯一且确定的传递函数,所以保证了L(x)与d变化的一致性。

本文采用原图像像素最大值和暗通道数据最大值的均值来估计大气光值A。考虑到实际室外场景应用中,彩色图像通道值的最大值多数情况都为255(像素为24位RGB),所以大气光值的简化计算公式为

(10)

通过式(9)和式(10)即可完成对环境光值和大气光值的估计,再将其带入到式(4)中即可得到恢复的无雾图像。

2 去雾算法的硬件优化设计

2.1 算法整体结构概述

算法架构被分为环境光值估计模块、大气光值估计模块和图像恢复模块。通过对算法设计的公式分析,发现其主要的计算步骤有:求最小值、求最大值、均值滤波、求全局平均值和乘除运算等操作,且这些操作中有着许多相似的计算过程,例如:求最大最小值都是对数据进行排序;求平均值和均值滤波都有对数据累加的过程。所以在硬件架构设计时,可以将其合并到同一电路模块中进行优化,即减少了架构的空间复杂度,又减少了不必要的时钟开销。

图1 去雾算法整体硬件架构图

图1将整个架构按功能拆分成排序滤波模块、均值模块、求全局最大值模块以及计算公式模块。该架构工作时呈流水线式,即图像数据在输入的同时就已完成对上一刻数据的处理,不需要先存储再处理,减少了FPGA内部处理模块与外部存储设备之间的数据交互,具有较低的时延[10]。图1中的箭头方向代表着像素数据的流向,每个模块都由同一个本地时钟进行全局驱动同步运行;当一帧像素数据在像素时钟的驱动下输入时,所有模块并行工作完成对数据的处理。

2.2 排序滤波器模块的硬件优化设计

2.2.1 并行全比较器结构

环境光值和大气光值计算模块的输入数据,都是对原始图像像素进行非线性滤波得到的,但前者以最小值为输出目标,后者以最大值为输出目标。不同于常用的排序算法,比如冒泡排序法、希尔排序法和计数排序法等,本文采用时间复杂度最低的并行全比较排序算法[11]。该算法将所有数据在同一时刻进行相互比较,并将比较结果进行累加,则累加和的排序顺序即为数据的大小顺序。因此,该算法仅在一个时钟内即可完成所有数据的排序工作。且FPGA本身就是并行运行的,使用并行全比较算法十分符合FPGA硬件设计原则。以3个数据为例,其硬件架构如图2所示。

图2 并行全比较器电路架构图

对数据0、数据1和数据2进行时序对齐后,在一个时钟内得到所有数据相互之间的比较结果c(x,y),其中x为当前数据序号,y为其他数据的序号;接着将每个数据的比较结果进行累加赋给sum并存入寄存器中,在下一个时钟将其与设定的输出序列号进行比较,从而输出所需的最大值、中值或最小值。由于流水线式的设计导致数据具有易失性,所以需要对输入的数据进行缓存用于输出。

为了保证具有唯一性,做出以下规定:

(1)数据0大于数据1或数据2时,结果记为1,小于或等于时记为0;

(2)数据1大于等于数据2时,结果记为1,小于时记为0。

依据该规则,使得不同时刻数据的优先级不同,即使存在相同的数据,不同数据的比较结果之和也具有唯一性。

该电路架构在FPGA中体现的是以面积换速度的思想方式,即综合考虑资源和速度的关系,在可接受范围内消耗少量额外的资源来换取速度的提升。

sigma^2 estimated as 11186: log likelihood = -6660.35,aic = 13340.6 9

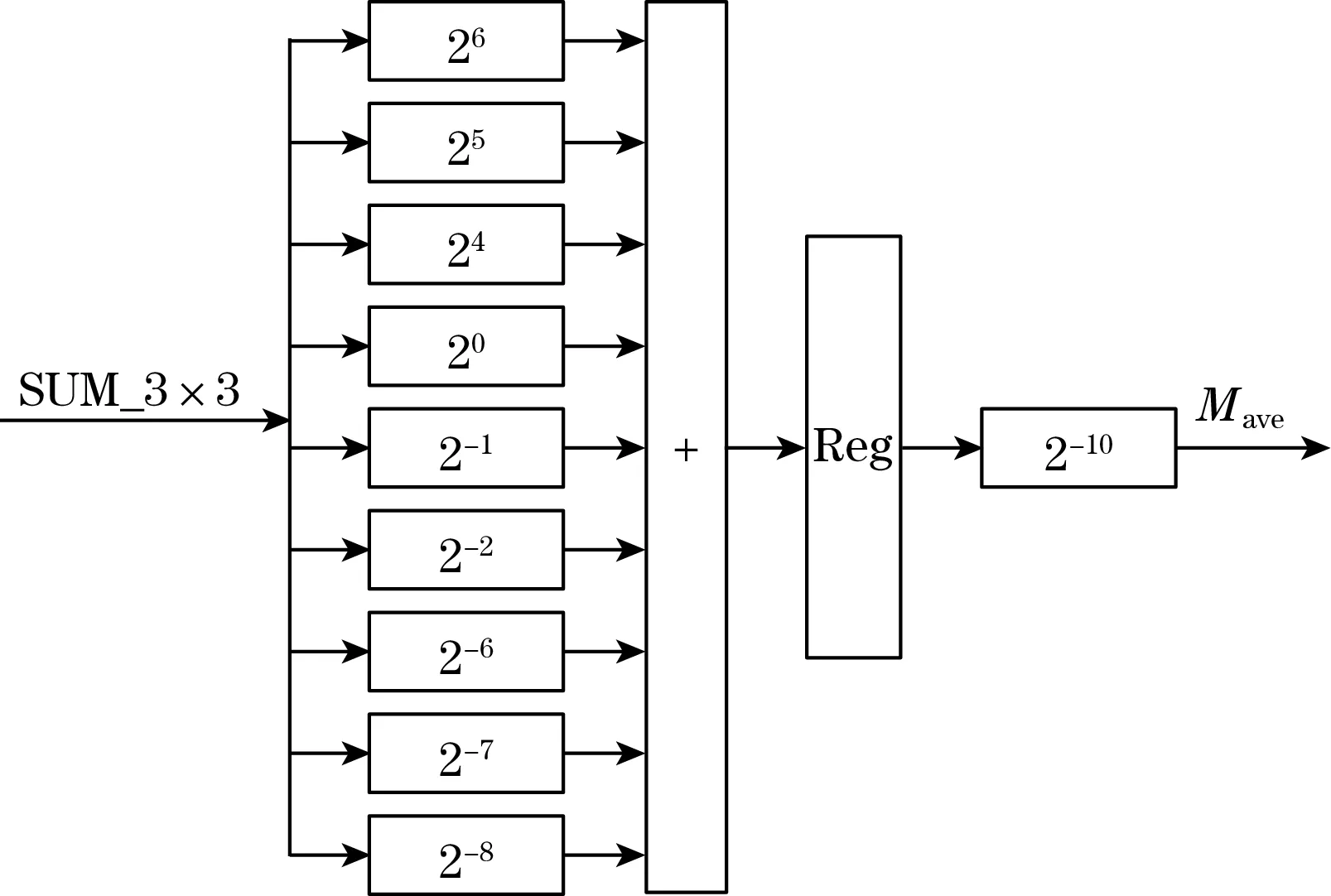

2.2.2 二维快速统计排序滤波模块设计

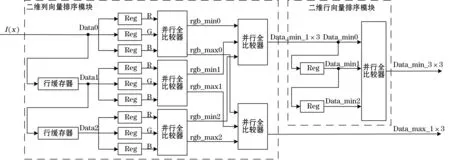

由式(7)可知,暗通道数据求取的是以x为半径的窗口中所有像素的RGB三通道的最小值,结合前文所述的并行全比较器电路和设计思路,以3×3大小的窗口为例,设计了如图3所示的硬件优化的二维快速统计排序滤波器。

图3 二维快速统计排序滤波器架构图

图3中,原始图像数据I(x)通过行缓存器实现串行转并行,并完成数据时序对齐,形成n×3行数据。数据对齐后进行3个通道值的并行全比较,值得注意的是此时的数据已失去时间的特性,不满足本文2.2.1节中所制定的规则(1)和(2),针对该情况做出以下补充:

(1)R通道的值大于等于B通道或G通道的值时,结果记为1,小于时记为0;

(2)G通道的值大于等于B通道的值时,结果记为1,小于时记为0。

该电路共用6个时钟完成对窗口内像素的暗通道值求取。第1个时钟完成对3行1列数据的RGB三通道值的拆分;第2个时钟完成对每个像素RGB三通道值的最小值和最大值的求取;第3个时钟完成对3行1列像素数据三通道值的最小值的求取,并将第2个时钟求取的最大值输出到下个模块;接着采用增量更新的方式,在第4、5个时钟对计算得到的最小值延时2拍,形成3列1行的最小值数据,从而形成窗口数据的形式;第6个时钟完成对3列1行数据最小值的求取,即暗通道数据的求取。所以随着像素半径的增加,该架构的时钟开销并不会增加,即从数据的输入到处理结果的输出时延仅为6个时钟。

2.3 环境光值计算模块的硬件优化

2.3.1 均值模块

均值模块是环境光值计算模块中最重要的一环,其主要功能包括对暗通道数据的均值滤波和求所有数据平均值。依据2.1节中的设计思路和方法,该模块主体电路由均值滤波器窗口大小决定,所以首先采用行缓存器和增量更新的方式完成对n×n窗口数据的求和,然后经由不同逻辑电路得到均值滤波输出数据和平均值输出数据。这里以3×3的均值滤波器为例,设计了如图4所示的均值模块硬件电路。

图4 均值模块电路架构图

图4中串行的暗通道数据(Idark)经由2个行缓存器变成3行并行数据结构,完成数据的开窗以及对齐;在同一时钟的驱动下,该电路先完成排在首列3个数据的相加并赋值给寄存器(Reg),之后在每个时钟到来时完成数据的更新和相加;相加后的数据再经由另外2个寄存器延时2拍后,形成3个列向量和并相加,从而完成3×3窗口数据的相加;最后经由除法电路得到均值Mave。

与均值滤波不同,平均值的求取会受增量更新影响,对数据进行重复性累加,从而造成输出误差。因此需要对平均值累加进行逻辑判断:当场信号(vsync)无效时,可以判断一帧图像数据已完成求和,此时除法电路的数据之和才有效,否则为0。

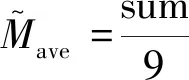

在进行除法运算的映射时,常见的方式是调用除法器IP核,但这样会消耗更多的逻辑资源或更稀少的计算单元。由算法原理可知,均值滤波算子窗口大小以及像素总个数是确定的,所以该除法电路可以被视为定常数除法。综合考虑系统架构逻辑资源占用率、最高工作时钟频率和计算精度之间的平衡,本文采用定常数转换的思想,将除法电路中的定常数除法转换为FPGA所擅长的移位和加法运算,从而降低系统的时间复杂度和资源的占用率。

这里以窗口的均值滤波除法电路为例,其除法运算的定常数为9,采用泰勒近似的方式完成定常数转换,即

(11)

在工程应用中,当量化的误差小于最小精度的一半时,可称为无损误差。其误差为

(12)

根据上述思想,设计了如图5所示的均值滤波器除法电路。数据(sum_3×3)输入到除法电路后,经由多个移位操作同时处理后相加赋值给寄存器,将相加结果延时一个时钟周期防止出现冒险与竞争,然后再进行左移操作来完成整个除法动作。该电路仅消耗1个加法器和1个寄存器,又因为在FPGA中移位操作不消耗时钟周期,所以该电路仅开销1个时钟。求平均值的除法电路与上述设计思想相同。

图5 均值滤波器除法电路架构图

2.3.2 环境光值计算模块

由式(9)可知环境光值的计算原理,为了避免进行冗余的计算,可以将设定的偏移值α放大2n倍,然后进行定常数转换来避免进行浮点运算,进而使用无时钟消耗的移位运算。

考虑到本文是基于视频流的处理,帧间具有相似性[12],且在帧率较高的情况下图像的变化较慢。所以本文采用上一帧的计算参数来处理当前帧的图像,计算结果可能存在一定的误差,但极大地减少了资源的消耗,从而降低该架构的空间复杂度,提高了算法的运行速度。

3 实验结果与分析

3.1 去雾效果比较与分析

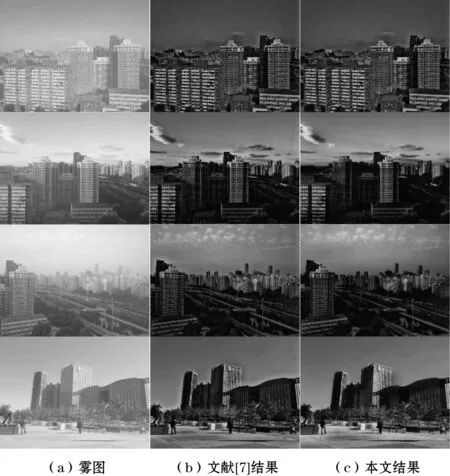

图6显示了文献[7]和本文硬件去雾的处理结果。本文所提出的架构虽然对许多步骤进行了硬件优化,但从主观上来看,两者视觉效果相当。

图6 去雾效果比较

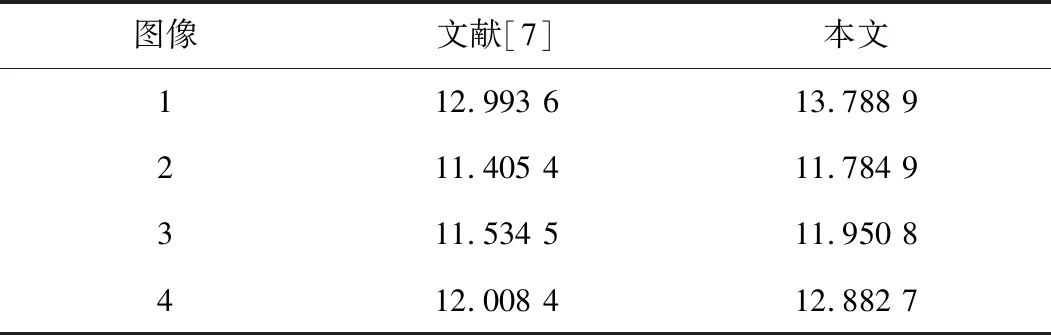

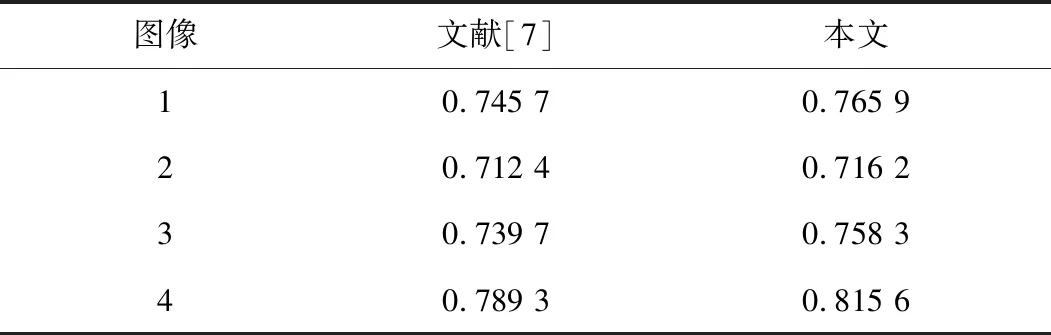

为了客观地评价实验结果,本文选择峰值信噪比[13](peak signal to noise ratio,PSNR)和结构相似性[14](structural similarity,SSIM)来作为评价标准。PSNR是基于误差敏感的图像客观评价标准,其值越大,则处理后图像失真越小;SSIM是衡量2幅图像相似度的指标,其值越大,则处理后的图像与原图结构越相似。具体客观评价指标结果如表1和表2所示。

表1 客观评价指标PSNR结果

表2 客观评价指标SSIM结果

从表1和表2数据可以看出,本文从算法原理上进行简化并没有减损去雾效果质量,与文献[7]中的算法处理效果相当。

3.2 运行速度比较

由于本文硬件架构是受文献[7]的启发而提出,且文献[15]是将文献[7]中的算法用FPGA进行的硬件实现,所以这里选取文献[7]和文献[15]进行去雾处理速度的对比。

表3中的数据来源于文献[7]和文献[15]原文。文献[7]通过Matlab7.11得到,运行环境为:2.33 GHz的IntelCore2(Q8200)CPU;文献[15]运行在cyclone Ⅳ系列的EP4CE10F17芯片开发板上;本文硬件去雾架构运行平台与文献[15]相同,但运行速度是文献[7]的约11倍,是文献[15]的约2倍。

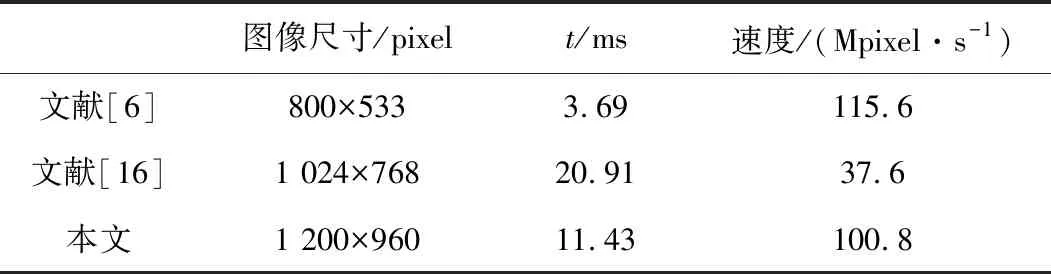

表3 算法运行时间比较 ms

表4为不同硬件加速方案的比较,可以看到本文所提架构的数据处理速度高达100.8 Mpixel/s,是文献[16]的3倍,与文献[6]相当,对1 200×960 pixel的视频图像去雾处理可以以60 fps的速度稳定运行。且通过软件分析可知,该架构实现的功耗为2.14 W。

表4 不同加速方案比较

4 结束语

本文将去雾算法进行简化,提出了一种视频流的实时去雾硬件架构。该架构具有低功耗、结构简单、实时性高和计算复杂度低等优点,在全局时钟的驱动下工作,呈流水线式。采用硬件优化的方法简化FPGA中环境光值和大气光值的计算步骤,降低了算法的计算复杂度,增加了硬件资源的重复利用率,提高了硬件架构的处理速度。各模块架构经功能性验证后,在Cyclone Ⅳ系列的EP4CE10F17芯片上进行实验,实验结果表明本文设计的硬件架构在保证去雾效果的同时,完全可以满足当前工业应用的要求,具有较高的应用价值。