基于Zynq的多通道涡流无损检测系统

蒋青松,张志杰

(中北大学 仪器科学与动态测试教育部重点实验室,太原 030051)

涡流检测技术是工业领域使用最广泛的无损检测技术之一[1-4],也是探测导电元件表层缺陷最合适的方法,对高速轨道,航空发动机叶片,飞机铆接件,油气管道,核电站蒸汽发生器等的在役检测都可取得很好的检测效果[5-9]。此外涡流检测也大量应用于复合材料的检测。

Xilinx公司的Zynq7000 系列产品为第一代可扩展处理平台,是一种可编程片上系统[10-11]。Zynq-7020芯片内部集成了FPGA(现场可编程逻辑门阵列)和ARM处理器资源,使其拥有了FPGA的硬件可编程性和ARM的软件可编程性,具有较高的稳定性和灵活性[12-14],可以对感应信号进行实时处理和计算,未来也可以提高系统的扩展性。

1 无损检测算法

1.1 数字相敏检波算法

数字相敏检波算法的核心是利用加减乘除基本运算实现复杂的数学运算,假设激励线圈的电压信号为Uj,幅值为UA,感应线圈的电压信号为Ug,幅值为UB。由于数模转换芯片利用DDS(直接数字式频率合成器)结构输出正弦波给激励线圈,所以感应线圈的信号是同频率正弦波,二者可表示为

Uj=UAcos(ωt)

(1)

Ug=UBcos(ωt+θ)

(2)

二者相乘可得到

(3)

式中:ω为角频率;t为信号时间;θ为感应信号与激励信号的相位差。

式(3)中cos(2ωt+θ)是一个周期和为0的高频分量,如果不用数字滤波器将其滤除,将消耗大量FPGA部分的片内资源,不利于系统未来的扩展,因此利用这个特性可以通过周期累加的方式滤掉高频分量,最终得到有效值电压值Uiy,即

(4)

将激励线圈的电压信号相位偏移90°,得到Uj90,即

Uj90=UAcos(ωt+90°)=UAsin(ωt)

(5)

将Uj90和模数转换芯片接收的信号Ug相乘,可得Ui90为

Ui90=Uj90×Ug=UAsin(ωt)×UBcos(ωt+θ)=

(6)

同样利用累加周期和为0去掉高频分量得到有效电压值Ui90y为

(7)

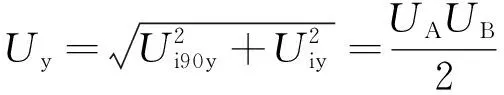

阻抗分解如图1所示,可由信号的实部I和虚部Q推出幅值和相位。实部和虚部也可以由幅值和相位进行正交分解得到。数字相敏检波算法就是利用实部和虚部计算出幅值和相位的。

图1 阻抗分解示意

复阻抗的实部是电阻分量,虚部是电抗分量,通过实部和虚部就可以推断出阻抗的变化情况。感应线圈的阻抗受多种因素影响,利用控制变量法可对各因素进行分析。

对Ui90y和Uiy各进行平方后求平方根得Uy。

(8)

相位θ可以通过反正切函数求得。

(9)

1.2 坐标旋转数字计算机算法

坐标旋转数字计算机算法(CORDIC)是针对FPGA在数字信号处理应用中计算三角函数相关的算法。FPGA利用坐标旋转数字计算机算法(CORDIC)可以计算均方根和反正切。

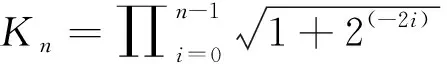

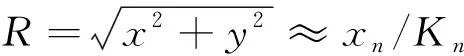

CORDIC算法的向量幅度计算应用了QR算法,要求输入的向量进行吉文斯旋转,初始向量(x,y)经过n次旋转后得到向量(xn,yn)的期望如下

(10)

yn→0

(11)

式中:Kn的值受迭代次数影响,迭代次数会影响CORDIC算法的精度。

x,y的迭代式为

(12)

xi+1=xi-di(2-iyi)

(13)

yi+1=yi+di(2-ixi)

(14)

(15)

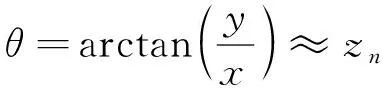

CORDIC算法计算相角的公式为

zi+1=zi-diarctan(2-i)

(16)

(17)

式中:Kn为伸缩因子;i,n均表示旋转次数;di用以表示不同的旋转方向;di=±1;zi为相位累加器。

该系统AD模数转换芯片的数据位宽达14位,在此基础上进行算法处理,数据位数只会大于14位,因此算法精度不会影响系统的算法精度。

2 硬件系统

AD 9240芯片输出数字量为14位,采样率为10 MSPS,为单电源模拟电压供电,AVDD引脚采用5 V电源供电,数字引脚DVDD为3.3 V电压供电,其中AD 9240的输入范围是2 V的基准电压,通过将SENSE引脚与REFCOM引脚连接在一起,VREF引脚就能提供2.5 V的基准电压。由于AD 9240只能采集正电压信号,通过将VREF引脚连接到VINA和VINB引脚,可以得到一个2.5 V的偏置电压,这样采集信号为-2.5 V~2.5 V。

AD 9240需要一个CLOCK时钟信号,这个时钟的最小周期为100 ns,在FPGA部分提供时钟信号后,AD 9240可以在数字端输出14个数字信号,幅值由DVDD引脚的电源输入确定,用AD 620作为信号采集的仪表运放,提供高共模抑制比并将模拟信号传输给AD 9240。

受激励频率影响,线圈的感抗会发生变化,无法确保AD 9240芯片接收到的信号一直处于-2.5 V~2.5 V之间,因此选用THS7001作为程控增益运放,其具有-22 dB~20 dB的增益范围。AD 9767输入为14位数字信号,采样率为125 MSPS,具有2通道高速数模转换芯片,其中AVDD引脚用5 V电源供电,DVDD的引脚的供电需要根据数字信号的幅值进行确定。由于FPGA部分的LVCMOS33或LVTTL最大能提供的电压只有3.3 V,而数字信号的输出高电平与DVDD引脚的电压一致,因此DVDD的电源输入不应选用3.3 V以上的电源。

AD 9767输出引脚接电阻再接地,将电流转化为电压后接AD 8066运放,可以将差分电压信号变为单端电压信号,以给激励线圈提供激励信号,AD 9767需提供一个时钟信号和一个输入写信号,写信号可以提前于时钟信号或与时钟信号一致,用于触发AD 9767的转换过程。

由于用到了高速率并行的AD和DA转换,所以极大地增加了所用的Zynq核心板的引脚数量。多引脚连接件如图2所示,由于多引脚连接件的存在,高频信号的走线距离变长,且信号大多平行。这会干扰高频信号引入串扰,因此为提高系统的稳定性,选用74ALVC162244缓冲器,74ALVC162244缓冲器有16个通道,当输入电压为3.3 V时,缓冲器可以将输入高电平提升到约3.3 V,相当于提高了信号的负载能力,加强了系统抵抗电磁干扰的能力,增加了系统的稳定性。

图2 多引脚连接件

采用Altium Designer软件设计硬件的原理图和PCB图,考虑到布线和噪声的影响以及成本控制,PCB设计采用四层布局。

3 仿真验证

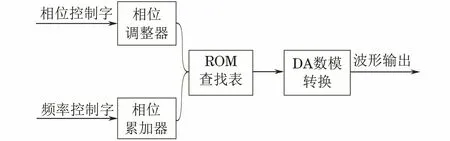

利用直接数字式频率合成器可以将所需要的数字量存储到ROM(只读存储器)中,ROM再将存储的数字量发送到DA中,完成波形的输出。DDS程序框图如图3所示。DDS输出波形如图4所示。

图3 DDS程序框图

图4 DDS输出波形

仿真验证数字相敏检波算法的正确性,使得AD输入和DA输出一致,计算相角和幅值。

AD 9767是14位输入,因此输出也设定为14位,将无符号14位数字量转化为有符号14位数字量得到信号da_data,设采集信号ad_data的数字量幅值和相位与da_data的一致,经计算得阻抗实部为33554432。由于移位会导致精度下降,因此得到的实际阻抗实部为33540267。

用实部和虚部赋值到CORDIC算法中,得到相位的计算量约为0 rad,试验结果符合验证规律。

4 涡流检测系统试验分析

利用所构建的涡流无损检测系统,用信号发生器作为标准信号源代替感应线圈的感应信号,检验设计的硬件系统输出激励和接收感应信号的能力以及数字相敏检波算法的正确性。整个系统包括信号发生器、电源、示波器、Zynq核心板、采集系统板等模块。检测系统试验平台如图5所示。利用逻辑分析仪抓取信号发生器与DA输出信号进行相位计算并与数值相敏检波算法计算的相位进行对照。

图5 检测系统试验平台

AD 9767输出的信号周期接近120 μs,Zynq-7020中的FPGA部分设定了一个计数器(数值为6)用于降低时钟频率,而系统时钟频率为50 MHz,一个频率需要输出1 024个点,因此波形验证无误。根据使能开关的信号就可自由选取激励通道。

通过信号发生器给任意一个通道施加激励,选定接收通道后,用逻辑分析仪抓取AD采样信号和DA激励信号,计算出信号的相位差,与算法实际输出的相位差进行比较。

经过数字相敏检波算法处理后得到的相位为50°,即采集的输入信号与DA激励输出的信号相位差约为50°。

相位可以描述实部和虚部之间的比例,相位的正确性即验证了实部和虚部间的比例计算是正确的,即在金属表面缺陷试验中,该系统可以正确表现感应信号的实部或虚部的变化规律。

5 结语

介绍了基于Zynq的多通道涡流无损检测系统的设计过程,利用Zynq的FPGA部分进行算法设计,捕捉涡流无损检测系统板的通道数据。将试验结果与逻辑分析仪得到的图形进行对照,发现数值相敏检波算法计算的相位值是正确的。

设计的多通道涡流无损检测系统可以对激励线圈进行信号激励,并采集感应线圈的微小信号进行放大,激励通道和感应通道可以更改,而采集到的线圈电压被分解成幅值、相位、实部和虚部值,通过实部或虚部的变化可以对线圈复阻抗的变化予以量化显示。