P-L波段多通道数字收发组件设计

王 轶,季 帅

P-L波段多通道数字收发组件设计

王 轶,季 帅

(中国电子科技集团公司第二十研究所,西安 710068)

通过P-L波段数字T/R组件的研制,实现了DC-2000 MHz频率范围内任意波形信号的射频直接产生和射频直接采样,并通过JESD204B协议和同步时钟驱动的设计,实现了多数字通道间的收发同步,最终通过上位机软件实现对多数字收发通道的波形、频率、相位等参数的实时控制。

L波段;数字T/R;射频直接产生和采样

0 引言

随着高速模数转换器(Analog Digital Converter,ADC)、直接数字合成(Direct Digital Synthesizer Digital Analog Converter,DDS+D/A)以及高速FPGA等器件的发展,加速了相控阵雷达的数字收发系统的进步。收发系统经过数字化后,雷达与计算机联系紧密,收发的数据更易于处理。收发系统的发展越来越向软件无线电发展,即在一个具有开放性、标准化、模块化的通用平台上,将雷达功能(如频率、相位和波形等)由软件来完成,并使高速A/D转换器和D/A尽可能地靠近射频前端以至天线,使得雷达的输入、输出都是软件可定义的。

本文通过DC-2000 MHz数字T/R组件的研制,实现了任意波形信号的射频直接产生和射频直接采样,并通过解决多数字收发通道工作时钟、系统参考信号和数据传输的同步问题,实现了板间的收发同步,最终通过上位机软件实现对多数字收发通道的波形、频率、相位等参数的实时控制。

1 数字收发组件设计

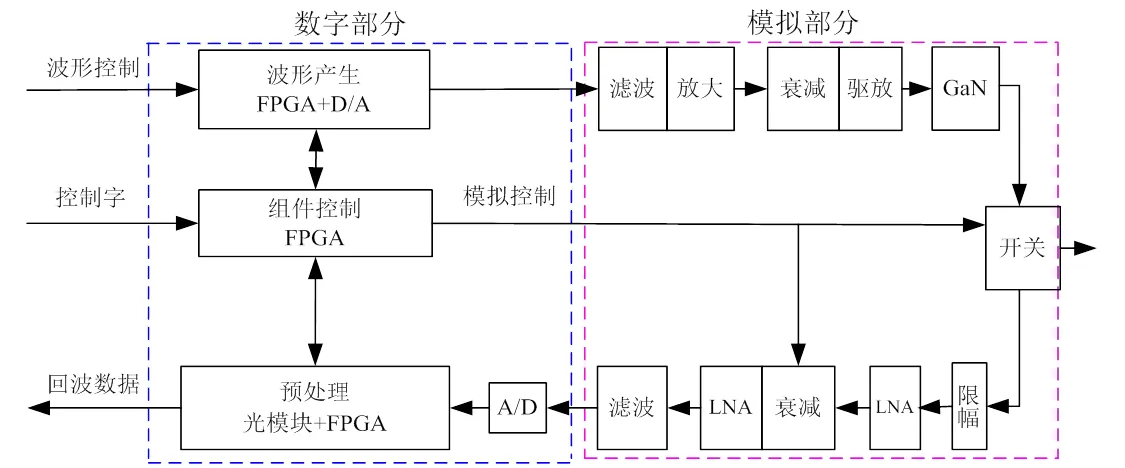

P-L波段T/R组件由数字组件和射频组件两大部分组成。射频组件部分完成发射信号的放大和回波信号的低噪声放大;数字组件部分完成发射激励信号的任意波形产生和回波信号的射频直接采样。

模拟模块划分成射频电路、控制电路、电源三个部分,其电路原理图如图1所示。其中射频电路主要完成发射信号的高功率放大过程和回波信号的低噪声放大接收过程;控制电路主要为射频电路收发开关提供控制信号切换电路的发射、接收状态;电源为射频电路中的有源元器件和控制电路中的数控器件提供必要的直流电信号。

图1 数字TR组件原理框图

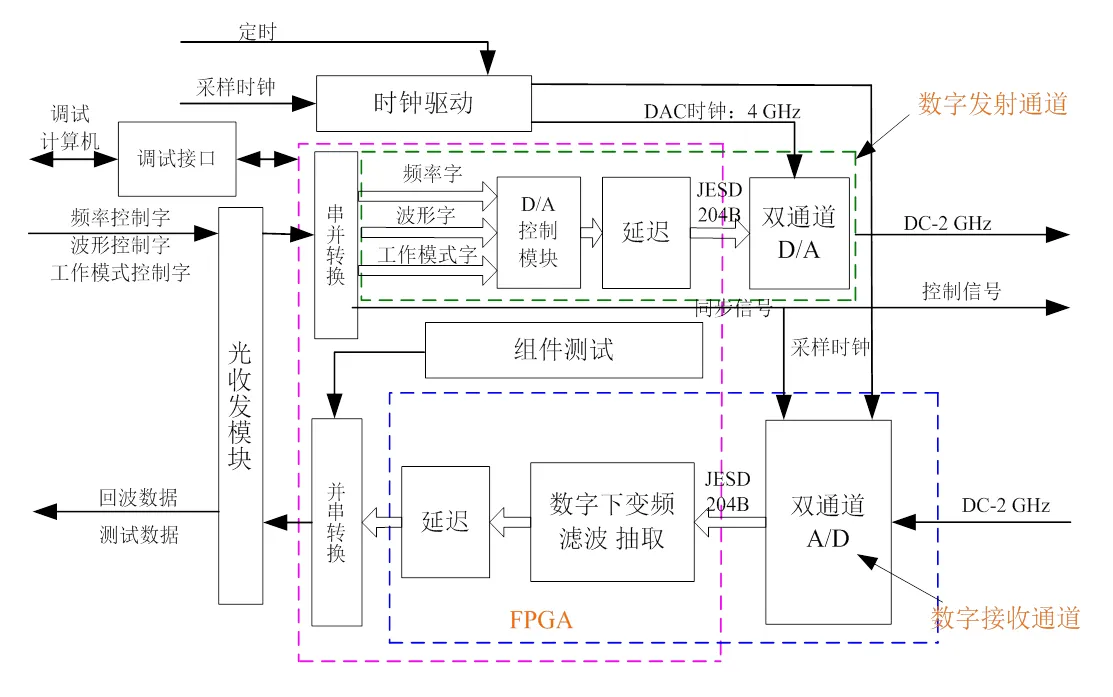

数字模块主要由数字发射通道、数字接收通道、组件电源监测电路、时钟驱动电路以及接口电路等组成。

数字模块使用A/D射频直接采样技术、协同D/A、A/D、光纤传输和存储器等高速器件是需要重点考虑的问题。接收通道中,射频前端送来的信号经过滤波后进入A/D,A/D在P波段直接对射频信号进行采样,变换得到的数字信号经由FPGA处理通过光纤传送给信号处理。发射通道由D/A产生灵活可变的发射波形,经过滤波后进入T/R组件。控制器信号在FPGA内部产生,先接收控制信息,再转换成A/D、光模块的工作参数和射频模块的控制信息,以及D/A的频率、波形、状态、控制信息,以此控制整个数字模块的运行。数字模块原理框图如图2所示。

图2 数字模块原理框图

中心机通过阵列控制单元送来的雷达的状态信号、频率和波形代码等以高速串行传输方式进入FPGA内部的串并转换电路,D/A控制模块根据雷达工作状态以及定时信号控制四通道D/A产生相应的基带发射信号。

从射频模块送来的射频回波信号首先进入单通道A/D变换器,在采样时钟ADCLK、定时信号以及多芯片同步信号的控制下对一路回波信号进行数字化采样,采样后对数字回波数据进行数字下变频将回波数据转换为正交、两路数据,然后根据雷达处于搜索还是跟踪状态对、数据进行抽取,对应于相应的信号带宽,对抽取之后的数据再进行FIR数字滤波。对回波数据在FPGA内部进行缓存后再进行并串转化和编码,通过光纤收发模块将回波数据采用非实时传输方式传送到信号处理机。

2 数字通道同步实现

对于多通道数字接收系统,仅取得具有优良性能的单通道采集电路是不够的,宽带阵列的多个通道难以避免在并行采样时出现不同步现象,这会极大地影响到系统性能,对于多通道数字接收系统而言,影响同步的因素主要有工作时钟、系统参考信号和数据传输的同步问题。

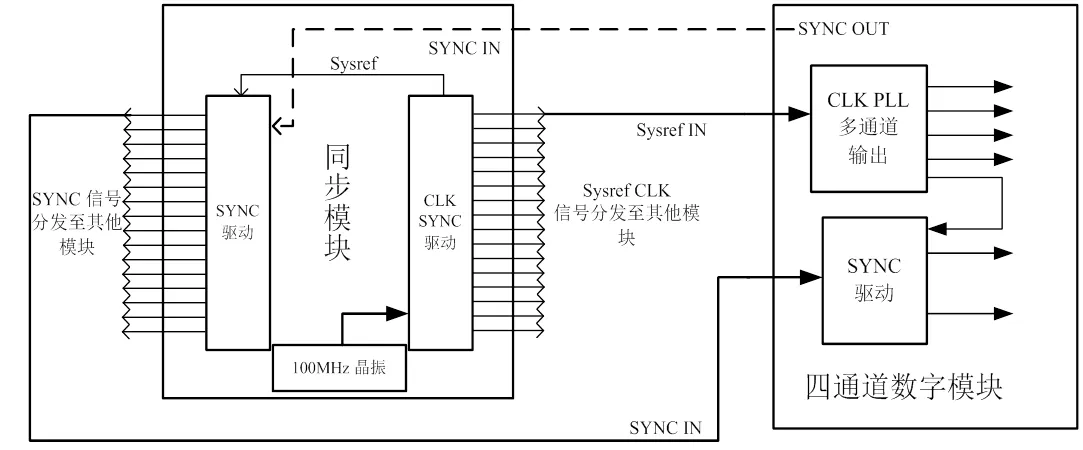

同步过程需要设计外置独立同步模块,用于同步分发参考时钟,同步SYNC信号到参考时钟并同步分发给各模块,如图3所示。用于分发Sysref时钟(即高精度公共时钟)的射频线缆全部等长,长度误差小于1 mm,长度在1 cm~150 cm。高精度公共时钟以方波形式传输,用于分发SYNC同步信号(即触发信号)的射频线缆全部等长,长度误差小于10 mm,长度在50 cm~200 cm,并且这些线比Sysref时钟分发的线长50 cm。同步模块的触发信号输入来自任意一个模块或者是用户信号处理机。触发信号在同步驱动前受高精度公共时钟触发,从而把触发信号同步到高精度公共时钟域。

在电路、系统和软件设计上,需要多方面综合考虑同步性,主要措施包括:

1)电路设计。单元内部各通道对触发脉冲的同步响应直接影响上行信号相位控制的稳定性、下行信号采样时刻的一致性,对时钟(FPGA时钟、D/A系统时钟、ADC采样时钟)和定时脉冲的硬件通路必须控制等长、减小延迟,并尽量减少相位随环境温度的器件(比如模拟滤波器等);

2)系统设计。严格计算系统时钟和定时的频率指标,要求定时器系统时钟、A/D采样脉冲、D/A系统时钟、同步参考时钟等皆为同源时钟,并且各时钟频率间满足整数倍关系。以高速电路设计标准,对各关键时钟的信号完整性进行约束;

3)软件设计。在硬件上是很难做到多路高速时钟完全同步的,而FPGA的软件化和数字化处理,使得我们可以灵活地控制FPGA内部的时钟相位,从而改变了DDS、DDC的控制码与同步脉冲之间的时序关系,完善了系统的同步设计。

采用高精度光纤传输定时和控制信号,严格控制硬件电路设计、加工流程,保证时钟、定时脉冲到各单元尽量等距离传输。针对本课题选用的核心数字A/D、D/A器件,利用JESD204B高速A/D、D/A同步接口协议标准,可实现大规模数字器件组阵,并实现多通道的信号产生和采样及高速数据传输同步。

图3 时钟分发原理图

3 数字收发组件实现

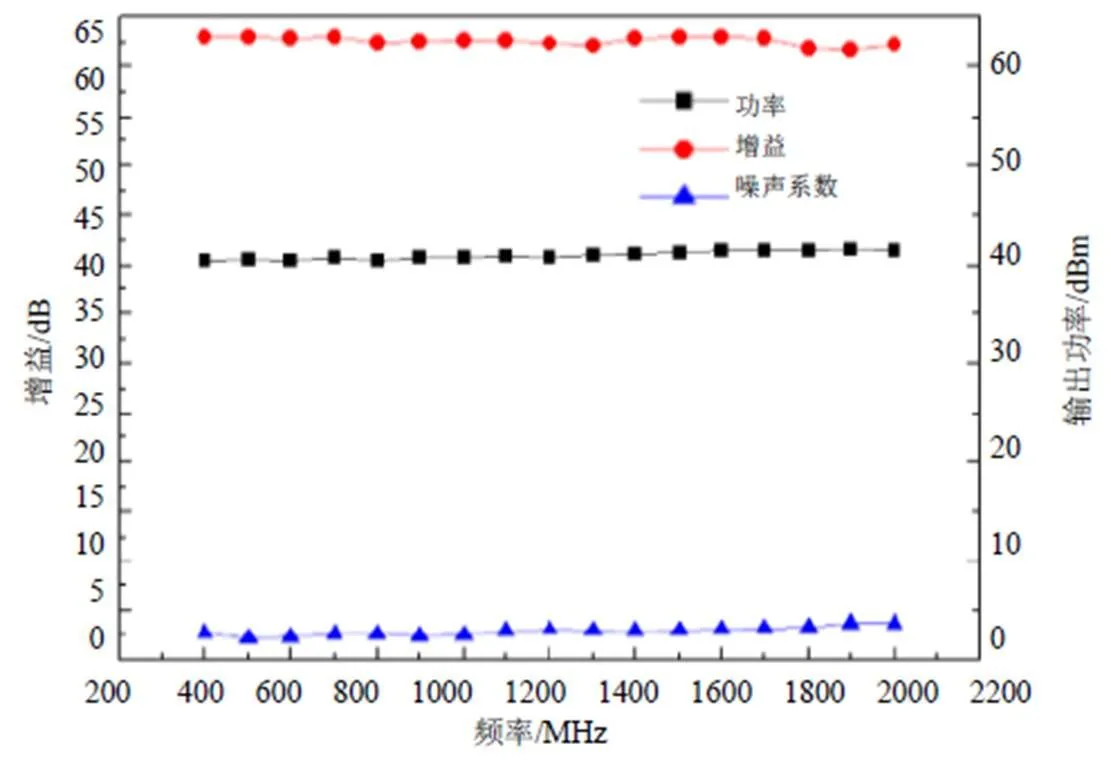

模拟T/R组件研制初样实物如图4所示,工作频带内射频指标如图5所示。

图5 模拟T/R组件射频测试指标

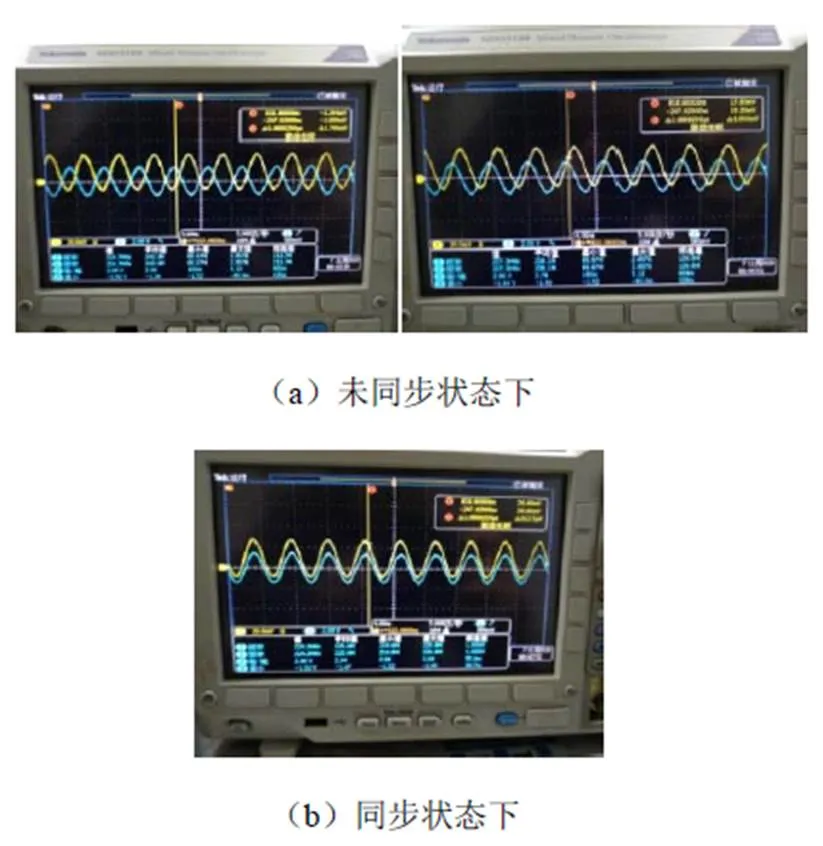

为验证数字T/R组件的射频直接产生和多通道同步能力,研制了数字T/R组件初样实物,如图6所示。针对组件的任意信号射频直接产生和模块级的多通道同步展开相关测试,测试结果如图7所示。

图7 同步测试结果

数字组件上电初始,在未提供同步触发信号的前提下,D/A处于不同步状态,每次开机其通道间输出信号相位不定,对组件进行同步复位,板间两片D/A根据同步触发完成同步设置,实现板间同步。

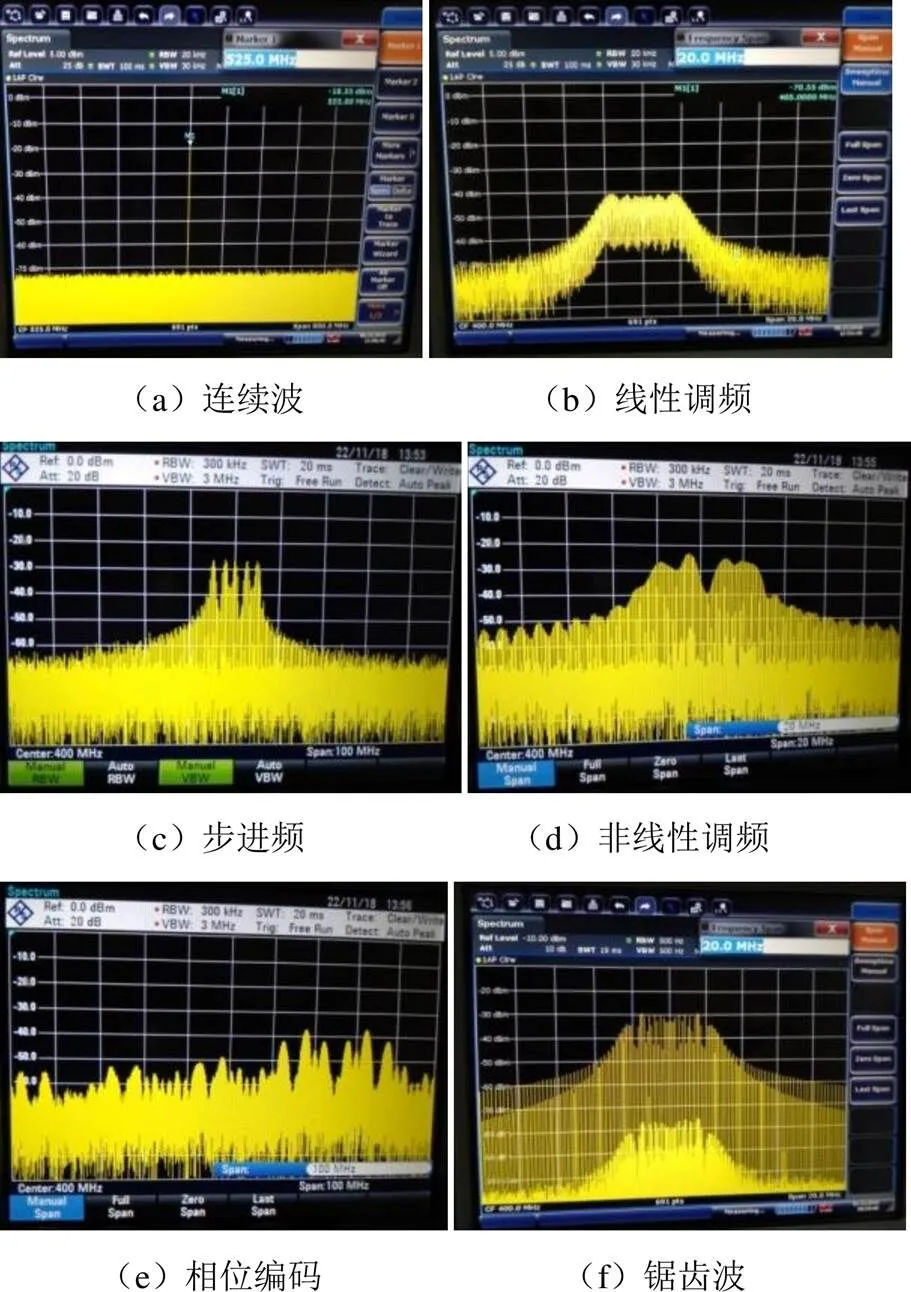

针对数字模块任意波形产生能力测试如图8所示,依次产生了连续波、线性调频、步进频、非线性调频、相位编码、锯齿波。

图8 任意波形产生能力测试

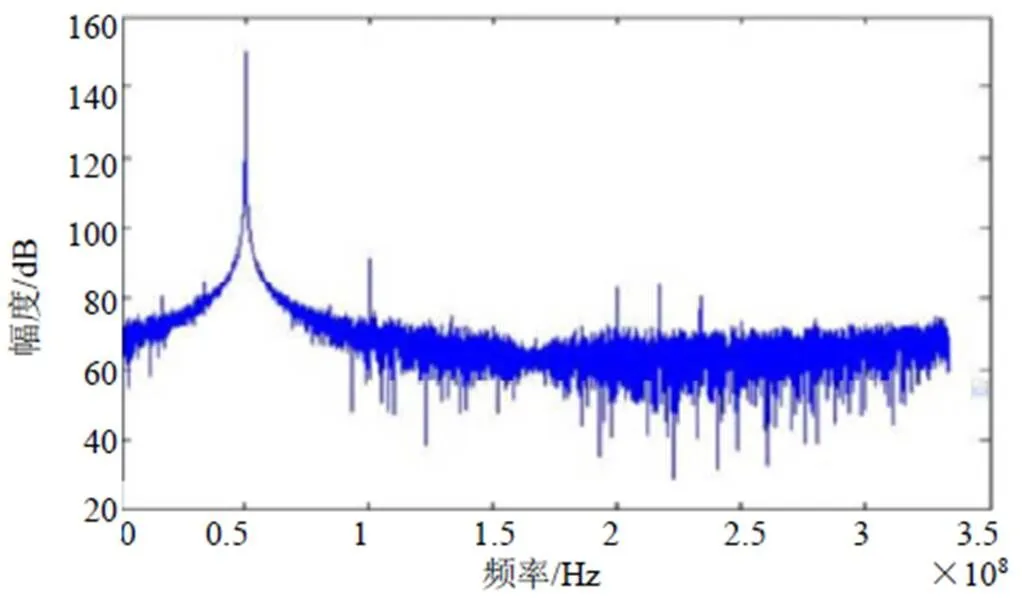

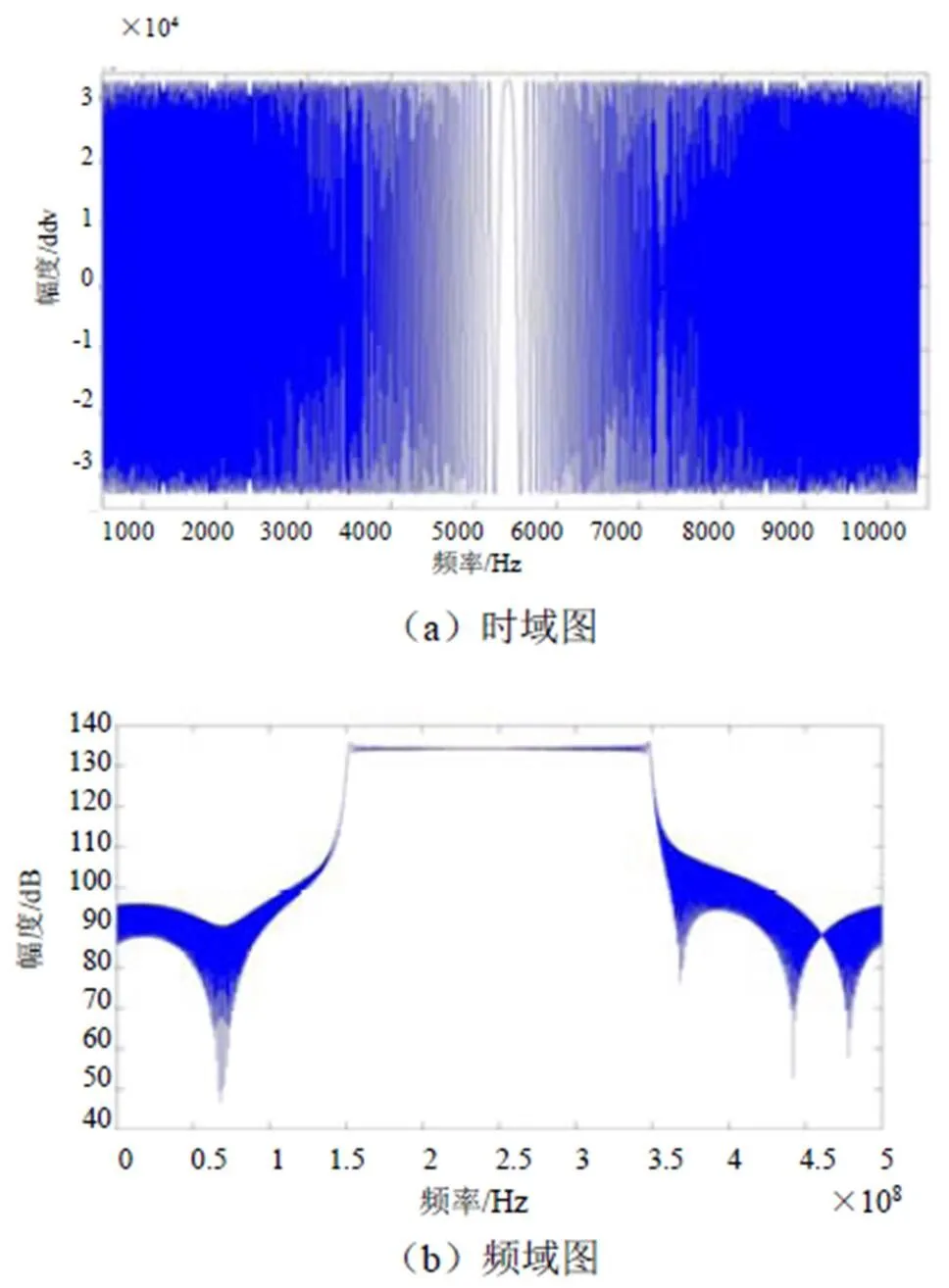

点频信号回环测试,通过FPGA产生零中频信号,经过D/A内部NCO进行上变频,其中NCO频率设置为750 MHz,经D/A产生信号经过外部射频线缆进行回环、A/D采集,其中A/D采样率设置为2 Gbps/s,A/D内部NCO频率设置为700 MHz,最终输出时域IQ波形如图9所示,对应信号频率为50 MHz。

图9 恢复后的D/A输出点频脉冲频域图

线性跳频信号回环测试通过FPGA产生宽带中频信号,经过D/A内部NCO进行上变频,其中NCO频率设置为750 MHz,经D/A产生信号经过外部射频线缆进行回环、A/D采集,其中A/D采样率设置为3 Gbps/s,A/D内部NCO频率设置为500 MHz,最终输出时域IQ波形如图10所示,对应信号频率范围为150 MHz ~350 MHz。

图10 恢复后的D/A输出宽带线性调频信号

经数字T/R组件联调,可实现对数字模块产生脉冲信号(线性调频脉宽10 μs,周期100 μs)的驱动放大,并实现40 dBm功率的最终输出,数字T/R组件联合调试测试环境如图11所示。实验验证,输出信号经50 dB衰减后,连入数字T/R组件接收通道,并由A/D采样后,将D/A产生的点频脉冲信号和线性调频脉冲信号恢复。经实验验证,数字T/R组件可实现对频率、波形、通道幅度/相位、接收增益等参数的实时控制,以完成阵面的参数化控制。组件控制参数如表1所示。

图11 数字T/R组件联合调试测试环境

当设置D/A内部NCO频率为NCO,数字生成中频信号频率为data,则通过D/A输出信号频率out=NCO+data。通过上述结果分析可知,被测件在2 Gbps/s及3 Gbps/s工作模式下,工作正常,能够实现需要的波形信号,并可以实现对射频信号的直接采样,恢复发射波形。

表1 组件控制参数

4 结论

本文通过P-L波段数字T/R组件的研制,实现了DC-2000 MHz频率范围内的任意波形信号的射频直接产生和射频直接采样,并通过JESD204B协议和同步时钟驱动的设计,实现了板间的收发同步,最终通过上位机软件实现对多数字收发通道的波形、频率、相位等参数的实时控制。

[1] Reinhold Ludwig, Pavel bretchko. RF circuit design: Theory and application [M/OL]. Learnengineering.in, 2002.

[2] J-M.Dieudonne, B.Adelseck. Advanced MMIC components for Ka-band communication systems[C]. IEEE microwave systems conference, 1995.

[3] 李涵秋. 微波芯片及模块技术创新发展战略研究[J]. 电子机械工程,2001(5):2-7.

[4] 高勇,王绍东. 采用LTCC 技术的X波段接收前端MCM 设计[J]. 现代雷达,2008,30(5):106-108.

[5] Vafa-Sedghi, Abdolali-Abdipour, Ahbas-Mohammadi. A flat conversion gain sub-harmonically pumped image rejection mixer in MM-Wave band[C]. Microwave and Millimeter Wave Technology, 2004. ICMMT 4th International Conference on, Proceedings 18-21 Aug.2004, 312-315.

[6] Cohn S.B. Characteristic Impedance of Shielded Strip Transmission Line[C]. IRE Trans, Microwave Theory Tech., 1954, MTT-2: 52-55.

[7] Bahl I.J.,and R.Garg. Designer’s Guide to Stripline Circuits [J]. Microwaves, 1978(17): 90-96.

[8] Gunston M. Microwave Transmission-Line Impedance Data[M]. London: VanNostrand-reinhold,1972: 38-39.

Design of Multi Channel P-L Band Digital T/R Module

WANG Yi, JI Shuai

P-L band digital T/R module is implemented in the paper. The direct generation and sampling of any waveform signal in the DC-2000 MHz range are completed. Through the design of JESD204B protocol and synchronous clock driver, the transceiver synchronization between multiple digital channels is realized. Finally, real-time control of waveform, frequency, phase and other parameters of multi-digital transceiver channel is realized by upper computer software.

L Band; Digital T/R Module; RF Direction Generation and Sampling

TN957

A

1674-7976-(2022)-02-138-05

2021-11-17。王轶(1983.02—),陕西西安人,高级工程师,主要研究方向为数字微系统技术。