同步以太网在5G 网络设备中的应用

邓 兵

(上海剑桥科技股份有限公司,上海 200000)

随着数字化技术的快速发展,5G 的应用给人们带来极致用户体验和更大的数据容量,它开启物联网时代的新纪元。5G 主要应用于车联网、工业智能控制、智能制造、远程医疗、无线家庭影音、高清网络直播、智慧城市等等。在这些应用中需要更高的速度和更低的延迟,如购物节中的“秒杀”“整点开始拍”,远程医疗等,都要求毫秒级甚至微秒级的时间同步。现阶段的网络设备以晶振为时钟源,时钟晶振工作在自由振荡状态。由于环境温度变化,电子元器件晶振老化和电磁干扰等原因,晶振的振荡频率与标准频率存在一定误差。虽然这些误差很小,但是长期累积会产生较大的影响。

想要保证网络设备的时钟同步,必须保证网络设备的频率同步。根据国际电信联盟ITU 规定的时钟同步的传输方式,本文介绍了其中一种方式,同步以太网SYNC-E 的时钟传输,在5G 设备中的每个节点,都从物理链路层提取线路时钟,使本地时钟锁定在上级时钟源,并将锁定后的时钟传给下级5G 设备,通过逐级时钟锁定方式,实现全网逐级同步到主参考时钟,给时间信号同步提供了可靠保证。

1 5G 设备中同步以太网简介

为了解决5G 设备中时钟同步的技术问题,本文提供了一种5G 设备中同步以太网SYNC-E 同步时钟的方法,同步以太网SYNC-E 是在物理层实现高精度的频率同步,不受上层应用带来的影响。它包括5G CU 通过GPS 模块获取高质量的时钟源GPS 信息,并每秒输出一个脉冲,传递给下一级设备5G DU;5G DU 的锁相环PLL 时钟单元锁定到CU 输出的秒脉冲,并产生系统时钟,系统时钟为以太网端口提供时钟源,用于以太网物理层发送数据时的时钟,从而实现时钟向下级节点传递;5G RU 的PHY 时钟处理模块从以太网码流中提取出以太网链路时钟,5G RU 的PLL 时钟单元锁定到提取到的以太网链路时钟,并产生系统时钟供5G RU 使用。这样5G RU 间接锁定到GPS 模块时钟。5G 网络拓扑图如图1 所示。

图1 5G 网络拓扑图

所述同步以太网,是一种从以太网链路码流恢复时钟的技术Synchronization Ethernet,简称SYNC-E。通过以太网PHY 芯片物理层从串行数据码流中提取出发送端的时钟,从而实现网络时钟同步。2006 年,国际电信联盟在G.8261 中提出了同步以太网概念。第二年在G.8262 中对同步以太网的性能要求进行了标准化。所述锁相环PLL(Phase-Locked Loop)是一种反馈控制电路。利用输入的外部参考信号控制内部环路振荡信号的相位和频率。锁相环一般由环路滤波器LF(Loop Filter)、鉴相器PD(Phase Detector)和压控振荡器VCO(Voltage Controlled Oscillator)3 部分组成。其工作原理为:当输出电压与输入电压保持固定的相位差,输出信号的频率与输入信号的频率相等时,即输出电压与输入电压的相位锁住。

所述5G CU 是第五代移动通信技术集中单元(Centralized Unit)。CU 设备主要包括非实时的无线高层协议栈RRC、PDCP 等功能,同时也支持部分核心网络功能下沉和边缘应用业务的部署,非实时的配置和控制决策。

所述5G DU 是第五代移动通信技术分布单元(Distributed Unit)。DU 设备主要处理物理层功能和实时性需求的二层功能。

所述5G RU 是第五代移动通信技术天线单元,负责数据与信号DAC、ADC 转换,属于网络的前传部分。

2 同步以太网在5G 设备中的具体实施方式

2.1 GPS 模块提取GPS 时钟信号

GPS 模块主要完成卫星信号接收功能,自动选择卫星信号波束。GPS 利用非常稳定的原子时钟作为其时基。GPS 模块接收到卫星信号后可以获得位置信息、高精度时钟和频率信号,提供高精度1PPS 秒脉冲输出。GPS 模块是5G CU 的一个功能模块,这相当于5G CU 输出1PPS 秒脉冲作为5G DU 的参考时钟。

2.2 同步以太网在5G DU 的实现方法

2.2.1 5G DU 锁定5G CU 输出的1PPS 秒脉冲

5G DU 要锁定到5G CU 输出的1PPS 秒脉冲会用到重要器件时钟转换器。时钟转换器由系统时钟锁相环、参考时钟输入、模拟锁相环、数字锁相环和输出分配器等组成。著名芯片公司亚德诺(ADI)、德州仪器(TI)和Maxim 等都推出了时钟转换器芯片。在芯片厂商官方网站可以下载桌面软件应用程序,应用程序由常用框架和各特定元件插件组成,用于配置时钟转换器,主要配置框架如图2 所示。

图2 5G DU 的时钟转换器框架

5G DU 时钟转换器锁定到5G CU 输出的1PPS秒脉冲的过程为:

(1)首先产生时钟转换器的时钟。5G DU 时钟转换器的晶振选用48 MHz 有源晶振,连接芯片的XOA和XOB 输入引脚。当使用不太稳定的PLL 参考源时,低于大约50 Hz 的环路带宽可以防止PLL 锁定或导致锁定事件的随机丢失。尽管减轻这一问题的一种方法是使用高稳定性系统时钟源(如OCXO),时钟转换器提供了集成系统时钟补偿能力,降低了对较高频率晶体的稳定性要求,同时提供了对系统时钟的突出相位噪声。要使用此功能,连接到XOA/XOB 引脚的晶振为25~60 MHz。系统时钟PLL 的输出构成系统时钟频率。系统时钟频率取决于反馈分频器的值,范围为4~255,可以通过8 位反馈分频器寄存器进行编程,得到时钟转换器的时钟为2.4 GHz。

(2)其次时钟转换器具有数字锁相环(DPLL),DPLL 使用一个数字控制的振荡器(NCO),它依赖于一个数字频率调谐器(FTW)来产生输出频率。1PPS 秒脉冲经过数字锁相环(DPLL)产生输出频率给APLL。

(3)再次时钟转换器具有模拟锁相环(APLL),APLL 依赖于压控振荡器(VCO)作为产生输出信号的频率元件,其中输出频率取决于所施加的直流电压,APLL 中的VCO 可以调谐到其操作带宽内的任何频率。经过APLL 的输出频率为2.5 GHz。

(4)最后2.5 GHz 的频率经过20 倍的分频产生125 MHz 的时钟,这样输出的125 MHz 的系统时钟可以稳定地锁定到输入的1PPS 秒脉冲。

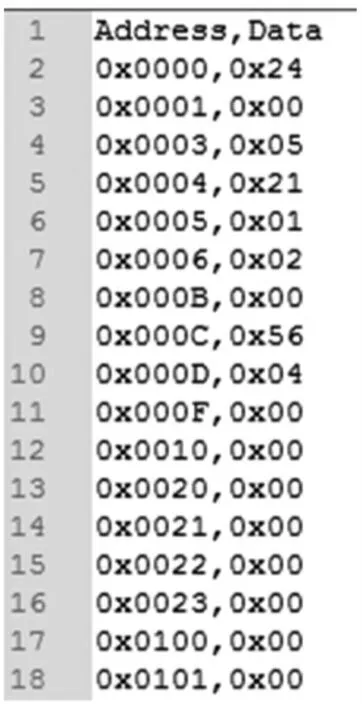

通过时钟转换器配置软件导出时钟转换器芯片的配置文件,扩展名为.txt,导出的配置文件有一千多行,部分配置文件的内容如图3 所示。配置文件的第一列为时钟转换器芯片的寄存器地址,第二列为时钟转换器芯片的寄存器值。5G DU 上电启动后通过程序把配置文件的值下载到对应的寄存器,然后运行。时钟转换器芯片的OUT0A、OUT0B 和OUT0C 对应引脚输出125 MHz 的时钟供5G DU 的物理PHY使用。

图3 时钟转换器配置软件生成的配置文件

2.2.2 5G DU 的高精度时钟往下一级5G RU 传送

以太网物理层编码平均每4 个比特就插入一个附加比特,传输的数据码流中不会出现超过4 个0 或者4 个1 的连续码流,传输的码流中就包含时钟信息。在以太网的Master 端使用高精度的时钟发送数据,在Slave 端恢复并提取这个时钟,在这个过程中时钟的精度不会有损失,可以与信号源保持高精度时钟同步。时钟转换器芯片输出125 MHz 的时钟作为5G DU 万兆PHY 的发送时钟发送数据。这样5G DU(Master 端)的高精度时钟通过网线或者光纤往下一级传送。

2.3 同步以太网在5G RU 的实现方法

2.3.1 5G RU 的PHY 芯片从数据码流中提取同步以太网时钟

时钟处理模块从以太网端口提取以太网链路时钟,可以从PHY 芯片MDI 接口数据码流中提取出25 MHz 时钟信号(如果是光纤端口,提取时钟信号为20.1 MHz)。5G RU 的PHY 芯片有两个端口分别为Port0 和Port1,其中Port0 作为Slave 端口通过光纤或者网线与5G DU 相连。

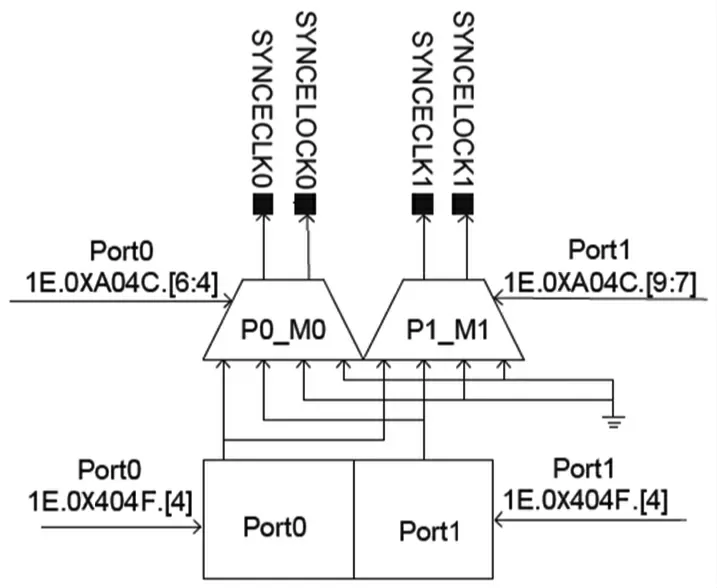

通过设置PHY 芯片1E.0X404F 寄存器bit4 位开启SYNC_E 功能,在芯片对应引脚输出两对同步时钟(SYNCECLK0、SYNCECLK1)和相应的同步锁定状态信号(SYNCELOCK0、SYNCELOCK1),也可以单独从一个端口恢复时钟,对应寄存器的描述见表1。当从接收的数据中锁住时钟后对应SYNCELOCK0 和SYNCELOCK1 引脚会输出高电平。

表1 SYNC_E 配置寄存器(30.0X404F)

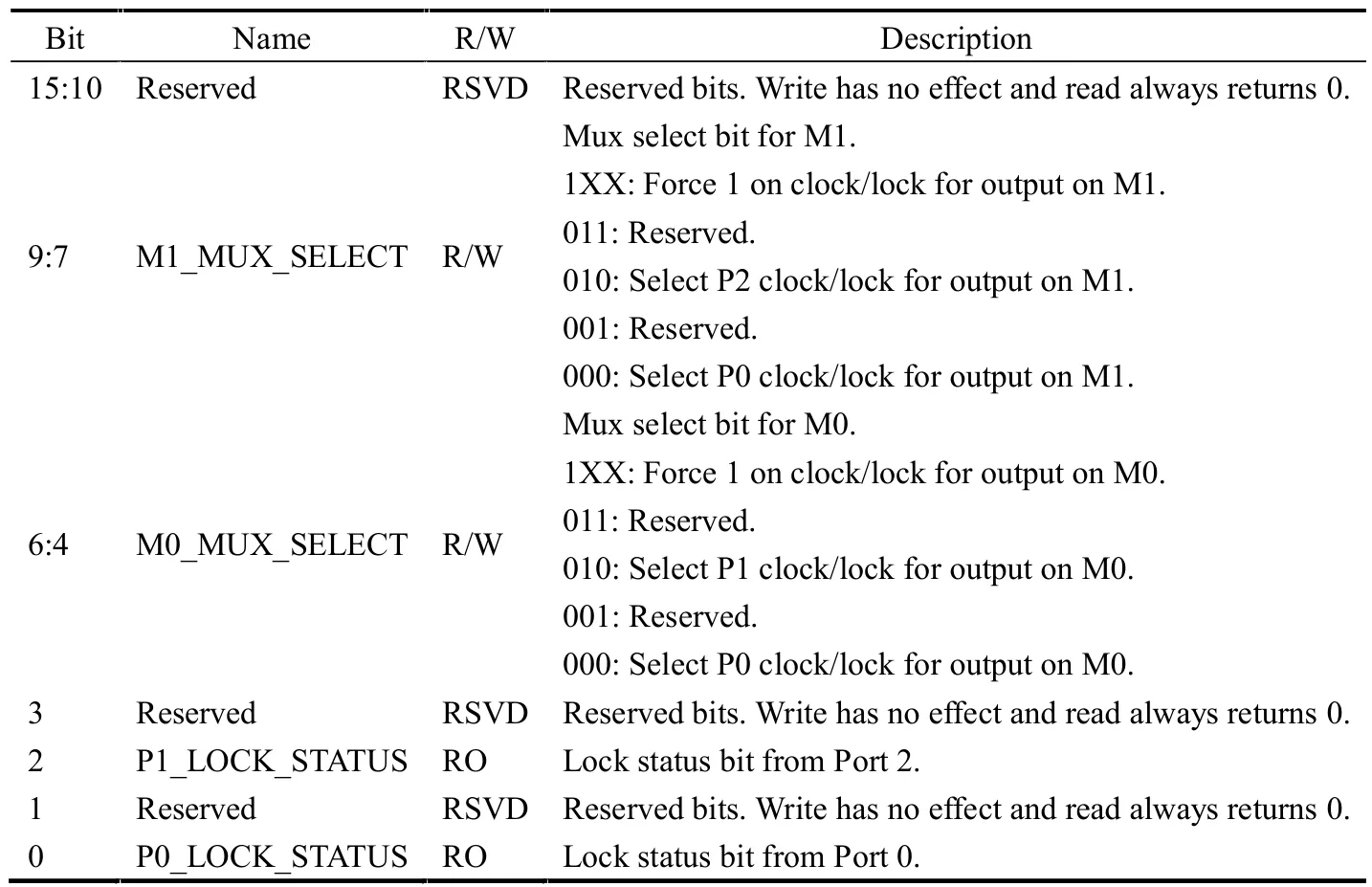

通过设置PHY 芯片1E.0XA04C 寄存器bits[9:4]位独立地从SYNCECLK0、SYNCECLK1 引脚输出锁定的时钟频率信号和SYNCELOCK0、SYNCELOCK1 引脚输出同步锁定状态信号,锁定后输出高电平,如图4 所示。Port0 端口1E.0XA04C 寄存器bits [6:4] 位控制P0_M0 MUX 输出SYNCECLK0 和SYNCELOCK0 引脚,Port1 端口1E.0XA04C 寄存器bits [9:7] 位控制P1_M1 MUX 输出SYNCECLK1 和SYNCELOCK1 引脚,寄存器描述见表2。

表2 SYNC Common CFG Register(30.0XA04C)

图4 PHY 恢复SYNC_E 时钟框图

2.3.2 从Port0 端口提取同步以太网时钟功能

以下是通过执行EnableSfpPort0SynceClk 函数实现从Port0 端口提取同步以太网时钟功能的程序。

2.3.3 5G RU 锁定PHY 芯片SYNC_E 时钟

5G RU 的PHY 芯片Port0 端口输出25 MHz SYNC_E 时钟信号,该信号接到时钟转换器,如图5 所示,原理与5G DU 时钟转换器的原理相同。5G RU 时钟转换器的晶振选用25 MHz 有源晶振,连接芯片的XOA 和XOB 输入引脚。通过8 位反馈分频器寄存器进行编程,得到时钟转换器的时钟为2.4 GHz。25 MHz SYNC_E 时钟通过时钟转换器数字锁相环(DPLL)和模拟锁相环(APLL),输出频率为3 GHz。最后3 GHz 的频率经过24 倍的分频产生125 MHz 的时钟。这样输出的125 MHz 的系统时钟可以稳定地锁定到输入的25 MHz 参考时钟。

图5 5G RU 的时钟转换器框架

5G RU 的系统时钟有3 种工作模式:自由运行模式、锁相模式和保持模式。

(1)自由运行(Free run)模式:如果5G RU 没有接5G DU,5G RU 不能提取SYNC_E 时钟,时钟转换器没有时钟源。时钟转换器工作在自由运行模式,提供的系统时钟精度受制于本地晶体振荡器精度。

(2)锁相模式:时钟转换器锁定25 MHz SYNC_E参考基准。输出的系统时钟精度与参考基准的精度保持一致。参考时钟基准是从上级5G DU 传下来的。

(3)保持模式:时钟转换器失去25 MHz SYNC_E参考基准,在一段时间内根据以前的时钟参数保持原有的时钟精度,保持时间一般为24 h。经过保持模式,时钟转换器进入自由运行模式。

3 同步以太网在5G 设备中验证方法

将5G CU、5G DU 和5G RU 按照图1 的组网方式接到时钟测试仪。锁相工作模式下,5G CU、5G DU和5G RU 的系统时钟与GPS 1PPS 秒脉冲保持完全同步。保持模式下5G RU 的系统时钟精度可以达到±4 ppm,完全符合设计标准。

4 结论

同步以太网SYNC-E 在5G 设备中的应用,它包括5G CU 通过GPS 模块获取高质量的GPS 时钟源信息,并每秒输出一个脉冲给下一级设备5G DU;5G DU 的时钟转换单元锁定到CU 输出的秒脉冲时钟信号,并产生系统时钟,5G DU 以太网源端口使用该高精度的时钟发送数据给5G RU;在5G RU 的接收端恢复并提取该时钟。通过逐级锁定,全网逐级同步到GPS 时钟源输出的高精度时钟。同步以太网的时钟精度不会受网络负载影响,同步性能好,可靠性高。可以广泛将同步以太网SNYC-E 技术应用于5G 设备中,完全满足对时间同步要求极高的秒拍、科研、军事、医疗卫生等领域。