FPGA部分重构系统设计与实现

杨文涛 侯睿 顾明超 刘子奕 李春晓

摘要:凭借开发周期短、使用场景灵活等优点,现场可编程逻辑门阵列(Field Programmable Gate Array,FPGA)在电子对抗系统中的应用越来越广泛。随着电子对抗系统的复杂化和功能多样化,系统设计对FPGA的硬件资源规模需求越来越大,随之带来了成本骤升的问题。针对日渐复杂的系统设计和有限的FPGA硬件资源的矛盾,提出了一种基于FPGA和DSP实现的部分重构系统方案。通过不同时刻动态加载不同FPGA功能模块的方式,实现了FPGA资源的复用。这种技术是数字系统设计方法、设计思想的变革,使FPGA资源利用率成倍提高,实现系统功能所用的硬件規模大大下降。

关键词:现场可编程逻辑门阵列;部分重构;测向

中图分类号:TN911文献标志码:A文章编号:1008-1739(2022)13-48-5

0引言

现场可编程逻辑门(Field Programmable Gate Array,FPGA)凭借其编程及重构高度灵活、逻辑资源和I/O资源丰富等优势在通信、电子对抗等领域应用越来越广泛[1]。目前,主流的FPGA芯片基本都基于SRAM工艺,芯片上电后首先需要通过BPI,SPI,JTAG,SelectMAP等方式加载配置bit文件,常规应用时需要为FPGA配备可存放bit文件的EPROM芯片。随着现代软件无线电技术的进步,侦察测向领域对FPGA芯片资源的需求越来越大[2]。持续升级硬件资源更丰富的FPGA芯片会引起硬件成本的持续攀升,因此,对FPGA硬件资源实现“分时复用”就显得尤为重要。

FPGA芯片的bit加载有2种方式[3]:整个bit重新加载,对整个FPGA进行重新配置,此种应用常配合EPROM使用,即在EPROM中烧写多个bit文件,根据需要通过上位机切换存储的bit文件。由于EPROM芯片的存储容量有限,能够存储的bit文件个数受限,且因为整个FPGA都进行了重新配置,SRIO接口需要重新入网,所有功能都必须重新启动。切换时间较长,功能连续性受限。部分重构(Partial Reconfiguration,PR)可以在一个FPGA程序设计内,动态改变模块功能[4]。FPGA本身是一个可以灵活配置程序的器件,PR在此基础上更进一步,通过一个部分配置文件(通常称为部分bit文件),来改变FPGA的部分功能,在这个过程中,FPGA的其他部分仍然可以正常工作。

Xilinx几乎所有的7系列芯片都支持逻辑资源、乘法器资源和存储资源的部分重构[5],UltraScale,UltraScale+和Zynq UltraScale+系列还额外支持时钟资源的重构。由于UltraScale系列芯片价格昂贵,且目前无国产化可替代芯片,应用场景局限性大,因此选择Xilinx的XC7VX690T FPGA来完成部分重构系统设计。Xilinx的XC7VX690T芯片拥有3 600个乘法器、1 470个BRAM及丰富的LUT资源,芯片大小及丰富的接口非常适合部分重构的设计。基于此,本文提供了一种基于FPGA部分重构的侦察测向实现方案,可实现多路宽带测向和窄带测向预处理的实时切换,实现了FPGA资源的“复用”,为FPGA应用的低成本工程化提供了一种参考方法。

1部分重构

1.1部分重构原理

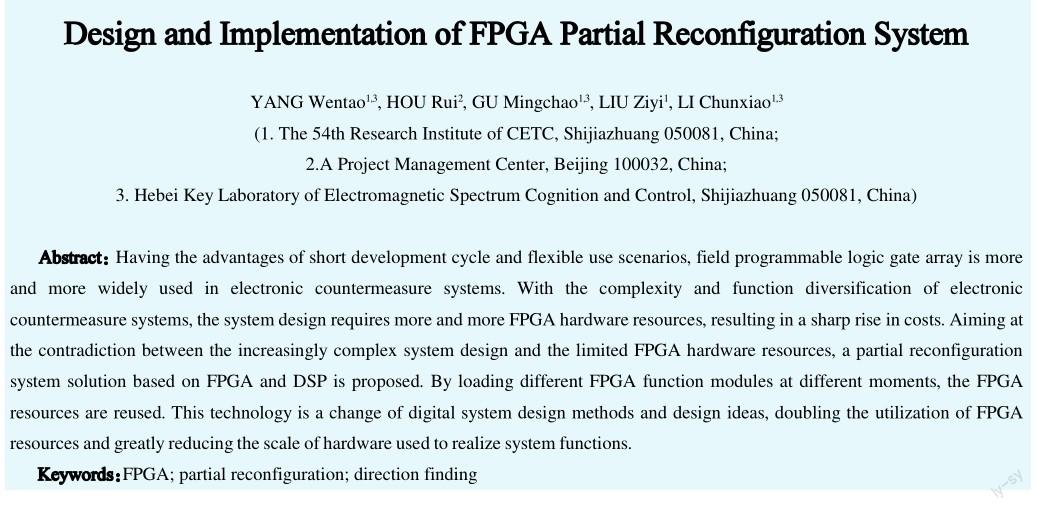

Xilinx XC7VX690T芯片可将芯片内部逻辑划分为静态逻辑和动态逻辑2个独立部分,静态部分上电后保持不变,动态逻辑部分可以根据应用需求实时切换[6]。FPGA部分重配置示意如图1所示,Reconfig Block‘A为可重构部分,整个FPGA中又可以包含多Reconfig Block‘A部分,可根据需要配置任意个数的子模块A。芯片工作时,静态逻辑部分上电即正常运行,可重构逻辑部分可通过SRIO总线将需要的功能模块的bit写入FPGA,此写入时间一般不超过100 ms,从上位机处可达到各种功能即点即用的视觉效果,由此可配合外部存储达到“无限”扩展FPGA资源的效果,适用于功能繁杂,但各种功能分时运行的系统[7]。

部分重构在PR流程中,经过FPGA的布局布线过程后,不仅会生成每个功能的完整的bit文件,每一个重配置模块(Reconfigurable Module,RM)还会生成一个部分bit文件[8]。所有的重配置模块会共用一个顶层的、静态的布局布线结果。每一个重配置模块布局布线时,会先读入共用的静态布局布线结果,在此基础上再进行重配置模块的布局布线,这个过程可以称为子实现(Child-implementation)。

1.2部分重构实现流程

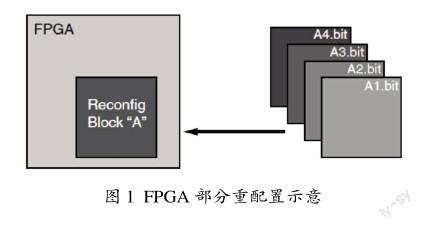

按重构区域划分,FPGA的重构可分为动态重构,和静态重构两种方式。FPGA的设计流程共包括设计、编译和运行三个阶段[9]。在设计阶段,需要完成逻辑设计、综合、布局布线设计。静态重构只包含一个功能电路的逻辑设计,并对该功能电路进行综合、布局布线。动态重构则根据需求包含F1~F多个功能电路的逻辑设计,并且布局布线时需要对设计中的所有功能电路进行布局布线。在编译阶段,需要配置文件生成工具并产成配置文件,静态重构只产生一个配置文件,而动态重构则需要通过配置文件生成工具生成多个配置文件,最终在重构件生成器的作用下得到初始构件和多个重构件。在运行阶段,静态重构只需在系统启动时载入FPGA运行即可。动态重构则需要在上位机的控制下,通过总线将编译阶段产生的重构件写入FPGA,实现各子功能电路的部分重构。设计流程如图2所示。

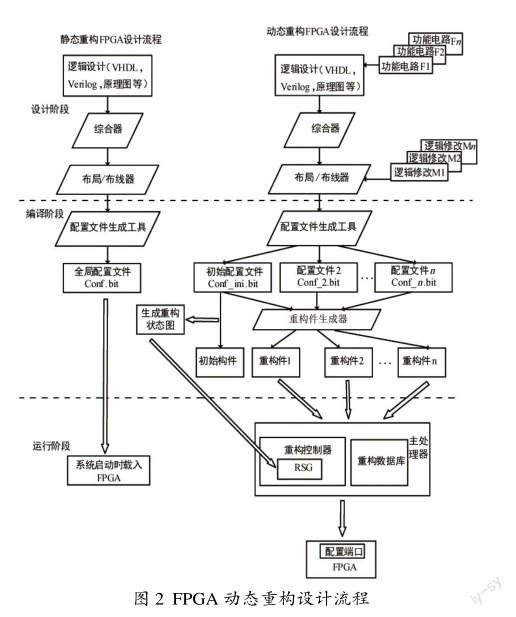

Xilinx芯片实现部分重构需要将编译生成的不同重构子bit文件写入FPGA中,bit重加载需基于ICAP接口,XC7V690T芯片对应接口为ICAPE2。bit写入时序如图3所示。其中,CSI_B为读写使能,RDWR_B为读写状态控制,DATA为bit文件数据接口。

2工程應用

2.1侦察测向处理单元

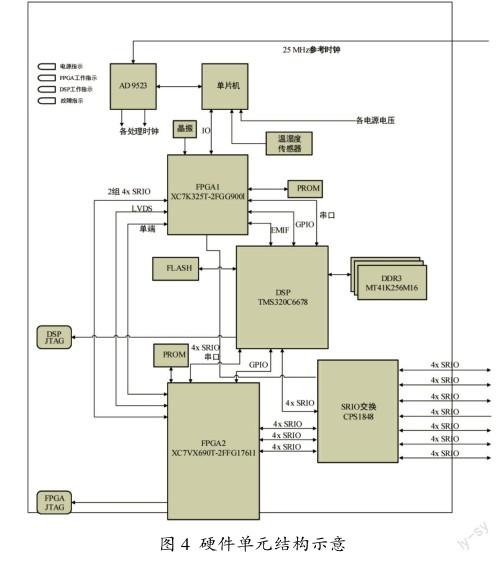

某侦察测向处理单元需要实现宽带信号侦察、5阵源干涉仪测向、26个频点特定信号分析解调等功能。针对该应用需求,设计了一块由FPGA和DSP等组成的硬件单元,在FPGA中实现了测向和分析解调预处理功能,在DSP中完成了干涉仪测向和分析解调功能。

2.2硬件电路设计

为降本增效并满足可国产化替代的需求,硬件电路设计时选用了一片型号为XC7V690T的FPGA芯片和一片型号为TMS320C6678的DSP芯片作为硬件单元主处理器件。通过一片CPS1848芯片实现本单元及其他硬件单元的SRIO交换互联功能;XC7K325T和单片机控制板卡上电加载及初始化芯片;在DSP上接入了4片DDR3颗粒用以满足DSP缓存需求。详细结构如图4所示。

2.3 FPGA部分重构设计

为满足系统分辨率需求,需在FPGA中实现5路32 000点连续FFT、26路宽带数字下变频(DDC)、其他自检接口及数据传输模块等功能。核算资源可知,所有模块需要3 710个乘法器资源,超出XC7V690T片内可用乘法器设计能力。基于此,将上述需求进行部分重构模块设计。

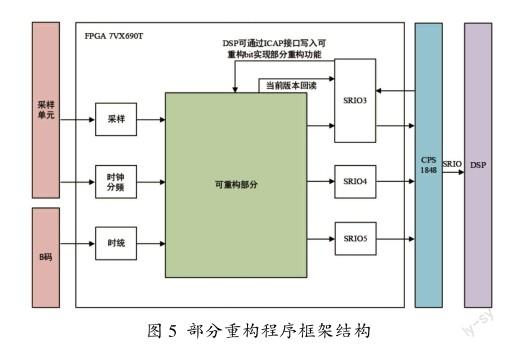

为满足7系列芯片部分重构规则并利于FPGA布局布线,将除I/O接口和时钟分频外的大部分硬件资源划分为一个PR区域,静态区域放置采样接口、时钟接口、时统接口和SRIO接口。采样接口用来接收ADC采集的外界信号;3组连接在交换芯片上的SRIO接口分别用来对外传输数据和接收上位机指令,其中,SRIO3还可用于为FPGA本身动态配置PR产生的重构bit文件。FPGA部分重构程序框架结构如图5所示。

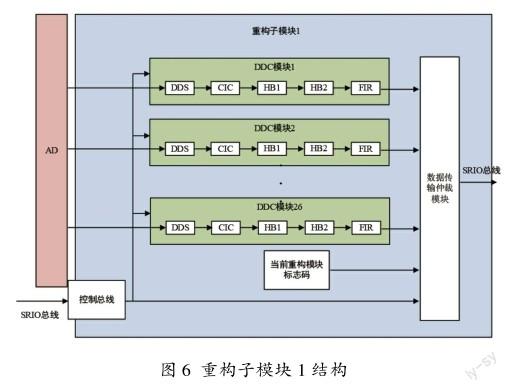

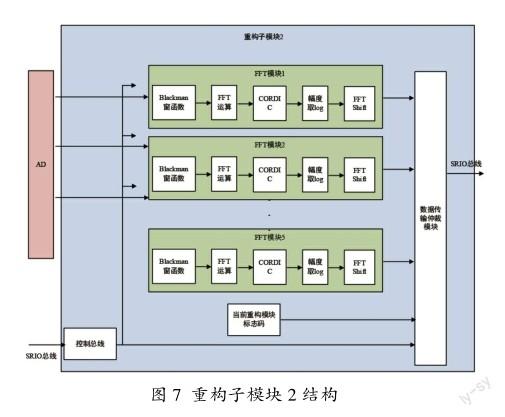

为平衡功能需求及硬件资源限制,将干涉仪测向预处理功能和宽带分析解调功能分别设计为FPGA的部分重构子模块。拆分后子模块硬件资源占用均可满足芯片最大硬件资源限制并能通过SRIO总线动态切换功能模块。各重构子模块都可以实时回读当前模块版本标志。

重构子模块1包含26路DDC模块和数据传输仲裁模块,可实现26个频点信号的变频抽取滤波,并通过SRIO将数据传输到DSP实现分析解调算法解析。重构子模块1共需占用乘法器资源3 250个,满足芯片资源限制条件。重构子模块1结构如图6所示。

重构子模块2包含5路FFT模块和数据传输仲裁模块,可对5阵源的采样信号进行连续FFT运算,计算信号幅度相位,并通过SRIO将数据传输到DSP实现信号侦察和干涉仪测向处理。重构子模块2共需占用乘法器资源460个,满足芯片资源限制条件。重构子模块2结构如图7所示。

2.4测试结果分析

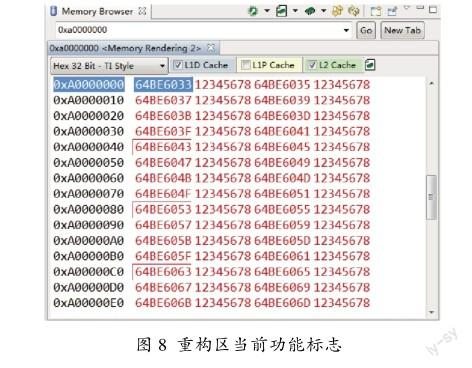

对基于部分重构方法设计的侦察测向处理单元进行板级测试,首先将静态逻辑部分bit文件烧写进EPROM中,FPGA上电后主动从EPROM中加载静态逻辑部分配置文件。板卡上电后首先通过DSP配置DSP和FPGA的板内路由,通过配置CPS1848将FPGA的3组SRIO与DSP的1组SRIO配置为全交换模式。完成路由配置后将重构子模块1的子bit配置文件从DSP写入FPGA中,完成对FPGA局部逻辑的电路配置。完成bit加载后,测试当前模块输出结果。读取重构子模块标志码,得到代表重构子模块1的特殊标志,即0x12345678与计数器的拼接。重构区当前功能标志如图8所示。

确认重构模块标志后对子模块进行功能测试,外部输入184.32MS/s采样率,141MHz中频的信号,DDC下变频140MHz,使能两级半带滤波器,CIC抽取倍数设为4,得到1 MHz频偏,11.52 MS/s采样率的复信号。经验证,部分重构后的模块功能输出正确。DSP收到的IQ数据如图9所示。

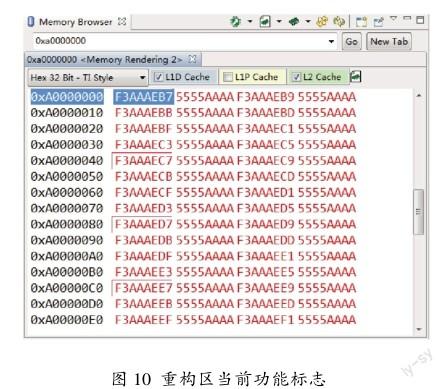

重复上述子bit文件配置过程,将重构子模块2的子bit加载到FPGA中,读取重构子模块标志码,得到代表重构子模块2的特殊标志,即0x5555AAAA与计数器的拼接。重构区当前功能标志如图10所示。

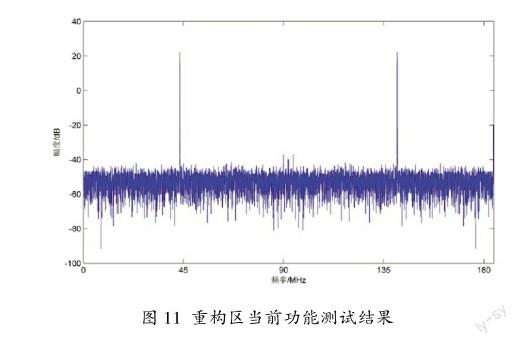

输入相同的外部信号,对部分重构后的重构区数据回读得到频谱数据,经验证,频点与输入信号相对应。测试结果如图11所示。

3结束语

本文设计通过DSP加FPGA的方式实现了一种复用FPGA硬件资源的工程应用方案。通过局部动态重构设计,在单片FPGA中实现了总资源需求超过FPGA本身硬件资源的算法模块,理论上按照本方案可以实现FPGA资源的“无限”叠加复用。為侦察测向、信号分析解调、信号产生等领域的FPGA设计提供了一种具有参考意义的实现方案。对节省硬件成本,提高FPGA器件使用灵活性具有积极意义,为复杂多功能系统的小型化设计提供了一种思路。

参考文献

[1]张宇,范建华,吕遵明,等.FPGA动态部分可重构技术概述[J].计算机与现代化,2014,49(3):210-214.

[2]任季中,赵倩.基于FPGA的高速跳频信号实时侦测[J].无线电通信技术, 2013,39(5): 78-80.

[3]姚爱红,张国印,关琳.基于动态可重构FPGA的自演化硬件概述[J].智能系统学报,2008(5):436-442.

[4]吴冬梅,何管清,邱昊.基于ARM的DSP与FPGA动态配置方案的设计与实现[J].舰船电子工程,2013,33(7):47-48.

[5]陈曦,沈佐峰.一种可靠的FPGA动态配置方法及实现[J].通信技术,2012,45(3):105-107.

[6]张炜,杨虎,张尔扬.一种灵活的实时FPGA数据配置方法[J].通信技术,2003(2):23-24,27.

[7]覃祥菊,朱明程,张太镒,等.FPGA动态可重构技术原理及实现方法分析[J].电子器件,2004(2):277-282.

[8]李庭胜.基于DSP+FPGA系统在线重构技术[J].信息安全与通信保密,2005(11):62-64.

[9]吕书东,徐光辉. FPGA被动串行配置控制器的研究与实现[J].军事通信技术,2006,27(4):66-69.