基于LabVIEW和FPGA的超声波探伤数据处理系统设计

谭群林,张东方,夏 浪,胡 亮,钟 盛

(株洲时代电子技术有限公司,湖南 株洲 412001)

0 引言

FPGA技术的灵活性使其成为复杂嵌入式系统设计、高性能数据采集和测试应用的首选方案。LabVIEW FPGA是National Instrument(简称“NI”)公司的一种嵌入式图形化开发环境,其开发效率高、代码可读性好、库函数丰富,适用于测控领域,但主要支持NI公司的FPGA板卡。基于LabVIEW和自主研发的FPGA目标机来开发系统是一种新的尝试,能参考的文献资料甚少。为打通LabVIEW环境下开发自主研发的FPGA终端的关键环节,本文以钢轨超声波探伤的数据系统设计为载体,参考《钢轨超声波探伤的信号处理》[1]的设计原理,采用FPGA构建超声波探伤数据处理系统,并使用组件级知识产权节点(Socket component-level intellectual property,Socket CLIP)[2]、IP集成节点[2]、IP核技术[3]解决FPGA硬件与LabVIEW之间的互联互通问题。由于该系统通道多、带宽高、吞吐量大,很适合FPGA的应用场景。与国内外同类系统相比:(1)系统集成度更高,其采用更高密度的XILINX 7系列FPGA搭载了DDR3内存、双以太网、16通道集成激励、串行32通道模数转换芯片等核心电路;(2)系统开发效率和性价比更好,传统FPGA主要使用VHDL、Verilog文本语言进行开发,本系统则采用National instrument公司的LabVIEW FPGA工具包,可高效地开发基于FPGA的数字系统。用此技术构建的超声波数据处理系统具备很高的性价比。

1 超声波探伤系统架构

钢轨超声波探伤检测系统由多传感器轮式探头总成、A型显示系统、B型显示系统、超声波数据处理系统及控制显示计算机等构成(图1)。探轮总成内部集成多路水浸式超声波探头,能够发射和接收超声波,超声波通过耦合液传递至被测钢轨,遇伤损或边界后反射回来,回波信号进入数据处理系统进行信号处理。然后分成两路输出,一路输出到示波软件上,进行A型显示,显示声波幅度与传输时间的关系;另一路传输到控制显示计算机,在上位机完成空间转换及伤损识别,把数字化的超声波信息转换成以钢轨里程及伤损埋藏深度作为参考系的B型显示。

图1 检测系统构成Fig.1 Composition of the detection system

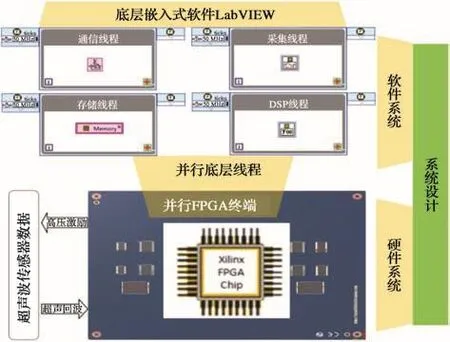

本文以超声波数据处理系统为设计重点,系统框架包含硬件系统和软件系统两部分(图2)。前端超声波传感器数据进入FPGA的硬件系统,FPGA芯片资源丰富,可用于构建采集、信号处理、通信及存储等复杂功能电路。嵌入式软件系统采用LabVIEW进行设计,它运行于底层FPGA硬件终端,实现算法及逻辑控制。

图2 系统框架设计Fig.2 System framework design

2 硬件系统

超声波数据处理系统硬件构架[4]如图3所示,其由轮式探头、FPGA主控电路、超声模拟前端电路、双千兆以太网电路、智能数据电路、定位同步电路及调试电路等组成。

图3 超声电子系统硬件架构Fig.3 Hardware architecture of ultrasonic electronic system

2.1 轮式探头

检测系统的数据传感装置采用轮式探头(图4),它是一种充满液体的能承受压力的软体橡胶轮,内部集成水浸式超声波传感器并朝不同方向布置,能探测钢轨内部不同部位和方向的伤损。超声波传感器通过高压脉冲激励传感器产生超声波,经过探轮和耦合介质进入到被测钢轨中。遇到钢轨内部的裂纹、空洞等伤损时,部分超声波能量反射回来,系统接收到反射回波后进行信号处理,以得到伤损回波的位置信息,并通过多个超声通道的组合信息完成伤损类型识别。轮式探头可在钢轨上滚动,实现高速动态检测。

图4 轮式探头设计与探测原理Fig.4 Wheel probe design and detection principle

2.2 FPGA主控电路

FPGA主控电路是系统控制的核心,由FPGA、DDR3和Flash组成(图5)。FPGA系统由两路低电压差分信号(low voltage differential signaling,LVDS)的差分晶振提供稳定的时钟输入,其中200 MHz有源差分晶振用于FPGA系统主时钟的驱动源,可用于驱动FPGA内部的DDR3内存控制器;125 MHz晶振预留给光纤GTP收发器使用。DDR3电路采用两片共1 GB容量的DDR3芯片组成,总线宽度为32bit、最高工作频率为400 MHz。

图5 FPGA主控电路Fig.5 Control circuit of FPGAmain

2.3 超声模拟前端电路

超声模拟前端电路包含多路超声激励电路和多路超声数据采集电路(图6),超声激励接收电路采用TX7316构建,其共设有16个脉冲发生器电路和16个发送/接收(T/R)开关,支持片上和片外波束形成器,集成片上浮动电源,可减少所需高压电源的数量。

图6 超声模拟前端电路Fig.6 Ultrasonic analog front end circuit

超声数据采集电路包括低噪声放大器(low noise amplifiter,LNA)、压控增益放大器(VCA)、时间增益放大器(time gain compensation,TGC)、抗混叠滤波器(Anti-Alias Filter,AAF)和8通道模数转换器(analog to digital converter,ADC)。LNA采用AD810型芯片,其固定增益输出为17.5 dB。VCA采用AD605型双运算放大器,两级串联,能在0.4~2.4 V的控制电压下实现-28~68 dB范围增益控制。AFE5801是8通道、12位、65MSPS串行输出转换器,其内置TGC和AAF,其中TGC可以通过编程获得-5~31 dB的增益用于距离波幅补偿,AAF通过SPI编程选择7.5 MHz、10 MHz或15 MHz任意一种频率的低通滤波器用于模拟前端滤波。ADC为LVDS接口输出,8个通道12位数据只需要8对LVDS接口就能实现与FPGA的连接,节约引脚资源,可实现更多通道、更高密度的应用。

2.4 双千兆以太网电路

千兆以太网通过2片KSZ9031型以太网芯片实现网络通信,该芯片支持10、100、1 000 Mb/s网络传输速率,通过 RGMII(reduced gigabit media independent interface)接口与FPGA(MAC)进行数据通信。当网络连接到千兆以太网时,FPGA和端口物理层(PHY)芯片KSZ9031的数据传输通过RGMII总线通信,传输时钟频率为125 MHz,数据在时钟上升沿和下降沿采样。千兆以太网电路[5]如图7所示。媒体访问控制器(media access control,MAC)的硬件控制器及通信协议在FPGA中完成。双路千兆以太网通信独立并行运行,有效提高了数据带宽且使用灵活。

图7 千兆以太网电路Fig.7 Gigabit Ethernet circuit

2.5 智能传感器、定位同步电路、JTAG调试电路

智能传感器、定位同步、联合测试工作组(joint test action group,JTAG)接口调试电路如图8所示。

图8 智能传感器、定位同步、JTAG调试电路Fig.8 Intelligent sensor、 positioning synchronization、JTAG debug circuit

智能传感器由数字温度传感电路和数字压力传感电路组成。LM75是高精度、低功耗数字温度传感器芯片,具备芯片互连(inter-integrated circuit,I²C)数字接口;数字压力芯片[6]是一种压阻式绝对压力传感器,其作为数字输出压力计,通过I²C或者SPI总线访问通信。FPGA通过I²C通信可以分别获得温度和压力数据。

定位同步电路由编码器、RS232和RS422串口电路组成。编码器采用增量型光电编码器,标准输出3 600 个脉冲,输出 3相互补信号:A+、A-、B+、B-、Z+、Z-,采用SN75182型微控制器将A+、A-、B+、B-信号转成A、B单极性方波信号后输入FPGA,A、B相输出相位差为90°,通过对编码器A、B相信号的计数与相位判断,可以用于里程的定位以及行进方向识别。

MAX232、ADM489分别用于实现RS232、RS422电路的功能。系统可通过串口获得北斗的经纬度信息、运监系统的公里标信息、射频标签定位信息、键盘输入的路标、路况信息等,实现系统的定位功能。

JTAG调试电路采用USB-JTAG调试模块,并嵌入到FPGA终端中,方便FPGA实现在线调试、数据下载和程序固化等功能。

2.6 嵌入式互联技术与FPGA终端创建

2.6.1 Socket CLIP与IP Node技术

Socket CLIP与知识产权集成节点(IP Integration Node,IP Node)是解决 LabVIEW FPGA 虚拟仪器(virtual instrument,VI)与底层物理芯片快速互联的关键技术,如图9所示。IP Node技术允许硬件描述语言 VHDL(very high speed IC hardware description language)代码直接与FPGAVI通信。Socket CLIP技术允许VHDL代码直接与FPGA VI通信及访问无法通过LabVIEW VI和函数访问的FPGA引脚。Socket CLIP与IP Node区别就是,它可以直接在底层和LabVIEW建立联系,直接调用IP读写FPGA的物理IO(输入输出)信号。所以根据芯片控制的复杂程度,DDR3内存芯片、千兆以太网等芯片的驱动程序采用Socket CLIP技术进行封装,CLIP底层可以看成是“先进先出(first in first out,FIFO)存储器逻辑+存储信息寄存器(memory-information register,MIG)控制器代码”。串行通信、A/D(模拟/数字)、D/A(数字/模拟)等控制电路相对简单的芯片采用IP Node技术进行封装。

图9 Socket CLIP与IP集成节点Fig.9 Socket CLIP and IP node

2.6.2 FPGA终端

本系统结合Socket CLIP封装技术,生成驱动程序包进行安装,能让LabVIEW开发平台识别到自主研发的FPGA硬件,并能在FPGA项目中创建FPGA终端。使用Socket CLIP技术封装的虚拟外部设备如图10(a)所示,其中KSZ_1 Data、KSZ_2 Data表示封装了双路千兆以太网外设,DDR Data表示封装DDR3存储器外设;它将外设与FPGA之间的物理引脚和时钟信号全部封装到CLIP内部,应用开发时,只需要将数据传输给CLIP或者从CLIP读取数据即可,无需关注外设本身的时钟和物理引脚。使用IP集成节点来封装AFE5801、UART、LM75、lPS25等外设IP核(Intellectual property core),这些封装好的外设极大地方便了整个系统的构建。它解决了LabVIEW软件与FPGA硬件间互联互通的关键技术问题,构建了LabVIEW与FPGA快速互连的软件桥梁。

图10 FPGA终端Fig.10 FPGAterminal

3 超声软件架构设计

软件数据流模型(图11)是软件架构设计的参考依据,其中A、B型显示、辅助判伤在上位机软件①中完成,线程②~⑨在下位机中完成。上、下位机之间通过千兆以太网通信,数据直达底层硬件,实时性更强。以下数据线程都运行在FPGA终端上:以太网通信线程②、DDR3线程③、编码器线程④、超声激励线程⑤、多路数据采集线程⑥、数字信号处理线程⑦、智能数据线程⑧、图像数据处理⑨,线程间采用高速且高效的FIFO交换数据。各线程的功能如下:以太网通信线程②是超声数据的主通信线程,上位机通过此线程完成数据、指令、参数的上传和下达,它通过FIFO1将上位机的“仿真数据、速度等级、通道参数、增益曲线、控制参数”信息传递到DDR3及FIFO2中;DDR3线程③、编码器线程④、激励线程⑤及数据采集线程⑥接受这些参数进行工作,数据采集线程⑥生产的数据通过FIFO4传递给数字信号处理线程⑦,经过FIR滤波、数字包络检波、A、B型显示数据处理之后通过FIFO5经由以太网线程②回传到上位机,在上位机进行A型和B型显示、伤损识别和存储。

图11 数据流Fig.11 Data flow

3.1 以太网通信线程②

以太网线程②是专门处理超声检测数据的线程,是底层电子系统的网络驱动程序,如图12所示。它采用Socket CLIP技术将整个千兆以太网双向收发UDP通信过程封装成CLIP组件,此组件在KSZ9031芯片输出的125 MHz时钟频率下工作,包含一个复位线程和一个通信线程。工作之前,把“FPGA_IP、PC_IP、FPGA_MAC、PC_Port、FPGA_Port”等参数传递给IP核,在isupdate信号上升沿更新IP核;启动以太网通信之后,IP核会把指定长度的“FIFO:数据上传”中的数据上传到上位机,并把上位机下达的“速度等级、通道参数、增益曲线、控制参数”等数据存到“FIFO1:指令参数”中。通过这两个FIFO,把数据再传递到下一级线程④~线程⑥中处理;还有一部分数据,如仿真数据,需要通过线程③存入到DDR3中;A、B型显示数据、里程数据、脉冲数据、智能数据等则通过FIFO5上传到上位机进行处理。所以以太网线程是上、下位机间数据的“高速公路”,负责两者间数据的上传和下达。

图12 千兆以太网线程Fig.12 Gigabit Ethernet software thread

3.2 DDR3读写线程③

封装后的DDR3内存使用非常方便,将DDR3的读和写都做成标准的4线握手制的CLIP组件(此组件包含一个复位线程和一个读写线程),DDR3线程的作用是满足大数据量的存储和缓冲。在写入指令的作用下,把“FIFO_DDR3_WR_Data”中的数据写入到指定长度、指定地址的DDR3中,如上位机的仿真数据存入DDR3中的过程及图像数据暂存DDR3的过程等;同理,在读取指令的作用下,将指定地址、指定长度的DDR3中的数据读入到FIFO_DDR3_RD_Data中,如仿真数据循环往复地从DDR3中读出来的过程。DDR3读写线程如图13所示。

图13 DDR3读写线程Fig.13 DDR3 read/write thread

3.3 编码器线程④

编码器脉冲是实现超声激励间隔、里程定位、各通道同步的基础。图14所示为编码器信号处理线程,具体如下:

图14 编码器线程Fig.14 Encoder thread

(1)通过对编码器A、B信号的边缘检测实现对脉冲计数和对激励的触发控制;

(2)对编码器A、B信号的正交特性进行检测可用于判断设备的行进方向;

(3)64位脉冲计数器用于使系统脉冲同步,通过计算转速、辅以轮径,可以算出绝对里程L=L0+2πR/3600 × P,其中L为里程,L0为初始里程,R为轮径,P为脉冲计数值。

3.4 超声波激励线程⑤

超声波的产生需要将高压脉冲[7]作用于压电晶片上。图15所示的8通道超声波激励线程,其作用是产生合适的激励脉冲,它通过软件将“保持时间、激发频率、激发延迟、通道使能信息”传递到“激励延时模块.ⅵ”和“TX7316脉冲发生模块.ⅵ”上,产生的激励脉冲通过FPGA的IO引脚输出,以驱动芯片TX7316产生高压脉冲。

图15 超声波激励线程Fig.15 Ultrasonic generation thread

3.5 多路数据采集线程⑥[8]

图16所示数据采集线程包含压控型增益控制VCA、时间增益控制TGC、AAF抗混叠滤波处理、模数转换ADC。模数转换前需要放大调理,回波信号经过低噪声运算放大器LNA后进入VCA压控增益放大。该环节通过AD7801控制AD605实现,通过软件控制“VCA”参数实现控制电压Vgn=0.0129×VCA的输出,以此控制两级串联放大器AD605;输出增益Gdb=40×Vgn-38,理论上可实现-28~68 dB增益范围输出。信号放大后进入AFE5801,内部完成时间增益补偿TGC、抗混叠滤波器AAF和模数转换器ADC 3大功能。由于此芯片引脚多且功能复杂,所以直接将底层Verilog驱动代码封装成IP核形式,采用IP集成节点调用。TGC、AAF功能通过FPGA的串行外设接口(serial peripheral interface,SPI)通信进行设置,用TGC功能进行声程补偿,用AAF功能进行片内模拟滤波,最后信号送到ADC进行模数转换。线程采用40 MHz时钟信号驱动;同时作为AD转换时钟,其最高频率可到65 MHz。IP核通过芯片的位时钟和帧时钟进行数据的串并转换,完成8通道串行数据的并行输出,在data_vaid指示有效的情况下输出8通道(ad_ch1~ad_ch8)的数据,并缓存到FIFO_CHx_AFE_Filter_16bit中,此8通道的FIFO数据又作为数字信号处理线程的数据输入传递到下一个处理线程。

图16 超声数据采集线程Fig.16 Ultrasonic data acquisition thread

3.6 数字信号处理线程⑦

数字信号处理线程⑦主要对模数转换后的数据进行数字信号处理,实现以下几个功能:有限长单位冲激响应(finite impulse response,FIR)数字滤波、包络检波和AB型数据处理。其中,FIR数字滤波器用于滤除超声波传感器特征频率以外的噪声信号,包络检波用于提取特征频率的包络,A、B型数据处理是根据包络计算A型显示的幅频特性和实现B型显示的成像。

3.6.1 数字滤波器设计[9]

基于“DFDT数字滤波器工具包”进行数字滤波器的设计。目前检测用的超声波频率有2.25 MHz和3.5 MHz两种。数字带通滤波器设计如图17所示,其带通范围为1.8~4 MHz,信号采样率40 MS/s,精度为16位,噪声抑制比为-40 dB。滤波器结构选型和系数量化见图18所示:选用FIR滤波器结构,16位量化系数,254阶系数生成于Coefficients Report中。对滤波器进行性能仿真(图19),向滤波器分别输入频率为3.5 MHz、2.25 MHz、1 MHz、5 MHz且幅度为±1V的正弦信号。可以看出:滤波器在频率为3.5 MHz、2.25 MHz(带通内)时幅度衰减很小;在频率为1 MHz、5 MHz时(通带外),幅度衰减很大,表明带通滤波性能良好,符合设计要求。滤波器代码输出如图20所示,可以看出,它是一种可以在FPGA单周期定时循环中运行的带通滤波器IP核,同时可以处理8通道数据。把此IP核移植到图21所示的数字信号处理线程中,则能同时处理8通道超声数据。

图17 数字带通滤波器设计Fig.17 Design of digital bandpass filter

图18 滤波器结构选型和系数量化Fig.18 Filter structure selection and coefficient quantization

图19 滤波器性能仿真Fig.19 Filter performance simulation

图20 LabVIEW FPGA滤波器代码输出Fig.20 LabVIEW FPGAfilter code output

图21 数字信号处理线程Fig.21 Digital signal processing thread

3.6.2 包络检波设计[10-11]

在脉冲反射式超声探伤研究中,常常采用高斯模型来表示回波特征:

式中:α—带宽因子;τ—到达时间;f—中心频率;φ—相位;β—幅度因子,βe-a(t-τ)2函数表征回波的幅度按照指数衰减规律进行变化。

超声回波的A型显示、时间计算都需用到包络信号。希尔伯特变换是信号包络提取的一种常用方法,其对超声回波信号fκ(t)求包络,首先对其进行Hilbert变换,得到合成信号然后对合成的信号取幅值y()t,此时y(t)就是回波信号的上包络。

利用数学模型生成超声回波信号,并进行Hilbert变换,算法如图22所示,包络提取效果如图23所示,包络特征的提取有利于后续的线程处理。

图22 超声波包络检波算法Fig.22 Algorithm of ultrasonic envelope detection

图23 超声波包络检波仿真结果Fig.23 Simulation results of ultrasonic envelope detection

3.6.3 A、B型显示数据处理

超声回波经过包络检波之后,进入“A_B显示数据处理.ⅵ”模块,经处理会得到3种重要数据:A型显示数据、B型显示数据、0度通道数据。如图24所示,A型显示数据和B型显示数据分别暂存于FIFO_UDP_U8H、FIFO_UDP_U8L中,其打包和上传任务在下位机完成,然后通过千兆以太网进行上传;0度通道的界面波数据是各通道回波传播时间计算的基础,即伤损埋藏深度计算依据。

图24 A、B型显示数据处理Fig.24 Processing ofAand B display data

3.7 智能数据处理线程⑧

智能数据线程1和线程2如图25所示,线程1是通过LM75型温度传感器芯片读取IP核、LPS25型压力传感器芯片读取IP核获得温度与压力数据,并存入相应的FIFO存储器中。线程2通过UART串口IP与北斗定位装置、运行监控装置、射频标签和远程键盘等连接,获得经纬度、公里标、路标、路况等数据信息并存入相应的FIFO6存储器中,最后通过以太网线程②将数据上传到上位机。这些数据可以提升系统的智能化水平和定位精度等。

图25 智能数据处理线程Fig.25 Intelligent data processing thread

线程2采用四线握手方式,其核心思想是将下一级的“输入就绪”通过反馈节点连接到前一级的“输出就绪”,通知前一级已经准备好了,可以接收新的数据;同样,如果前一级产生了有效数据,需要将“输出有效”接到下一级的“输入有效”,以便将有效数据传递过去。四线握手方式可以很好处理数据生产与数据消费之间的速率同步问题,在两者步调一致的情况下实现数据的最大吞吐率。

3.8 图像检测线程⑨

辅助判伤是上位机为超声识别的伤损提供图像辅证功能,图像数据采用千兆以太网通信。上位机通过以太网供电(power over Ethernet,POE)交换机从左右两路线扫摄像头中获得图像数据,跟上位机中的伤损识别数据进行同步存储,可以为用户提供800×600像素以下的图像,用于伤损特征的视觉辅助判别。

4 上位机A、B型显示处理

A型显示窗口、B型显示窗口是上位机人机显示的主要窗口。超声波A型显示在检测过程有着十分重要的作用,其可以提供激励信号、界面波信号、伤损回波、底面回波、闸门、幅度信息、增益变化及噪声等信号的观测窗口,为参数调整提供参考依据。如图26所示,本系统采用软件显示方式实现A型显示窗口,优点是便于A型显示数据的存储及回放。其实现原理把一帧经过包络检波的超声回波声程数据,辅以闸门宽度、延时等信息后,以幅度时间坐标系进行显示。

图26 超声波A型显示Fig.26 Ultrasonic A-scan

超声波B型显示数据是在系统空间转换和伤损识别后的图形数据,再配上定位公里标、路况及路标等辅助信息,在上位机检测软件中显示。同时,系统根据多通道超声伤损特征自动识别伤损类型,以不同的伤损图标提示,图27示出B型显示的主要特征,图28示出真实检测的B型数据,检测人员从这些多通道组合的图形数据中进行分析、判读和伤损定位。

图27 超声波B型显示Fig.27 Ultrasonic B-scan

图28 现场运用中的超声波B型显示Fig.28 Ultrasonic B-scan in field application

5 结语

通过工程应用与实验证明,基于FPGA搭建的系统硬件架构不仅能满足了超声系统在多通道、并行、高速和大吞吐率应用中的要求,还降低了硬件成本和PCB的布线面积。基于LabVIEW完成底层软件算法设计,编译生成目标电路并部署到自主研发的FPGA硬件构架上。两者的融合为电子系统设计提供了一套新的开发方法,其既发挥了LabVIEW在算法和图形编程上的优势,又发挥了自主研发的FPGA硬件在功能和成本方面的突出特点:

(1)此架构能在一块标准6U插件的PCB板上用“1片FPGA+4片AFE5801”就能实现32通道的超声波数据采集通路,相比之前需要用4块6U插件才能实现的架构,可降低硬件成本60%左右,集成度增加50%以上;

(2)基于LabVIEW搭建底层软件架构,其在构建并行特性、多线程、实时性、图形编程和FIFO数据传递方面有先天优势;

(3)结合“Socket CLIP封装技术、IP集成节点技术”的灵活运用可实现软硬件间的互联互通;

(4)标准四线握手编程与FIFO应用既方便了线程间数据的交换,又实现不同时钟频率下数据速率的同步;

(5)采用定时循环构建的并行线程,程序结构清晰,易读易懂,既提高了软件的开发效率,又能提高软件后续的升级及移植的效率,开发实例表明基于数据流的图形编程和多线程的并行架构设计可以提升固件约60%的开发效率和约40%的代码移植效率。

目前,利用此架构设计的超声波探伤数据处理系统具有32个通道的超声波信号处理能力。随着探伤技术的发展,会出现64通道、128通道、256通道等更多通道的超声波探伤技术的应用环境,包括相控阵应用领域,因此,需要规划更多通道、更宽数据带宽、更大数据吞吐率的平台架构,以适应未来探伤产业的发展。