宽频率范围的单子带压控振荡器设计

张 博,蔡林钰,吴昊谦

(西安邮电大学 电子工程学院,陕西 西安 710121)

第五代移动通信技术(5G)是近几年研究的热点,在5G 通信的实现过程中,射频前端系统发挥着重要的作用。锁相环作为射频前端系统中的重要模块,对射频收发机的性能有着很大的影响。压控振荡器(VCO)作为锁相环的重要组成部分,其性能的优劣对锁相环乃至整个射频收发机都有着重要影响。低相位噪声与宽频率范围是压控振荡器的设计难点,如果本振信号的相位噪声较差,则会增加通信中的误码率,影响载频的跟踪精度。同时,相位噪声还会影响通信接收机信道内、外性能测量。相位噪声越好,接收机的选择性和灵敏度也越好。文献[1]基于TSMC 180 nm CMOS 工艺设计了一款频率范围为3.26~5.27 GHz的VCO,其采用交叉互补耦合结构,应用6 位开关电容阵列实现了宽的调谐范围,但多位开关电容阵列会加速恶化相位噪声性能。文献[2]基于GF 65 nm 工艺,设计了一款应用于毫米波段的VCO,工作频率为137.87~162.34 GHz,其采用开关电感阵列来实现宽的频率范围,但由于振荡频率较高,且频率范围与相位噪声之间未能最佳折衷,其相位噪声性能为-86.63 dBc/Hz@1 MHz。文献[3]基于TSMC 40 nm CMOS 工艺,通过设计改进型开关电容阵列、高Q值谐振回路等方式实现了2.65~3.84 GHz 的宽频率范围VCO,并对芯片版图进行优化,实现了小的版图面积,但牺牲了相位噪声性能,中心频率处的相位噪声为-109.71 dBc/Hz@1 MHz。文献[4]提出的新结构VCO 只需较少的外部偏置可产生较高的跨导,因此功耗更低,相位噪声性能也较好,但输出频率范围为2.38~2.52 GHz,应用范围较小。因此,如何在宽的频率范围与低相位噪声之间折衷成为近年来VCO 的研究热点。

基于硅基的CMOS 工艺中,片上变容二极管的电容电压变化范围相对有限,使得传统的CMOS 工艺VCO 通常采用开关电容阵列或开关电感阵列的方式来实现宽频率范围[1-3,5-8]。以上学者已有研究成果大多采用开关电容阵列或开关电感阵列实现宽的频率范围,但此时VCO 输出频率曲线不再是单一的频率曲线,而是由多条频率子带交叠构成。这种情况下,应用于锁相环频率综合器的VCO 往往需要自动频率校准(AFC)技术来选取所需要的VCO 子带。这种方式极大地增加了整个锁相环的锁定时间[9],同时增大了芯片面积。因此,在一些对跳频切换有严格要求的系统应用中,采用开关电容阵列形式的VCO 难以得到应用。相较于多频率子带的VCO,单子带VCO 无需配置AFC 进行VCO 子带的选取,极大缩小了应用于锁相环频率综合器的锁定时间。

本文利用双平衡吉尔伯特混频器的差分输入输出特性,将定频率3 GHz VCO 与单子带5~6 GHz VCO进行下混频,得到的2~3 GHz VCO 不仅展宽了相对带宽,而且提高了相位噪声性能。

1 宽频率范围的单频率子带VCO 设计

1.1 总体电路结构

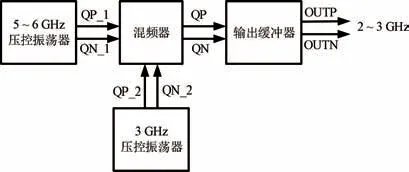

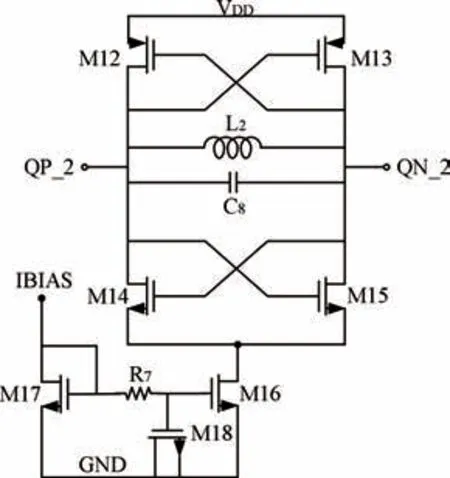

本文提出的宽频率范围单子带VCO 的电路结构框图如图1 所示,其中包括一个5~6 GHz 的单子带压控振荡器,一个固定频率为3 GHz 的压控振荡器,一个双平衡吉尔伯特结构混频器,一个输出缓冲器。其中5~6 GHz 的单子带压控振荡器差分输出信号QP_1、QN_1 连接混频器的一对差分输入端,固定频率的3 GHz 压控振荡器的差分输出信号QP_2、QN_2 连接混频器的另一对差分输入端。混频器的差分输出信号QP、QN 连接输出缓冲器的差分输入端,最终的输出信号OUTP、OUTN 通过输出缓冲器的差分输出端输出。通过将5~6 GHz 的单子带压控振荡器与固定频率的3 GHz 压控振荡器进行混频,可输出2~3 GHz 的振荡信号,可以看出,输出信号的相对带宽从18.2%(5~6 GHz)提高为40%(2~3 GHz),相对带宽极大提升。其中,相对带宽的计算公式为:

图1 总体电路结构Fig.1 Overall circuit structure

式中:B为相对带宽;fmax、fmin分别为最大频率和最小频率。

1.2 5~6 GHz 压控振荡器设计

图2 为本文设计的5~6 GHz 单子带压控振荡器电路结构。VCO 的品质因数主要由谐振腔中的电感决定,而由于工艺限制,谐振腔中的电感产生的品质因数通常很低,需要更高的负阻来抵消谐振回路中的寄生阻抗。换句话说,需要更优的起振条件,因此核心电路采用互补交叉耦合结构,相比于NMOS 交叉耦合结构[4,8],互补交叉耦合结构更容易满足起振条件,能够有效降低相位噪声,同时实现输出波形上升时间与下降时间的对称性[10-12]。电感L1、固定电容C1~C5、可变电容Cv1~Cv4共同构成振荡器的谐振网络,决定振荡器的工作频率范围。固定电容C1~C4、可变电容Cv1~Cv4与偏置电阻R1~R4共同构成可变电容的并联形式,可以提高调谐曲线的线性度,拓宽压控振荡器的输出频率调谐范围[13-15],在变容二极管两端加入固定电容C1~C4既用作隔直,也可将可变电容的调谐范围控制在最优范围之间。Vb1、Vb2为偏置电压,Vtune为调谐电压,两者一起控制可变电容的端口电压,调节输出频率范围。晶体管M6 作为尾电流管,为整个电路提供核心电流。M5、M6 构成电流镜,等比例放大基准电流。R5与MOS 管M7 构成一个低通滤波器,抑制电流源上的交流抖动。隔直电容C6、反馈电阻R6和晶体管M8、M9 构成一级输出缓冲器,与隔直电容C7、反馈电阻R7、晶体管M10、M11 共同构成一路差分输出缓冲器电路,通过反馈电阻R6、R7,能够实现输出信号轨对轨传输。输出缓冲器能够有效抑制后级电路的频率偏移所引起的对振荡器核心电路相位噪声的影响,驱动振荡器的差分输出信号为混频器的理想输入信号[3]。

图2 5~6 GHz 压控振荡器电路结构Fig.2 5~6 GHz voltage-controlled oscillator circuit structure

相位噪声是衡量压控振荡器性能的一项重要指标,根据相位噪声模型可知,在偏离载波频率较远处,相位噪声可表示为:

式中:Δω为频率偏移量;Q为谐振回路带载时的品质因数;K为玻尔兹曼常数;T为热力学温度;Psig为信号能量;ω0为振荡频率。根据式(2),可通过提高振荡信号的幅度来增加信号能量Psig,从而降低相位噪声。

另外可通过提高谐振回路的品质因数Qtot来降低相位噪声,其表达式为:

式中:Qtot为整体谐振回路的品质因数表达式;QL为谐振腔中电感支路的品质因数;C为谐振腔中固定电容的容值;Cvar为谐振腔中变容二极管的容值;QC,var为变容二极管支路的品质因数。片上可变电容的品质因数要比片上电感的品质因数大很多[11],因此谐振回路中的品质因数主要由片上电感决定,在设计时尽量使用高Q值的电感,或对谐振腔电感进行优化设计。

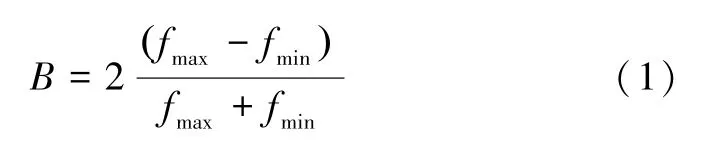

1.3 3 GHz 定频率压控振荡器设计

固定频率的3 GHz 压控振荡器电路结构如图3,其同样采用互补交叉耦合结构,可有效降低相位噪声,晶体管M12、M13、M14 和M15 构成负阻,用于抵消谐振网络的阻抗损耗,达到起振条件。电感L2与电容C8构成谐振网络,振荡在3 GHz 定频处。R7与晶体管M18 构成的低通滤波器抑制电流源上的交流抖动。

图3 定频率3 GHz 压控振荡器电路结构Fig.3 Fixed frequency 3 GHz voltage-controlled oscillator circuit structur

1.4 混频器设计

有源混频器可以看作电压/电流转换器、电流开关器和电流/电压转换器的组合[16]。混频器电路结构如图4。由于压控振荡器输出差分信号,因此混频器需采用双平衡吉尔伯特结构,相比于单平衡结构,双平衡结构对LO 信号的噪声抑制更好。M20 与M21 分别作为跨导放大电路,对输入的差分信号QP_2、QN_2进行放大,同时可看作电压/电流转换器,将输入的射频电压转换为射频电流。差分开关对管M22 与M23,M24 与M25 轮流导通,将电流传输至两边支路上,电流通过负载电阻R10、R11产生输出电压,把中频电流转换为中频电压信号,最终实现混频功能。偏置电阻R8、电容C9构成偏置电路,对固定频压控振荡器的输出信号QP_2 进行有效衰减,来满足混频器的输入三阶交调点IIP3,从而有效抑制三阶交调信号对输入信号的干扰。晶体管M19 作为尾电流管,提供整个电路的核心电流。

图4 混频器电路结构Fig.4 Mixer circuit structure

1.5 输出缓冲器设计

输出缓冲器的电路结构如图5 所示,采用差分共源极放大结构,能够驱动下级电路同时实现较好隔离作用。通过设计合理的带宽,可有效抑制频带外的谐波分量。M26、M27 为放大管,对混频器输出的中频信号进行放大,R12、R13为负载电阻,M28 作为尾电流管,提供整个电路的核心电流。

图5 输出缓冲器电路结构Fig.5 Output buffer circuit structure

2 结果与讨论

2.1 流片结果

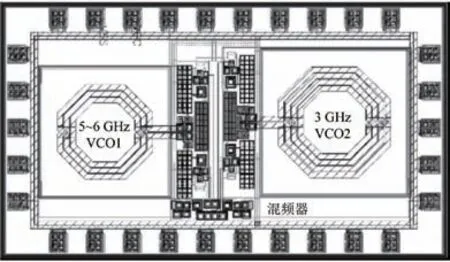

本次设计采用TSMC 180 nm 工艺进行仿真设计与流片测试验证。芯片版图如图6 所示。考虑到合理布局版图使其面积最小化,两个VCO 呈对称分布,中间为混频器及输出缓冲器。芯片照片如图7 所示,尺寸为1.2 mm×0.7 mm (含焊盘)。

图6 芯片版图Fig.6 Layout of the chip

图7 芯片照片Fig.7 Photograph of the chip

2.2 测试与结果分析

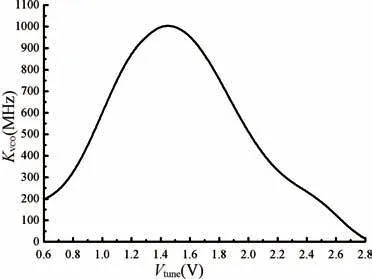

利用FSWP 频谱分析仪进行测试,该频谱仪的测试范围为1 MHz~26.5 GHz。测试表明,调谐电压在0.6~2.8 V 变化范围内,得到压控振荡器的输出频率范围如图8 所示,压控振荡器的输出频率为1.85~3 GHz,满足设计指标的2~3 GHz;灵敏度(KVCO) 如图9 所示,最高灵敏度为1000 MHz/V;输出功率如图10 所示,可以看出,输出功率整体较低,为-10~-4 dBm。这是由于混频器及后级输出缓冲器等模块电路的设计对芯片整体性能的影响,另外,测试中信号线存在差损也会降低输出功率。2 GHz 处压控振荡器的相位噪声性能如图11 所示,分别为-73 dBc/Hz@ 10 kHz,-99 dBc/Hz@ 100 kHz 和-123.2 dBc/Hz@ 1 MHz。对比仿真结果,仿真时2 GHz 处相位噪声为-128 dBc/Hz@1 MHz,实际芯片测试恶化4 dB,这是由于流片后电路实际的品质因数降低,造成相位噪声的性能下降。

图8 压控振荡器的输出频率范围Fig.8 Output frequency range of VCO

图9 压控振荡器的调谐灵敏度Fig.9 Tuning sensitivity of VCO

图10 压控振荡器的输出功率Fig.10 Output power of VCO

图11 2 GHz 处压控振荡器的相位噪声Fig.11 Phase noise of VCO at 2 GHz

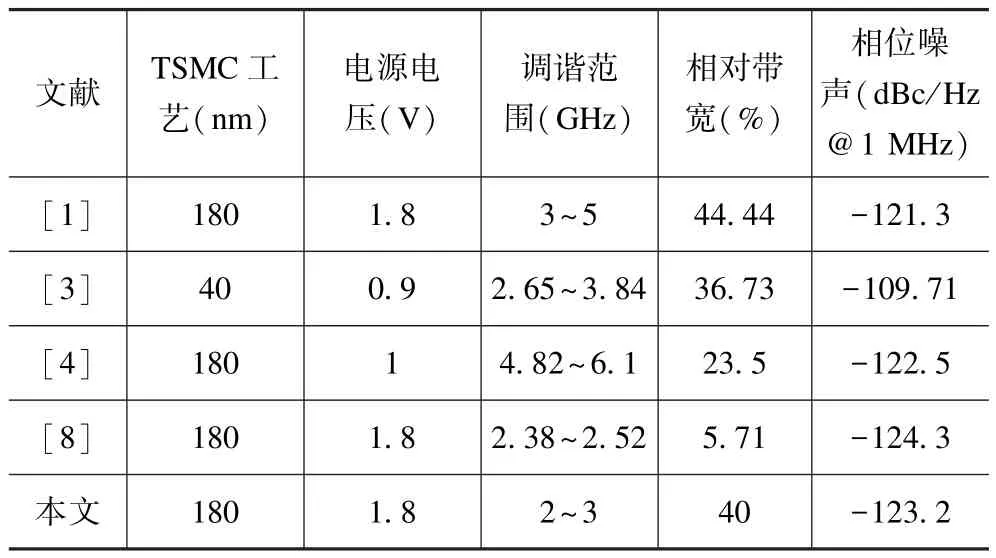

1.8 V 电源电压条件下,本设计压控振荡器的几项关键指标与其他已报道文献对比结果如表1 所示。可以看出,本文设计的单子带压控振荡器相对带宽为40%,相较于其他文献具有更宽的相对带宽。在同种工艺条件下,2 GHz 处的芯片实测相位噪声为-123.2 dBc/Hz@1 MHz,与其他文献芯片实测结果相比具有更低的相位噪声性能。

表1 本设计与其他文献设计方法测试对比结果Tab.1 Test comparison results between this design and other design methods

3 结论

本文设计并实现了一种宽频率范围的单子带压控振荡器芯片,采用TSMC 180 nm 工艺,通过双平衡吉尔伯特混频器的差分输入与差分输出特性,实现单子带5~6 GHz 压控振荡器与定频率3 GHz 压控振荡器的下混频,最终输出2~3 GHz 单子带频率范围。测试结果表明,在相同工艺下,与其他已报道相关文献相比,本设计的压控振荡器在保证宽频率范围的基础上,达到了较优的相位噪声性能:相对带宽从18.18%展宽至40%,2 GHz 频点处相位噪声为-123.2 dBc/Hz@1 MHz。

此外,通过双平衡吉尔伯特结构混频器,可固定一端差分输入为5~6 GHz 单子带压控振荡器的差分输出,而另一差分输入端可连接任意固定频率压控振荡器,在工艺允许的频率范围内通过混频可实现任意需求的宽频率范围单子带压控振荡器。