SiCMOSFET栅极驱动电路研究综述*

周泽坤,曹建文,张志坚,张 波

(电子科技大学功率集成技术实验室,成都 610054)

1 引言

随着5G、智能汽车、电力电子的高速发展,高压、高频的应用越来越广泛,大功率、高效能、高速度的性能需求也日益急切。作为高压和大功率电子产品及电力电子应用中的基础部件,高压功率器件对产品的性能有着显著影响[1]。以碳化硅(SiC)和氮化镓(GaN)为代表的第三代宽禁带半导体材料,凭借着自身寄生效应小、导通电阻低、功率密度高以及耐高压能力好等特点,逐渐成为高性能功率器件的良好制造材料[2]。SiC MOSFET的正常工作电压能达到1200 V以上,广泛应用在高压、高速和大功率领域。

SiC MOSFET有很多优点,例如导通电阻小、导热性好、电子迁移率高,使得采用SiC MOSFET的电子产品在体积、散热、能量损耗等方面具有很大优势[1-2]。因此,SiC MOSFET可极大地提升高压电子产品的性能。相较于Si MOSFET,SiC MOSFET的寄生电容较小、击穿电场较大,能够实现更快的开关速度和更高的开关频率。因此,SiC MOSFET常应用于高压高速开关应用中,有助于电子电力系统能效的提升。但是,高速的开关瞬态会带来很大的dv/dt和di/dt,与之相伴的将是高电磁干扰(Electro-Magnetic Interference,EMI)噪声,这对电子系统非常不利[3];大的dv/dt也会在SiC MOSFET的栅极引入串扰,影响功率器件的工作稳定性[4]。由于SiC MOSFET的寄生电容较小,对于功率回路中的寄生电感更加敏感,在开关瞬态容易产生振荡,影响器件的开关性能[5]。这些高速高压大功率应用中的问题都成为研究者关注的热点。

为了应对高速高压应用中的问题,作为SiC MOSFET的控制器,驱动电路的设计与研究主要致力于优化SiC MOSFET的开关性能[6-14]、减小开关过程中的串扰和振荡[15-16]、提升SiC MOSFET的开关速度[17-22]、降低EMI噪声[23-25]以及短路保护[26-28]等。

本文介绍了SiC MOSFET的部分基础知识,对SiC MOSFET的PCB板级栅驱动器技术进行了总结、分类和分析,讨论了SiC MOSFET驱动设计技术的实现,并给出了SiC MOSFET栅极驱动器设计的考虑。

2 SiC MOSFET栅极驱动器的研究现状与分析

SiC MOSFET在高压大功率的应用中常常以半桥结构和模组形式出现,为了发挥SiC MOSFET的高耐压性能,SiC MOSFET的驱动研究大多以母线电压为1200 V的应用为背景,而现有的BCD集成电路工艺中能产业化使用的集成高压耐压器件的耐压仅为700 V左右,因此目前几乎没有针对高压半桥所需的双通道SiC MOSFET驱动芯片设计的深入研究,大多数研究仍围绕单个SiC MOSFET的驱动展开。

SiC MOSFET以模组形式出现时,常常是为了实现更高的耐压能力,通过串联多个SiC MOSFET以实现更高的耐压。2个串联SiC MOSFET的结构如图1所示,通过2个驱动芯片分别对功率管进行驱动控制。由于串联功率管的寄生电容之间的差异以及驱动器关断时间的匹配等问题,在关断过程中容易出现2个功率管的漏源电压(Vds)不平衡的问题[29]。文献[30-31]针对2个SiC MOSFET串联形成模组的电压平衡问题进行了有源栅驱动架构的设计,针对模组关断过程中存在的漏源电压不平衡从而损害MOSFET的问题进行了特定设计。文献[30]采用动态电压分享的方式来实现电压平衡控制,合理地动态降低更高侧管的关断速度,从而实现电压的平衡控制,文献[31]采用反馈控制的方式来调节2个串联管中低侧MOSFET的栅极电压,控制漏源电压变化速率,从而实现2个SiC MOSFET漏源电压的动态平衡。

图1 串联SiC MOSFET电路结构

由于半桥应用下的SiC MOSFET和模组形式的SiC MOSFET均需要单个SiC MOSFET的驱动芯片,所以目前SiC MOSFET驱动方面的学术研究大多为单个SiC MOSFET驱动技术的研究。因此本文主要对单个SiC MOSFET栅极驱动器进行介绍和讨论,并结合半桥应用环境进行论述。

2.1 SiC MOSFET驱动电路的基本要求及原理

在高压大功率应用中,硅基材料所需耐压越高,外延层掺杂浓度越小、漂移区长度越长,导致其单位面积导通电阻越大。几种半导体材料的性能对比如表1所示,与传统的Si MOSFET相比,SiC MOSFET作为宽禁带半导体器件,由于禁带宽度是硅基的3倍左右,具有更高的绝缘击穿电场,所以相对于硅基的高压功率管而言,在实现相同耐压的情况下,SiC MOSFET的导通电阻更小;因此在实现相同耐压、相同导通电阻的情况下,SiC MOSFET的尺寸远小于Si MOSFET,从而使栅极等效寄生电容以及结电容变小。因此SiC MOSFET适用于高压高频应用。

表1 几种半导体材料的性能对比

由于SiC MOSFET在栅源电压Vgs为0 V时对应的栅极电荷QG不为0,然而完全关断SiC MOSFET则需要抽离它的栅极电荷QG,因此采用一般的0 V关断模式无法完全关断功率管。对于SiC MOSFET而言需要采用负压来关断功率管,保证它能从开启状态完全转换到关断状态。

SiCMOSFET和Si CoolMOS的转移函数曲线如图2所示,SiC MOSFET的跨导明显小于Si CoolMOS[32],因此在实现相同沟道电流的情况下,SiC MOSFET所需的Vgs更大,这也说明SiC MOSFET的密勒平台电压更高,通常在8~10 V。因此,对于SiC MOSFET而言,传统Si MOSFET的5 V开态驱动电压远远不够。现在市面上的SiCMOSFET正向耐受电压通常在25 V左右,而越高的开态Vgs将实现越小的导通电阻RON,从而减小导通损耗。因此SiC MOSFET的开态VDD通常推荐为18~20 V。

图2 SiC MOSFET和Si CoolMOS的转移特性曲线[32]

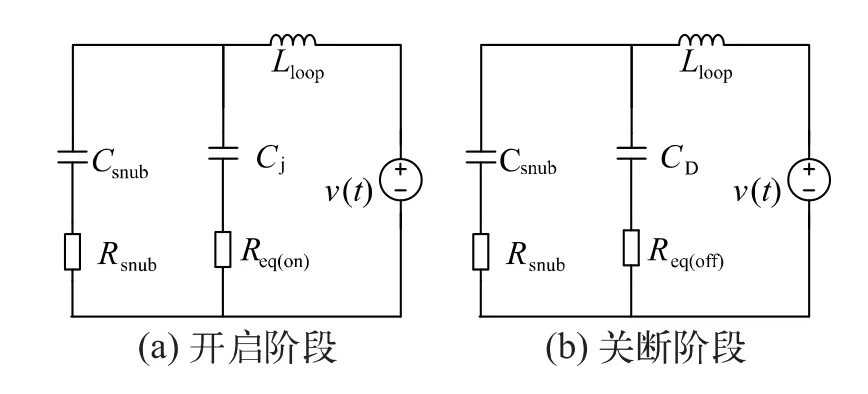

SiC MOSFET的开关瞬态和一般硅基功率管的开关瞬态类似,除了VDD为18~20 V、关断电压VEE为负压以外,密勒平台也有些不同,在密勒平台期间Vgs仍然以一定斜率上升,并不是完全呈现为栅源电压不变化。单个SiC MOSFET的驱动结构及开关瞬态波形如图3所示,SiC功率管的开关瞬态可以简化为对电容的充电、放电过程。在开启过程中,通过对栅极寄生电容充电,在充电的过程中Vgs逐渐增大;当Vgs达到密勒平台电压Vmiller后,Vgs几乎维持不变,功率管的Vds开始降低;当Vds的下降阶段结束后,Vgs将继续充电,直至Vgs充电至VDD,将功率管完全开启。在关断过程中,通过对栅极寄生电容放电,在放电过程中Vgs逐渐减小;当Vgs接近Vmiller后,Vgs几乎维持不变,功率管的Vds开始增大;当Vds的上升阶段结束后,Vgs将继续放电,直至Vgs充电至VEE,将功率管完全关断。

图3 单个SiC MOSFET的驱动结构及开关瞬态波形

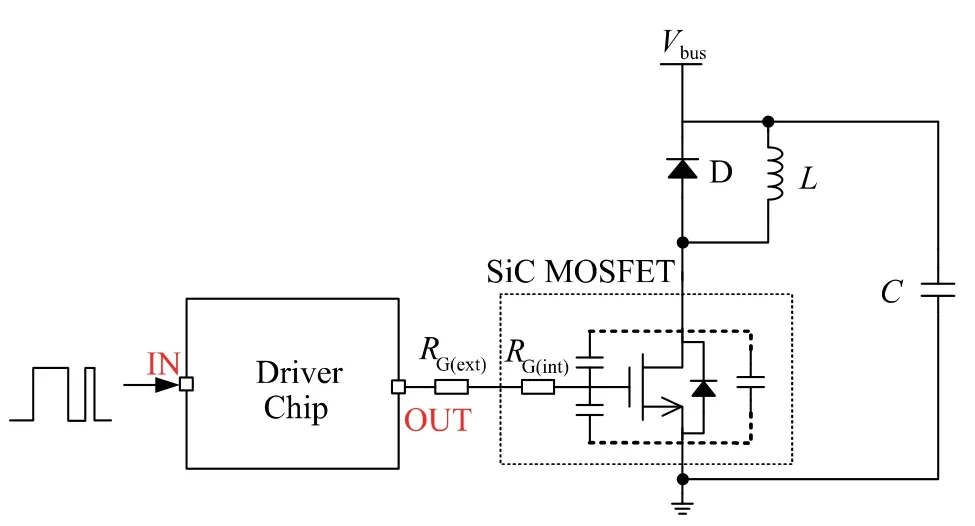

业界通常采用双脉冲测试电路对SiC MOSFET开关瞬态进行测试,来考量SiC MOSFET在实际电路应用中的性能和表现。为了体现实际应用中的开关性能,母线电压Vbus常常为800~1200 V,如果不采用DC-DC控制架构稳定电感每周期的充放电过程,电感L的电流将易烧毁功率管和测试板。双脉冲测试电路的工作原理简单,避免了测试板复杂的搭建过程,降低了高压大功率损坏测试板的风险,只对需要测试的SiC MOSFET进行2次开关动作,模拟实际应用中的负载电流,双脉冲测试电路如图4所示。通过合理设置第一个脉冲的宽度来设置电感L中的电流Iload,再采用第二个窄脉冲来抓取SiC MOSFET的开启和关断的瞬态波形,从而对驱动芯片实现的效果进行测试和分析。

图4 SiC MOSFET的双脉冲测试电路

其中Iload为所需要模拟的负载电流,tpulse1为第一个脉冲的宽度。因此根据需要合理选择电感和第一个脉冲宽度,即可模拟实际应用的开关瞬态。

2.2 SiC MOSFET驱动电路的分类与总结

SiC MOSFET驱动技术分类如图5所示,大致分为3类:电压源型驱动、电流源型驱动以及相关的保护电路和可靠性提升电路。每种类型的驱动结构都包含有不同的设计方案,每种方案的产生都是为了解决对应的问题以提升SiC MOSFET的开关性能。

图5 SiC MOSFET驱动技术的分类

2.2.1 电压源型驱动

电压源型的驱动技术较为常见,简单的电压源型驱动结构如图6所示,通过开关控制SiC MOSFET栅极电容的充放电方向,在S1闭合、S2断开的阶段,通过VDD、栅极电阻和栅极寄生电容形成暂态响应,栅源电压逐渐充电至VDD,实现开启过程;在S2闭合、S1断开的阶段,通过VEE、栅极电阻和栅极寄生电容形成暂态响应,栅源电压逐渐放电至VEE,实现关断过程。

图6 电压源型驱动结构

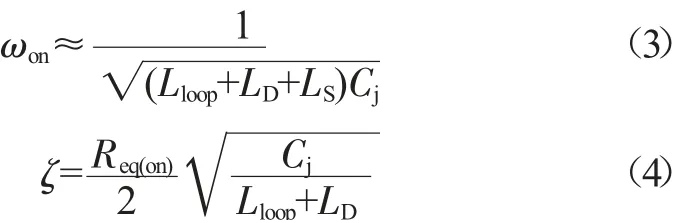

如果单从电路拓扑图和栅极回路的简化等效电路来看,开关瞬态类似于一个一阶RC暂态响应,但是实际上SiC MOSFET的寄生参数中不仅包含寄生电阻还包含寄生电感,在栅极、源极和漏极均存在寄生电感LG、LS、LD,这些寄生电感的存在将使开关瞬态等效为二阶暂态响应。文献[25]针对双脉冲测试电路中开关瞬态下的寄生效应进行了等效,将开启和关断过程中的阻抗进行了等效和分析,功率回路等效电路如图7所示,对于开关瞬态的Vds和漏端电流Id而言,最终的等效电路为RLC串联电路。

图7 双脉冲测试电路的等效电路

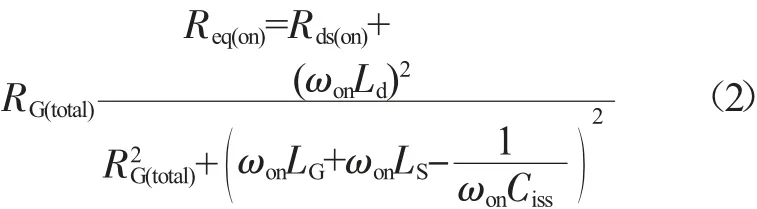

开启瞬态RLC的等效电阻Req(on)为:

其中Rds(on)为导通时的漏源电阻,RG(total)为栅极的电阻之和,Ciss是SiC MOSFET的Cgs和Cgd之和,ωon是开启瞬态RLC的谐振频率,ζ是阻尼系数,Lloop是功率回路中的等效电感。

关断瞬态RLC的等效电阻Req(off)为:

其中ωoff是关断瞬态RLC的谐振频率。

针对Vds和Id的振铃问题,文献[25]提出了并联一个RC缓冲器的设计思路,在电感L回路的左端和地之间并联一个RC串联支路,其等效电路如图8所示,整个系统成为3阶瞬态响应,选择合适的Rsnub和Csnub,三阶系统从阻尼状态变为临界阻尼状态或过阻尼状态,使其特征方程有多个实根,从而抑制开关瞬态中Vds和Id的振铃。但这种方法参数选取的计算复杂,不同应用环境下对于RC缓冲器的参数选择不同,对于应用变化或者器件更换的适用性不强。

图8 增加RC缓冲器后双脉冲测试电路的等效电路[25]

为了能够应对应用场景变化、器件类型更换等导致的功率回路和栅极回路的电容、电感参数的变化,有源驱动逐渐被提出。有源驱动主要是通过有针对性地调整开关瞬态中某一阶段的驱动速度,降低这一阶段功率管栅极寄生电容充放电的速度,避免di/dt或dv/dt过大;在其他阶段增大驱动速度,进而不明显增加开关延时。与传统的驱动速度相比,有源栅驱动的主动干预性更强、灵活性更好。

有源驱动可以按照控制方式大致分为数字分段控制和模拟闭环控制两类。模拟闭环控制方式是指实时获取SiC MOSFET的电压、电流信息,基于反馈信息在模拟电路负反馈环的作用下形成闭环控制,功率管的电压电流信息可以实时调节驱动能力,实现自适应调节。由于SiC MOSFET的开关速度很快,在数十纳秒级别,采用模拟闭环的方式对于环路带宽的要求很高,要求环路带宽在几十兆赫兹及以上,对于电压型控制环路而言比较难实现,因此现在对于电压型模拟电路闭环控制架构的研究比较少。数字分段控制包含多电阻分段控制和多电平分段控制两大类,都是基于检测电路得到的反馈信息对开关瞬态进行分段处理,不同阶段采用不同驱动能力来驱动功率管,分段控制的有源驱动拓扑结构如图9所示。

图9 分段控制的有源驱动拓扑结构

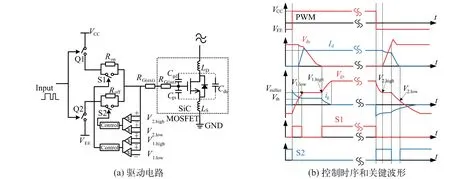

文献[6]提出的一种变电阻的有源驱动电路见图10(a),其采用传统的电压型驱动架构,动态调控栅极充电电流,减小了电压过冲和电流过冲。控制时序和关键波形见图10(b),就开启阶段而言,在Vgs达到比较点电压后,此时还没到达密勒平台,通过增大栅极电阻来减小开启阶段的di/dt和dv/dt;当Vgs超过密勒平台后,再转换为较小的栅极电阻,从而加快完全开启的过程;就关断阶段而言,当Vgs降低至密勒平台后,通过增大栅极电阻来减小关断阶段的di/dt,当Vgs小于阈值电压后再采用较小的栅极电阻,加快关断瞬态的进程。合理设置好窗口比较器的阈值,能够有效减小di/dt和dv/dt,控制EMI以及电压和电流过冲。

图10 变电阻的有源驱动电路[6]

这类有源驱动方式结合了栅极电压的反馈信息,动态控制栅极电阻,主动调节不同阶段的栅极电流,改变栅极寄生电容的充电速度,实现di/dt和dv/dt的降低。文献[24]采用了另一种降低di/dt的方法,在漏极电流上升和下降的阶段通过电压注入的方式,降低漏极电流Id的变化速度,从而实现对di/dt的主动调节。

电压型有源栅驱动的架构除了通过调节栅极电阻或者注入电压的方式之外,还有采用多驱动电平的方式。文献[7]通过20 V和5 V双电源的方式实现了板级上的多电平有源驱动,在不同阶段对功率管栅极和源极施加不同电压,实现4种栅源驱动电压的组合,从而调节各个阶段的栅极电容充电速度。文献[7]采用了3个高速比较器用于检测功率管的漏极电流Id和漏源电压Vds,并且利用限幅电路来保证比较器的输入信号在一个安全范围内。它的控制器是一个复杂的数字可编程单元,结合反馈信息最终控制4个开关的开启和关断时序,实现预期想要的分段控制效果,多驱动电平的有源驱动电路如图11(a)所示,控制时序和关键波形如图11(b)所示。这种多电平控制方案一般只适用于PCB板级驱动电路,因为S3、S4的5 V供电电压需要具备承受较大电流里灌的能力,一般只能在板级设计里利用变压器实现,而常规的片内5 V电源轨不具备承受被灌大电流的能力。因此这种架构比较难实现片内全集成,难以朝着小型化方向改进,占用空间较大。

图11 多驱动电平的有源驱动电路[7]

文献[10]则采用多级驱动器串联的方式,第一级驱动器的输出作为第二级驱动器的地电位,第二级驱动器的输出作为第三级驱动器的地,最后在3级驱动器的供电电压之间形成多种组合,在3个驱动器的输入信号时序的叠加下,能够实现多电平驱动功能。这种结构现在也只在板级设计中实现,因耗用驱动芯片和面积较大,需要多个电源。文献[12]则提出了利用可调的LDO来辅助驱动,在常规的驱动架构下,增加可调的LDO,为开关瞬态中di/dt及电压过冲的阶段内提供第3个驱动电平Vint,从而实现3电平驱动。和常规驱动不同的是采用了2个开关控制信号控制2组驱动级,使驱动电压在3个电压之间进行选择。文献[12]还对第3个电平Vint的取值以及负载电流对dv/dt和能量损耗的影响进行了计算和分析,最后指出,负载电流越小,dv/dt越小;Vint越大,dv/dt也越小。

2.2.2 电流源型驱动

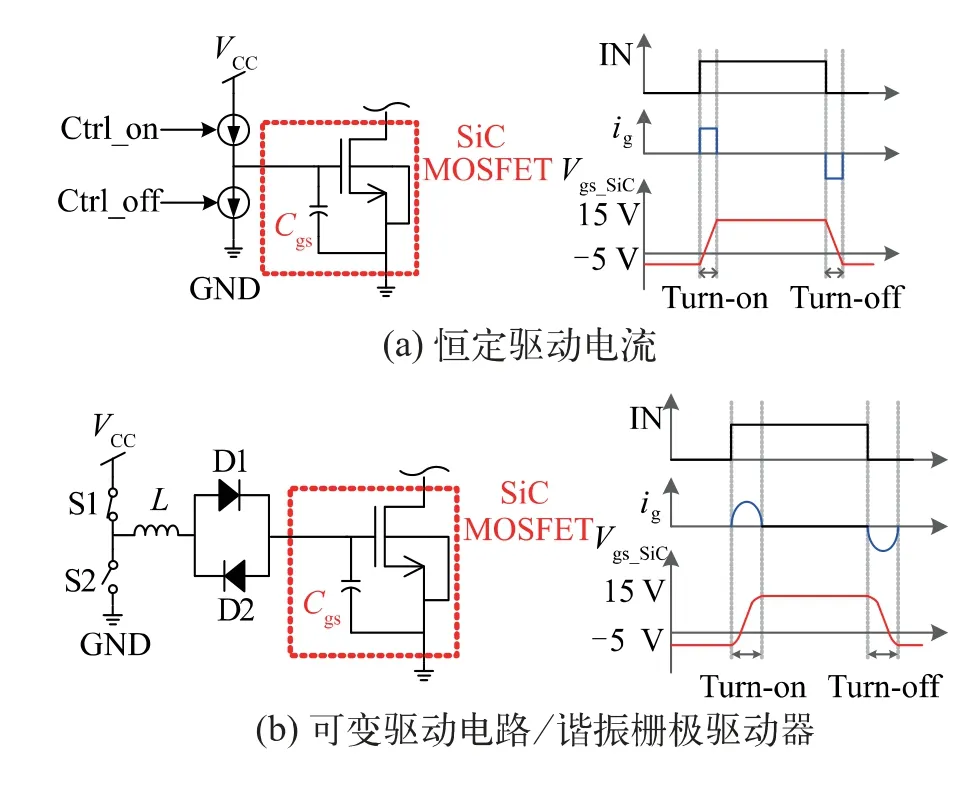

电流源栅极驱动器不需要使用额外的栅极电阻,这不仅大大简化了SiC MOSFET的栅极回路,还带来了2个优势。首先,可以尽可能减少开关的能量损失,其次,可以加速开关操作,使其更适合高频应用[18-20]。电流源栅极驱动器的2种基本结构如图12所示。图12(a)中使用脉冲驱动电流,电流值在开关操作期间是恒定的[15,17]。在图12(b)中,SiC MOSFET的导通和关断由电感L上提供的ig控制,驱动电流是可变的,也称为谐振栅极驱动器[18-20]。可变驱动电路由S1、S2、D1、D2组成,当S1开启且S2关闭时,ig可以为Cgs充电。上述过程中,当Vgs低于VCC时,ig增加;当Vgs高于VCC时,ig开始下降。然后SiC MOSFET导通。SiC MOSFET的关断与上述类似。

图12 电流源栅极驱动器的2种结构及电流时序和关键波形

虽然电流源栅极驱动器在低能耗和高频应用方面具有很大的优势,但也存在许多缺点:

(1)SiC MOSFET的栅极电压不受控制

在电流源栅极驱动器中,SiC MOSFET的寄生电容被电流源充电,无法控制栅极电压值,导致栅极电压可能会损坏SiC MOSFET。为了解决这个问题,文献[15,18-20]利用钳位电路使SiC MOSFET的栅极电压在一个合理的范围内。然而SiC MOSFET需要较大的驱动电流,因此钳位电路的电流容量需要很充足,这将增加整个驱动电路的体积。

(2)过冲电压和EMI噪声大

文献[15,17-20]中电流源栅极驱动器的驱动电流不是分段的,由于SiC MOSFET的寄生电容小,这会产生大的过冲电压和EMI噪声(d v/d t和d i/d t)。文献[9]添加了栅极电阻以在EMI噪声和能量损失之间进行折衷。

为了控制d i/d t和EMI的大小,电流源型的驱动也可以采用分段式的驱动策略,文献[25]提出了一种将闭环控制和分段控制结合的控制方式和驱动电路,驱动架构如图13(a)所示,其将驱动电流分为逻辑信号控制的电流idis和d i/d t反馈信息控制的电流iana两部分,逻辑控制的离散电流仅与开关控制时序有关,带有d i/d t反馈信息的电流对功率管的d i/d t产生影响,从而形成一个闭环系统,实现负反馈调节。

文献[25]中的电流时序如图13(b)所示,结合电流时序对开启过程和关断过程中漏极电流Id变化阶段的栅极充电电流ig和d i/d t之间的关系进行了模型建立,对于关断阶段而言,功率管被完全关断前,离散电流If1始终存在,当漏端电流开始变化时,与d i/d t相关的电流iana才不为0。在电流发生变化时,栅极电流对功率管的栅极寄生电容Ciss放电,放电导致的Vgs变化在跨导的作用下进一步对漏端电流产生影响:

图13 闭环控制和分段控制结合的驱动架构[25]

其中gfs是SiC MOSFET的跨导。为了实现整体栅极电流ig为离散控制电流idis和模拟电流iana的总和,可以最终建立如下关系式:

其中If1和If2的大小取决于设计中想要控制的dv/dt和di/dt的大小,由此将栅极电流和di/dt建立了合适的模型,只要在电路设计上使模拟电流iana的产生和di/dt信息采样之间建立式(10)所示Kpf的比例关系,即建立合适的闭环网络,再通过合适的补偿网络保证环路的稳定性。文献[27]最终采用板级搭建的方式实现了合理的闭环系统,使环路的单位增益带宽做到了50 MHz。在模型建立和架构搭建上都比较新颖,做到了大带宽的设计。

SiC MOSFET的开关瞬态di/dt和dv/dt对EMI和系统稳定性存在影响,很多设计针对di/dt和dv/dt的控制以及相关振铃、串扰问题进行了抑制,这必然是建立在以延长di/dt和dv/dt存在阶段的时长为代价的,这将会降低功率管的开关瞬态速度,加大开关瞬态时间,限制高频高速的应用频率上限,增大开关瞬态功耗。为了实现对di/dt和dv/dt的控制,又能尽可能缩短开关瞬态所需的时间,提高di/dt和dv/dt存在阶段之外的驱动能力是一个可行方法,但是SiC MOSFET本身具有10Ω左右的栅极寄生电阻,对于完全发挥SiC MOSFET的高速开关性能存在一定限制,想在传统驱动架构的基础上实现更高的驱动能力比较困难。

文献[21-22]对SiC MOSFET开关性能的提升进行了驱动架构的改善和研究,降低了开关瞬态的时间,提高了速度。文献[21]采用电荷泵的方式,利用电容给功率管的栅极提供电荷,实现高于传统驱动中20 V供电电压的驱动能力,提高了驱动速度。文献[22]采用谐振式的结构增大驱动过程中的栅极电流,使栅极电流突破传统驱动中的电流上限限制,实现更快的驱动速度。文献[22]提出的提高驱动电流的谐振驱动架构如图14所示,利用S3和S4两个双向开关对Vgs进行钳位,保证Vgs处于安全的电压范围内,避免了谐振型驱动中栅极电压易超出安全范围的问题。

图14 提高驱动电流的谐振驱动架构[22]

虽然文献[21-22]没有进一步与分段控制结合起来,也没有构建合适的分段驱动架构,但是为进一步提升SiC MOSFET的驱动能力提供了可能性,为今后实现更高速的分段控制奠定了基础。

2.2.3 串扰抑制及保护电路

在SiC MOSFET的栅极驱动器中,有一个非常关键的问题是要确保SiC MOSFET处于安全适当的工作状态。由于SiC MOSFET的高速开关操作及其对异常状态的耐受性较差,因此提高SiC MOSFET的可靠性也很重要。SiC MOSFET的可靠性主要从两个方面考虑,一是过流保护(Over Current Protection,OCP),二是dv/dt噪声的抗扰度。

SiC MOSFET的OCP与Si MOSFET非常相似。不同的是OCP电路的响应速度需要非常快,这是因为过流故障情况下的SiC MOSFET只能保持很短的时间,只有几微秒。在文献[4,26-28]中,OCP设计技术主要包括固态断路器(Solid State Circuit Breaker,SSCB)、去饱和技术、源端寄生电感检测和电流发送器。

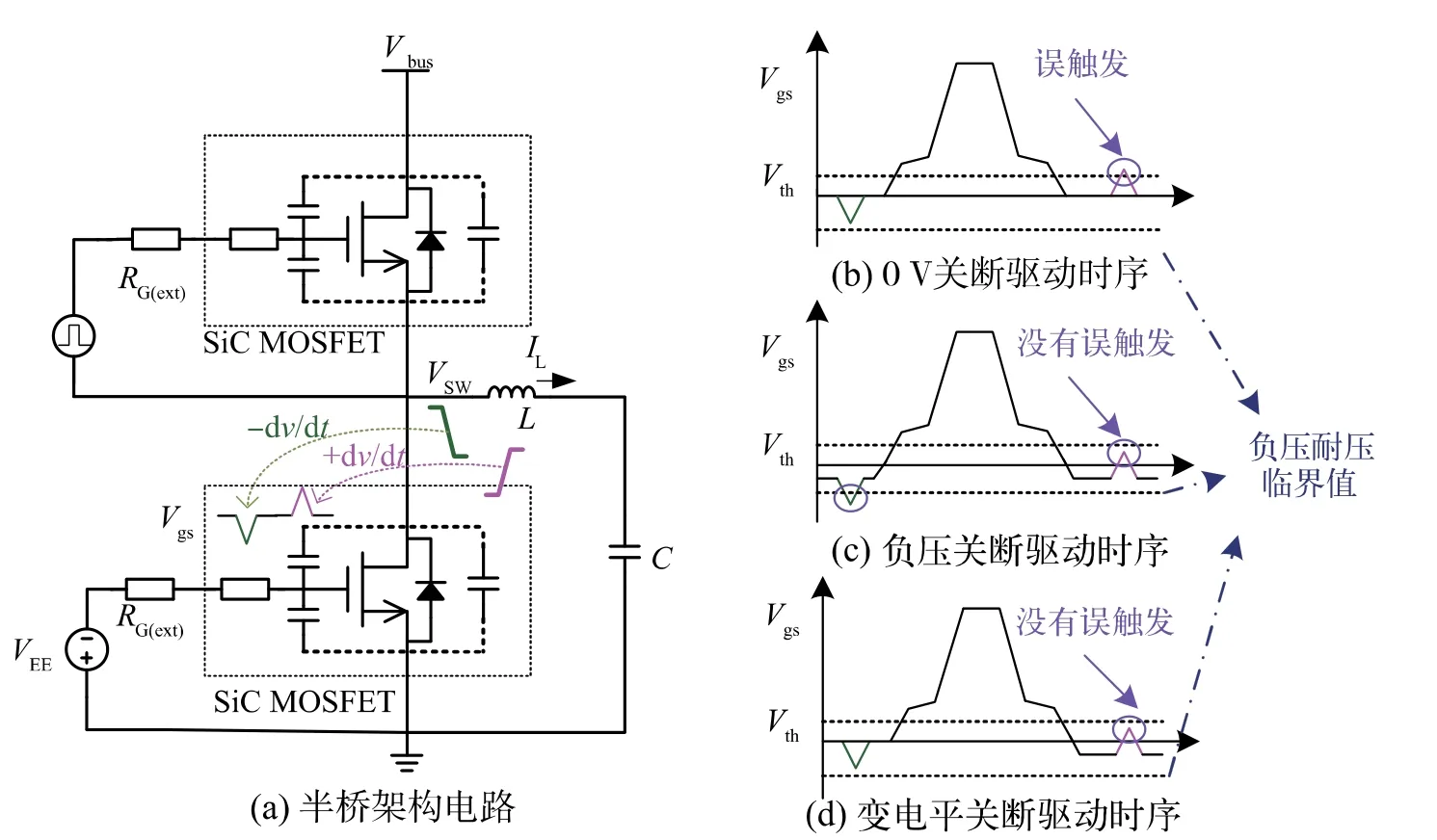

SiC MOSFET常用于800~1200 V的高压应用,在功率管开启阶段,MOS管的漏源电压Vds会从1200 V降到0 V,在功率管关断阶段,MOSFET的Vds会从0 V增加至1200 V。由于SiC MOSFET的栅极寄生电容较小,开关速度较快,在短时间内变化了1200 V的大电压,将产生非常大的dv/dt。以半桥应用的SiC MOSFET为研究对象,dv/dt对低侧管的串扰情况如图15所示。图15(a)展示了正dv/dt对于低侧功率管的影响,由于在低侧功率管的漏端和源端之间存在寄生电容Cgd,在dv/dt的作用下将会有一股寄生电流从低侧管的漏端流向源端,这股串扰电流最终流向驱动器的下拉支路。由于这股电流在VEE和栅极之间的电阻上产生压降,导致实际的Vgs比正常关态时的Vgs要大,在低侧功率管的栅源电压之间引入一个正的电压串扰。当存在负dv/dt时,对实际的Vgs的影响正好相反,在低侧功率管的栅源电压之间引入一个负的电压串扰。正的串扰将使Vgs增大,如果串扰电压过大,将导致低侧管误开启,如图15(b)所示,因此,需要负关断电压。负的串扰将使Vgs变小,如果串扰过大会使Vgs超过SiC MOSFET的负压耐压额度,增大功率管被损坏的风险,这种情况在图15(c)所示的负关断电压下更容易发生。因此,在SiC MOSFET的驱动设计技术中,不仅需要使用负关断电压来提高其正dv/dt抗扰度,还需要使用零关断电压来提高其负dv/dt抗扰度,这就是如图15(d)所示的可变关断电压的设计技术。

图15 d v/d t对低侧管的串扰情况

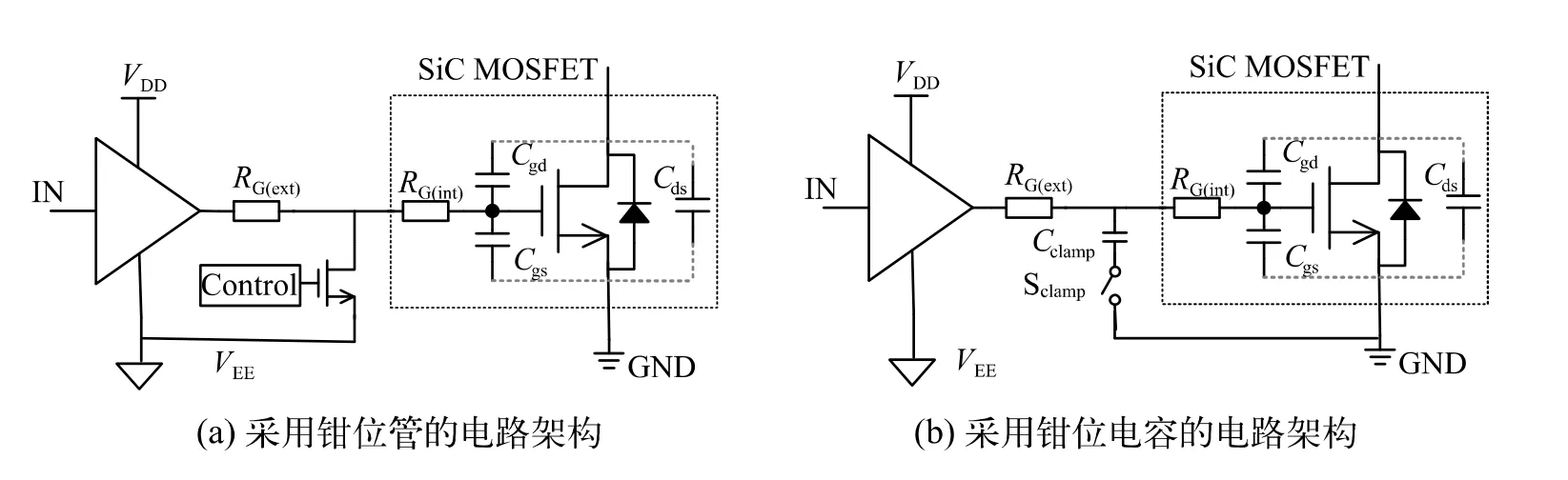

有源钳位电路架构如图16所示。除了采用可变关断电压的方式来抑制dv/dt串扰问题外,根据串扰的产生机理,采用大的功率管并联在SiC MOSFET的栅源之间,为串扰电流提供低阻通路,从而可以大大降低串扰,见图16(a);也有采用大电容并联在SiC MOSFET栅源之间的方式,在串扰产生时让更多的电流流向电容,从而降低串扰的大小,见图16(b)。但是钳位电容的方式需要采用开关管动态开启和关闭,否则大电容的存在将会影响SiC MOSFET开启和关闭的速度,因此大电容和开关管的存在导致这种方式与只用钳位管提供低阻通路的方式相比几乎没有优势,都需要为钳位管或开关管提供控制电路。

图16 有源钳位电路架构

文献[8-9,15]提出双电平关断电压技术用于改善SiC MOSFET的±dv/dt,采用辅助晶体管在PCB板上实现可变关断电压。文献[3]的有源钳位方式是采用钳位管进行钳位,设计了一个简单的辅助控制电路对钳位管进行控制,利用SiC MOSFET的栅极电位和驱动级的输出状态自动影响辅助电路,在RC的延时下使有源钳位管在合理时段开启和关闭,从而实现图15(d)所示的时序。文献[4]提出了有源米勒钳位技术来增强SiC MOSFET正dv/dt抗扰度,设计方法是SiC MOSFET的栅极电压直接与下拉功率晶体管相连,其外栅极电阻不受正dv/dt噪声的影响,从而提高了dv/dt抗扰度。

3 SiC MOSFET栅极驱动器设计考虑

由以上分析可知,在设计SiC MOSFET的栅极驱动器时,需要考虑低EMI噪声、高开关速度(高频)、低能量损耗和高可靠性。

对于电压源栅极驱动器,多电平驱动方式在低EMI噪声和快速开关速度方面具有很大优势。因此,多级栅极驱动器是趋势。但是现在大多数驱动器还是在PCB板级上实现的,多电平自适应的集成电压源栅极驱动器将是今后研究的热点,既能实现驱动、di/dt和dv/dt控制、有源钳位的联动控制,又能促进小型化。

虽然电流源栅极驱动器在低EMI噪声方面存在一些缺点,但在高开关速度和低能量损耗方面具有不可替代的优势。这种技术对于SiC MOSFET的栅极驱动器来说仍然是更好的选择,它也仍然需要优化和改进。将高速度和多电平相结合,将实现速度和EMI的双重优化效果。

最后,SiC MOSFET的可靠性至关重要,其设计技术也值得关注。在栅极驱动器的设计中,应考虑可变关断电压技术、有源米勒技术和快速过流保护,以保证器件和系统的可靠性。

4 结论

本文全面回顾了SiC MOSFET的基础理论以及其驱动电路的发展状况,主要从电压型驱动电路设计技术、电流型驱动电路设计技术以及提升系统工作可靠性设计技术3个方面进行论述,对基于SiC MOSFET驱动电路设计的3个方面进行了详细的分析、归纳及总结,分析了它们各自的优缺点。从开关速度、EMI噪声和能量损耗方面对已有驱动设计技术进行了分析和总结。电压型栅驱动设计技术是目前应用最为广泛的驱动设计技术,被广泛使用在各类功率管中,在开关速度、EMI噪声和芯片集成度方面具有非常大的优势。电流源栅极驱动器在开关速度和低能耗方面具有优势,但受到EMI噪声的限制,其应用非常有限;不过,由于其架构的优异特性,仍然有很大的研究改进空间。快速OCP、有源米勒钳位和可变关断电压可提升SiC MOSFET的可靠性,这些均可以在SiC MOSFET的驱动电路中得到应用。值得一提的是,以上提出的设计技术均已在PCB板上实现并验证,其性能受限于板级寄生影响,因此,SiC MOSFET的驱动技术仍需广泛研究。