量子计算模拟及优化方法综述

喻志超,李扬中,刘 磊,2,冯圣中

(1.国家超级计算深圳中心(深圳云计算中心),广东深圳 518055;2.中国科学院计算技术研究所计算机体系结构国家重点实验室,北京 100190)

0 概述

量子计算是一种遵循量子力学规律调控量子信息单元进行计算的新型计算方式。由于量子力学叠加态的存在,量子计算机与经典计算机相比具有更强大的并行信息处理能力,并有望解决经典计算机无法解决的问题。量子计算被认可的潜在应用领域包括密码学[1]、量子化学[2]、材料科学[3]、机器学习[4]等。

研究量子计算技术,需要开展精确的量子门操作和纠错、容错等实验,以及模拟量子叠加、纠缠等状态,构造足够复杂的相干量子计算实验体系,并开展适用的量子计算模型和算法研究。量子计算的主要研究方向包括构造含有更多量子比特的通用量子计算机、设计更有效的量子算法以及优化量子程序编译器[5-6],从而使得量子计算机能被广泛使用。现阶段的量子计算机属于嘈杂的中尺度量子(Noisy Intermediate Scale Quantum,NISQ)计算机[7-8],量子位的数量尚不过百,量子位状态脆弱且易受干扰,无法保证量子程序的可靠执行,也无法适用于求解大规模的科学计算问题。自从谷歌提出量子优越性以来,如何展示现阶段量子对于经典计算机的优势一直是研究热点[9-11]。由于量子比特受到噪声的影响易失去量子特性,而基于量子纠错码的容错架构可能是利用量子计算机执行大规模计算的重要基础,因此设计一种使用适度资源即能有效对抗实际噪声的实用量子纠错码,也是量子计算核心问题之一[12-13]。此外,探索新的效率明显优于经典计算机算法的量子算法,也已经成为量子计算理论研究的一个重要分支[14]。

由于已知量子运行规律,因此可使用经典计算机模拟量子计算。量子计算模拟器相比于物理量子比特计算机的突出优势是功能齐全,可执行的量子程序规模不会受到物理量子计算机保真度的制约,是理想的量子算法测试平台[15]。量子计算模拟包括计算并存储所有量子态、部分或者单个量子态概率幅、含噪声模拟等多种形式,不同的模拟方法对应于不同的量子计算目标。许多研究机构开发了量子线路模拟器用来支撑量子计算领域复杂问题的模拟,如太章模拟器[10-11]、ProjectQ[16]、qHiPSTER[17]、QuEST[18]等。量子模拟器可被部署于分布式超级计算机集群,利用超算集群的运算性能实现量子计算的高效模拟,模拟过程中需要考虑子任务划分和通信优化问题,通过分布式节点上任务的合理分配和减少通信成本的设计策略,实现均衡分布式节点间负载的目标。

为了能够模拟具有更多量子比特数且深度更深的量子线路,如何减少模拟所需存储和提高模拟计算效率是关键问题。现有研究对算法的优化改进,使得模拟器在实际应用中已经取得了较大突破。针对目前量子计算模拟的研究工作,本文综述实现量子计算模拟的基本方法,总结量子线路模拟的优化方法和已有的模拟器,并阐述在超算上模拟量子计算的核心问题,讨论相应的优化方法。

1 量子计算原理

本节主要介绍量子计算理论中的背景知识,包括量子比特、量子门、量子线路、量子操作系统和量子模拟。

1.1 量子比特

经典计算机的比特位只有0 和1 两种状态,而量子比特中这样确定的状态则被称为基本态,除此之外,还有可能是2 种状态的叠加态。一个量子比特位(量子位)的状态(状态向量表示)可以看作是由两个基本态(计算基态向量和)组成的二维复空间向量。根据量子规律,单量子比特可以是两种基本态叠加成的任一种状态,用状态向量公式表示为:

其中,系数α、β为复数值的概率幅,|α|2和|β|2分别为对应状态的概率且满足|α|2+|β|2=1。

n位量子比特的状态向量可以表示为2n个基态的复合态:

1.2 量子门

经典计算使用逻辑门操作经典比特的状态,量子计算则使用量子门操作量子位状态。量子态满足归一约束|α|2+|β|2=1,经过量子门作用后得到的量子态依旧满足归一化约束,所以量子门相应矩阵U须为酉性[19],即U*U=I,U*为U的共轭转置。因此,量子态的制备和任何对量子态的操作都是酉操作,量子门是对所选量子位进行酉操作的算子。

按照操作涉及的量子比特的个数,可以将量子门分为单量子比特门和多量子比特门。单量子比特操作中常用的有Hadamard 门、Pauli-X 门、Pauli-Y 门、相位门(S 门)等,多量子比特操作中常用的有CNOT门、受控Z 门(CZ 门)、Toffoli 门等。表1 列出了常用的量子门及其矩阵形式。

表1 常用量子门Table 1 Frequently-used quantum gates

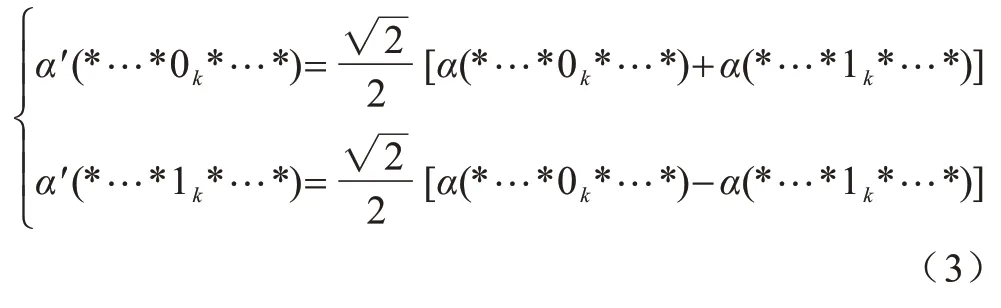

以Hadamard 门为例,假设一个目标量子比特为k的Hadamard 门,其概率幅计算和操作更新规则为:

1.3 量子线路

量子算法由一系列基础的量子门组合而成,实现的形式称为量子线路。量子线路以量子比特为基本存储单元,将量子逻辑门连接在一起来实现特定的计算功能,可以直观地表示量子算法的结合和复杂度。本质上,量子计算可以描述为对包含量子比特的量子系统实施一系列酉变换,然后对变换之后的状态进行测量,最后得到计算结果的过程。因此,量子计算的过程包括初态设置、状态变换和测量3 个步骤。图1 为2 个量子比特的Grover 搜索算法线路图[1],其中每一条线代表一个量子比特,量子门操作使用不同的方块表示。

图1 Grover 算法示意图Fig.1 Schematic diagram of Grover algorithm

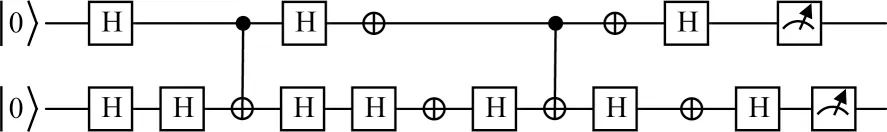

量子优越性是量子计算研究过程中的一个重要里程碑,指现阶段实现针对特定问题的计算能力超越经典超级计算机。为研究量子优越性,研究人员提出了一些非常适合于展现量子设备计算能力的特定问题,包括随机量子线路采样(Random Circuit Sampling)[9,20]、IQP(Instantaneous Quantum Polynomial)线路[21]、高斯玻色采样(Boson Sampling)[22-23]等。谷歌量子研究团队所针对的问题是随机量子线路采样问题,中科大团队则致力于高斯玻色采样问题的研究。

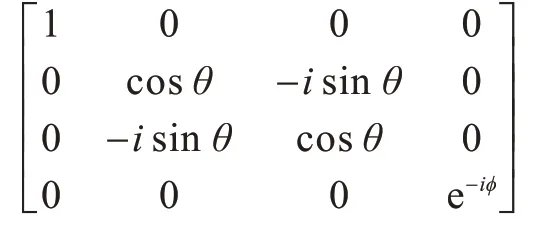

如图2(a)所示,谷歌的Sycamore 随机量子线路是在特定图结构上,周期地作用单量子比特门和两量子比特门,且最终以单量子比特门结束[9,24-25]。单量子比特门均匀随机取自于一个单量子门的集合,两量子比特门表示为:

其中,θ=90°,φ=30°。随机量子线路采样问题是一个足够复杂且又适合当前带噪声量子计算机求解的计算问题,能够以较少的门操作数量来实现较大纠缠的量子态。随机量子线路采样成为最近展现量子优越性的主流候选问题,主要有3 个原因:1)随机线路采样问题非常适合于在二维结构的超导量子计算芯片上实验实现;2)已有很多理论工作证明了随机线路采样问题的困难性;3)随机量子线路采样满足反集中(anti-concentration)性质,表现为噪声对输出结果的概率造成的影响更小。

如图2(b)所示,玻色采样过程的模拟是计算给定输入光子分布时得到某种输出光子分布的概率,其最重要的部分在于求解矩阵积和式,而计算复矩阵的积和式对经典计算机来说是很困难的。

IQP 线路代表一类简化的量子线路模型,如图2(c)所示,线路的初始量子态都为零态,首先对每个量子比特作用一个Hadamard 门,然后在这些量子比特上作用对角的门,最后再次在每个量子比特上作用Hadamard 门。

图2 研究量子计算优越性的3 种量子线路Fig.2 Three quantum circuits for studying quantum advantage

1.4 量子操作系统

量子操作系统是量子计算机资源的管理者,负责管理、监控、配置量子位硬件资源,调度量子程序运行的先后顺序,控制量子程序单独或并发映射,并提供具体的量子线路映射策略,保证量子程序的可靠度。为了充分利用量子计算机强大的计算能力,文献[26]倡导建立量子操作系统来管理量子计算机的硬件资源。文献[5-6]在国内率先开展了量子操作系统的原型研制,提出QuOS 原型,用于并发多量子程序在量子芯片上的映射、调度和优化。该系列工作设计了优化健壮量子位资源利用率的程序映射策略、跨程序量子位交换的映射方法和多量子程序调度机制,为量子操作系统软硬件栈的设计和优化提供了原型系统和参考经验。

1.5 量子模拟

目前,由于量子计算机的真机仍处于发展阶段,通常单机可用的量子位数量较少(在100 以内)且量子位状态保持不稳定,不能完成有实际意义的、较大规模的量子运算。在未确定量子硬件实现方案之前,很多量子算法所展现出的巨大计算潜力并未得到真机的实验验证,而主要是基于数学理论或者基于经典计算机的形式进行模拟验证。

量子计算机除了和经典计算机有相似模型之外,还存在一些特有的计算模型。比较常用的量子模型包括量子线路模型、绝热量子计算模型、One-way 量子计算模型、拓扑量子计算模型等。虽然这些模型设计的出发点不同,但计算结果的输出是一致的,且相互之间可以进行转化。在处理某类特定问题的计算中,采用不同的算法计算复杂度可能不同,而选择一款好的计算模型能够简化算法的实现流程。

采用超级计算机模拟量子计算的过程,是目前研究量子计算、辅助量子计算机执行任务的一种方式。国内外科研机构、公司、高校积极开展了相关研究。量子模拟内涵丰富,本文将从量子计算模拟方法、国内外量子模拟器、超算集群模拟等方面进行深入介绍。

2 量子计算模拟方法

量子计算模拟主要是通过输入不同的矩阵来改变要计算的量子态的状态,从而引起量子线路状态的变化。但在量子线路中,由多个量子逻辑门级联而成对于逻辑门的操控精度提出极高的要求,若量子比特门的保真度不高,逐级增大,则会严重影响最终计算结果。受制于量子比特自身的物理特性,计算错误的发生常常无法避免,但可以避免错误对最终计算结果的影响。此外,评估量子计算中的错误严重性,对于改进器件的设计、优化控制参数以及使用缓解协议最小化错误至关重要。

2.1 量子计算概率幅模拟

量子计算概率幅模拟方法通过对概率幅的计算在经典计算机上实现对量子计算的模拟,在量子线路模拟过程中,通过计算一个量子线路后终态在各个基态上的概率幅获取量子计算的模拟结果。该方法可分为全概率幅模拟和单概率幅模拟,其主要区别在于,全概率幅模拟一次模拟计算能够计算出量子态所有概率幅,而单概率幅模拟只能计算出所有概率幅中的一个。除此之外,还有部分概率幅模拟的目的是在更低的硬件条件下实现更高的模拟效率。

全概率幅模拟方法直接计算并存储全部量子态,计算的空间复杂度随模拟的量子比特数指数增加。以n个量子比特为例,需要计算2n个复数形式的量子态来描述该量子系统,如果采用双精度浮点数表达概率幅,则需要存储空间的量子态为24+nByte。目前,即使在大型超级计算机上,也很难模拟一个超过50 个量子比特的量子线路。一方面,一个包含50 个量子比特的线路,完整的状态有250个,即使采用单精度浮点来存储,也需要约4 PB 的内存空间,这几乎达到了当今超级计算机可使用内存的最大值;另一方面,即使超级计算机的内存够用,处理这些海量数据也比较困难,原因在于数据在超算系统的网络传输中将产生巨大的通信负荷[27]。

薛定谔方法和费曼方法是2 种经典的量子计算模拟方法。薛定谔方法存储全部量子态,按顺序计算作用不同量子门后的全部振幅,对于n个量子比特所需的24+nByte 的内存,每个量子门需要O(2n)的计算时间,对于深度为m的量子线路,所需模拟时间约O(mn2n)。费曼方法[28]对于终态的每个分量,枚举通过量子线路中量子门能从初态到这一态的变化路径,将所有这些路径的值累加即可得到对应的概率幅,计算过程中存储一条路径最多需要O(n2m)的空间,对于深度为m的量子线路,计算一个状态的振幅需要的时间为O(2mn)。文献[8]将上述两种方法相结合,提出薛定谔-费曼方法,以达到平衡算法时间和空间复杂度的目的。此外,研究人员还提出了数据压缩[29]、辅助变量[30]、MPS[31]、PEPS[32]、部分振幅模拟[33]等方法,使得45 个量子位以上全概率幅的大规模量子计算模拟得以实现。

在量子计算模拟中,可将量子线路转换为具有酉正性的特殊张量网络表示,其单个概率幅的计算可以转换成张量网络缩并问题。张量网络缩并算法不直接存储实时的量子态,而是将初始量子态和测量基矢当作很多一维张量,这些张量和量子门操作组成一个时间和空间维度上的三维张量网络。如何对一个包含数百节点的高维张量网络选取一条接近最优的张量收缩路径,是张量网络收缩算法的关键问题。

文献[18,34]采用张量网络方法计算特定量子基态的概率幅,在模拟过程中利用对角矩阵缩减计算项数,并采用无向图模型优化张量网络缩并顺序,从而减小张量网络缩并开销。文献[35]改进张量网络缩并顺序优化算法,使其适用于分布式集群,并利用分布式计算的特性,将张量网络计算任务拆分为多个子任务,使每个子任务的执行时间尽可能短,最终在阿里云集群上用1 PB 内存实现了81 量子位、40 深度的量子线路模拟。

谷歌提出的随机量子线路结构是一个高度正则的张量网络。当张量网络缩并时,正则性将会表现为占用大多数计算时间的节点,构成一条“主干”,几乎所有的运算时间都花在节点个数相较“分支”节点较少的“主干”上。文献[8]提出一种基于张量网络收缩的模拟方法,该方法主要分为图划分、局部优化和动态切片3 个步骤。首先,将张量网络的节点划分为若干块,包含“主干”和“分支”部分,持续重复对“主干”部分划分直到缩并成点后,对剩下的点再进行计算缩并。通过识别和优化这样的“主干”,该方法计算速度可以比谷歌的模拟算法快200 000 倍。

文献[32]基于张量网络态来求解随机量子线路采样问题。张量网络态算法可以认为是对张量网络收缩算法选取了一条特定的收缩路径,即先收缩时间维度,再收缩剩下的空间方向的二维张量网络,通过对节点上的张量利用奇异值分解或QR 分解进行自动压缩,以降低节点张量的维度。

文献[36]提出Big-Head方法,并使用60个英伟达GPU 组成的小型计算集群,在5 天时间内完成了谷歌量子随机线路的模拟。Big-Head 方法将终态的n个量子比特分为两组,数量分别为n1和n2。任意位串s 可视作两条位串s1和s2的拼接,其概率可计作PU(s)=PU(s1;s2)。当n2=0 时,该方法和张量网络的单概率幅估算一样。Big-Head 中最重要的环节就是找到一个满足上述条件,时间与空间复杂度都比较合适的缩并阶数,其使用分割算法将整个张量网络切割成Ghead与Gtail两份,切割边nc条。分割算法会在对n1和n2数量限制的基础上最小化。要找到分割点,需要保证同时缩并2 个部分的计算复杂度不会太大,为了达到这个目的,其使用一种聚类算法将每个子图都分割成更小的子图,直到每个子图都足够小。

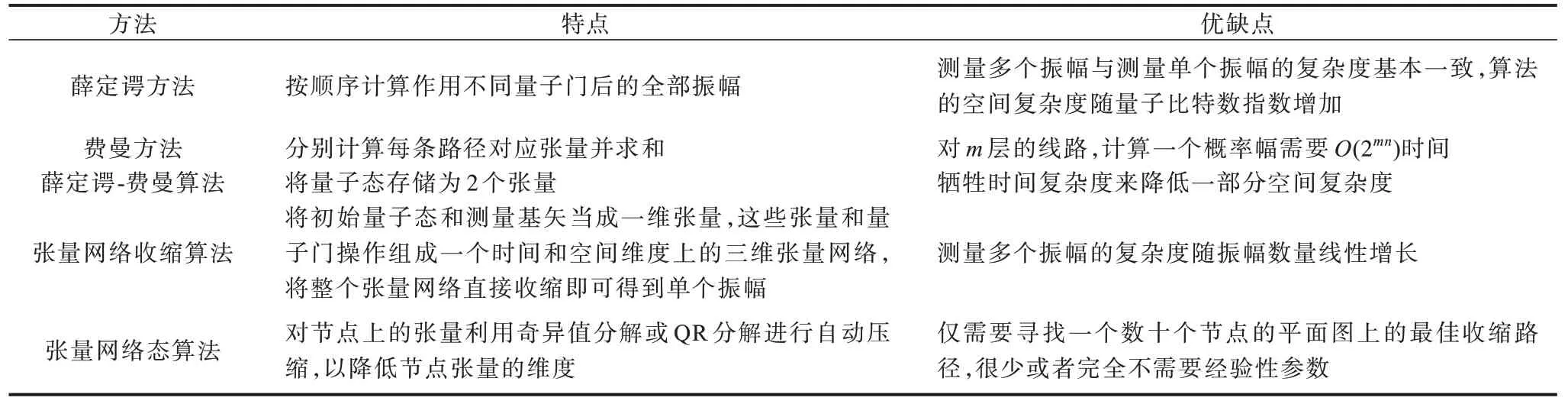

常见量子计算模拟方法的特点及优缺点如表2所示。全概率幅模拟方法的计算复杂度随模拟量子线路的深度线性增长,因此该类方法适合模拟具有较少量子比特数、任意深度的量子线路,适用于需要获取全部模拟结果等场景。部分概率幅模拟方法的效率高,相比于全概率幅模拟方法能够模拟具有更多量子位的浅深度的量子线路。张量网络态算法可以用几乎相同的模型来研究不同硬件架构下不同深度的随机量子线路,原因在于其通常存在一个简单的路径搜索算法,仅需寻找一个数十个节点的平面图上的最佳收缩路径,因而实现起来只需要很少或者完全不需要经验性参数。张量网络收缩算法则往往需要考虑具体线路来确定其经验参数,相比而言,其在更大空间搜索最优路径,具有更大的优化空间。

表2 常见量子计算模拟方法特点及优缺点Table 2 Features,advantages and disadvantages of common quantum computing simulation methods

2.2 针对Clifford 线路的量子计算模拟

量子比特通常是不稳定的,为了维持逻辑量子比特的准确性,需要进行量子纠错。与传统的纠错方法不同,由于量子不可克隆定理、量子叠加态塌缩(或称波函数塌缩)的限制,对量子比特进行纠错必须加入辅助量子比特。相对于经典比特,量子比特还存在相位上的错误,这也为量子纠错带来了更大的复杂性,通常需要上千个物理量子比特来实现一个高保真的逻辑量子比特,而这也会为系统带来大量的噪声。针对容错、抗退相干、保护目标数据的准确存储,以及正确编码、运行等问题,目前研究者提出了一些解决方案,包括无消相干子空间(Decoherence Free Subspace,DFS)、拓扑量子计算、基于量子纠错码的容错量子计算等[37]。

针对因噪声而导致的计算错误问题,可以使用量子纠错码来解决。在计算错误的分布满足某些条件的情况下,可以把最终计算结果出错的概率降到任意低,这被称作容错量子计算。与经典纠错相比,量子纠错不仅需要处理比特错误,而且还需要处理相位错误。容错量子计算在量子计算码的基础上,通过级联的方式实现量子逻辑门,以至于当物理操作的出错率低于容错阈值时,量子逻辑门的错误率急剧降低,从而实现可靠的量子计算。

量子纠错码与级联结合,满足容错量子计算要求,横向实现量子逻辑门,使得错误的位数和传播控制在量子纠错码的纠错范围内。在量子纠错码上,可以横向实现的量子逻辑门基本来自于Clifford 群。Clifford 群是指把Pauli 群共轭映射到Pauli 群的操作形成的群,包括Hadamard 门、相位门S 和受控非门CNOT 等。

Stabilizer codes 是一种基于稳定子的定义通用量子纠错码的框架,用以表述和操作需要的量子态,其使用Clifford group 中的量子门对稳定子态进行编码和解码。拓扑码是一种比较容易实现的编码方式,其可构造局域的稳定子测量来避免远程的量子比特的交互,从而降低对设备的要求。拓扑码的一个显著的优点在于,人们可以通过增加单位晶胞的大小来提升检错和纠错的容量。然而,随着编码容量的增大,解码的任务必然会对量子态造成干扰,因而设计有效的解码算法成为拓扑码最重要的任务。表面码的关键问题在于,要使用它来实现通用量子门集合是比较困难的,因为其缺少Toffoli 门以及π/8 门。在容错量子计算的标准模型中,通常使用魔法态注入过程来构造一个完整的量子门集合。

随机基准测试[38]和量子过程层析(Quantum Process Tomography,QPT)[39]可以分别测量噪声量子信道的平均门保真度和完整信息,但这2 种方法只在几个量子位系统中是有效的。交叉熵基准测试可以用于验证多量子比特系统,但无法直接应用于经典计算机不可模拟的量子线路。量子计算机的并行计算能力随量子比特数目增加而指数上升,同时,表征量子线路误差的难度也指数上升[9]。文献[40]提出一种基于Clifford 采样的方法来描述量子线路的误差,克服了现有误差表征方法的不足,但只适用于少数几个比特的量子线路,很难被用在未来成百上千个量子比特的量子线路表征中。Clifford 采样将一个指数复杂度的问题转换成多项式的问题,具有很好的可扩展性,适用于大规模量子线路参数的优化以及筛选等多个领域。

Gottesman-Knill 定理表明,一个仅由CNOT、Hadamard 门和相位门组成的量子线路可以在经典计算机上有效模拟。文献[41]改进了定理中的算法,去除对高斯消元法的依赖,并给出2 种稳定态内积计算的有效算法。针对Clifford+T 门线路的模拟,研究者开展了一系列的工作,包括模拟包含少量T 门的量子线路和考虑nonstabilizer 的输入态+Clifford 线路的模拟等[42-43]。为了解决量子线路的容错和可靠性问题,研究者提出了量子线路的一系列结构等效规则和优化操作策略,以尽量减少T 门的数量,增加T 门的深度,最小化线路级,减少容错实现代价并提高线路可靠性[44]。

2.3 针对含噪声线路的量子计算模拟

NISQ 设备的计算能力对于量子信息科学具有基础和实际重要性。如果没有减少或绕过物理噪声的策略,在苛刻的条件下任何量子程序的执行都可能会失败。降噪技术的策略是设计更稳健的量子位来延长时间,以及执行更精确的门操作以提高可靠性等。随机编译是一种常用的策略,即在量子线路中插入随机门。所有相干误差和非马尔科夫噪声都可以转换为随机泡利误差,在保留一个量子线路逻辑操作的同时误差容易被检测和纠正。虽然噪声对单个随机线路的影响可能有所不同,但在多个随机线路上的预期噪声被打乱,并调整成一种简单的随机形式。

文献[45]考虑了在对称或非对称去极化噪声下一大类随机通用量子线路,并证明了如果每个量子门的噪声是恒定的,那么这些量子线路的输出可以用系统大小的时间代价多项式进行经典有效的模拟。文献[46]结合了纯态分解和低维基投影的思想来有效地模拟噪声量子线路,提出将混合密度矩阵分解为一个类似于纯态集合的低秩矩阵,将门和Kraus 运算子应用于该低秩矩阵,并计算了输出密度矩阵和概率分布。该过程包括对密度矩阵的迭代压缩,可保持一个具有最小误差的数值紧凑形式。

3 量子计算模拟器

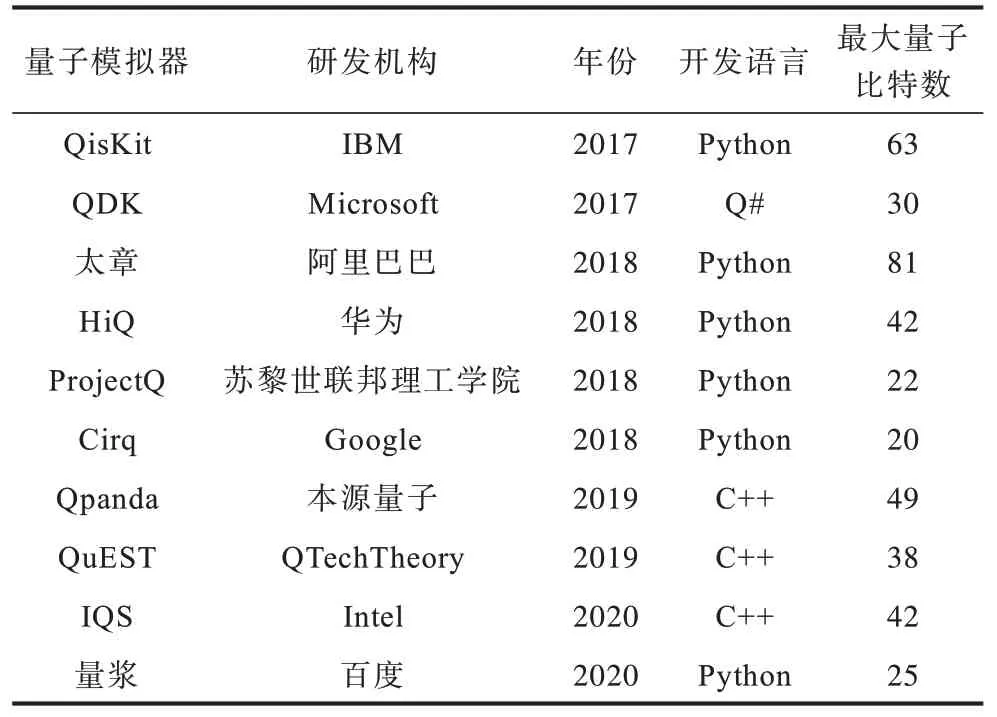

量子模拟器是在经典计算机上实现对量子计算机的模拟。近年来,基于量子计算原理,国内外许多公司机构设计并开发了大量的量子模拟器,如QisKit 量子模拟器(IBM)[47-48]、QDK 量子模拟器(Microsoft)[49]、太章量子模拟器(阿里巴巴)[10-11]等。现有的量子模拟器规模仍属于NISQ 模拟器,模拟量子比特数在100 以内,主要受限于经典计算机的存储技术和处理能力。本文系统梳理了国内外常见的量子计算模拟器,如表3 所示。

表3 常见量子计算模拟器Table 3 Common quantum computing simulators

QisKit[47]是由IBM推出的Python量子开发工具集,包含Terra(量子计算基础库)、Aer(带有噪声的模拟器)、Aqua(量子算法)、Ignis(检测和去除实际量子计算机噪声)四大组件,该量子模拟器可用于机器学习、自然科学、经济金融领域以及解决最优化问题。

QDK[49]是Microsoft 推出的Q#量子开发工具集,Q#是一款面向量子计算机开发的程序语言,其结合了Python、C#等多种语言的设计元素,对量子计算机的逻辑进行了高度的封装。QDK 包括Q#编译器、量子库和量子模拟器,该量子模拟器可应用于量子机器学习、量子化学等领域。

太章[10-11]是阿里巴巴推出的Python 量子开发工具集,目前最高存储不到60 量子比特的量子态,太章采用张量网络收缩的动态拆分办法,减少了量子线路模拟的资源占用,支持量子算法和纠错。

HiQ[50]是华为推出的Python 量子开发工具集,包括华为HiQ 量子模拟器、HiQ Pulse、HiQ Fermion等功能模块,目前主要应用于量子化学领域。

ProjectQ[16]是苏黎世联邦理工学院推出的Python 量子开发工具集,其提供了量子模拟器、编译器框架、编译器插件、资源估算等模块,可实现量子和量子线路的模拟。

Cirq[51]是谷歌推出的Python 量子模拟器,用户可通过Cirq 实现对量子线路的精确控制,同时开源的OpenFermion-Cirq 可应用于量子化学领域。在Cirq 的基础上,谷歌应用量子机器学习原理设计开源TensorFlow-Quantum(TFQ),该框架可有效解决量子分类、量子线路优化等问题。

Qpanda[52]是本源量子推出的C++量子工具集,其在量子模拟器基础上实现了大量量子算法,如量子近似优化算法(QAOA)、Deutsh-Jozsa算法、Grover算法等。

QuEST[18]是牛津大学QTechTheory 团队推出的C++量子模拟器,其在模拟基本量子计算的基础上,支持CPU、GPU 多平台运行。

为了安全库存模型求解的合理性,需要做出以下假设:(1)生产线不允许缺料停线,停线费用设为无穷大。(2)库存的消耗是连续且均匀的,即假设生产线是以恒定生产节拍进行消耗的,速度V线性消耗的,V是常数。(3)库存的补货时间远远小于周期运行时间,在此忽略不计。(4)库存的补充间隔时间大于等于Milk-run系统的周期时间,记为T。(5)为了应对生产波动需要设置安全风险系数γ,增加安全库存量来应对可能的风险。Milk-run线边库存模型一次补充量P必须满足T时间内生产线的消耗,其物料的安全库存量设置为:

Intel Quantum Simulator(IQS)[53]是Intel 推出的C++量子模拟器,前身为qHiPSTER,其提供了高性能计算功能,可支持用户通过超级计算机进行模拟。

量浆[54]是百度推出的量子模拟器,其支持量子神经网络的搭建和训练,提供了多个量子机器学习案例,如量子近似优化算法(QAOA)、变分量子特征求解器(VQE)、量子神经网络的贫瘠高原效应(Barren Plateaus)、量子分类器(Quantum Classifier)等。

目前,量子模拟器属于NISQ 模拟器,在未来几年,提升量子比特数、优化量子模拟器、构建模拟器上层软件将成为量子模拟器的研究热点。

4 基于超算集群的量子计算模拟

超级计算机集群为量子计算的模拟提供了硬件平台,基于超算集群的量子计算模拟主要涉及以下2 项影响性能的关键问题:

1)任务拆分。任务拆分即拆分量子线路为多个子线路,并将其分配至不同的节点进行计算。任务拆分的目的是利用超算集群的运算性能来应对量子计算模拟带来的海量存储和计算资源开销问题。合适的任务拆分策略可协助提升模拟性能,缩减节点间通信开销,允许更多任务被拆分为子任务并行计算,充分利用超算集群的并行处理能力。

2)通信优化。通信优化涉及2 项优化内容:节点间通信次数以及单次通信传输数据量(单次通信开销),这2 项优化内容之间亦可进行权衡。不合理的通信策略可能造成节点间带宽拥堵、通信延时增加、节点数据饥饿等问题,因此,进行通信优化是提升超算集群运算性能的关键。

下文分别阐述任务拆分和通信优化的代表性工作。

4.1 任务拆分

现有的量子线路拆分方法通常采用分割多线路量子门操作的方式来拆分。拆分一个多线路门操作可生成多个小规模的子线路。将子线路分别执行后的结果进行合并,可得到原线路的执行结果。文献[33]为了能够在经典计算机上模拟更多量子比特,提出了一种“slice”的方法,将原来可能存在纠缠的整个量子线路切割成2 个或多个互不纠缠的子线路,并按照这种方式在IBM Blue Gene/Q 超级计算机上完成了对49 个量子比特、线路深度为27 的量子线路以及56 个量子比特、线路深度为23 的量子线路的模拟,提升了经典计算机所能够模拟的量子程序的规模。

如果在分割时把线路分割成不同的子部分而分割线遇到了CZ 门(见图3(a)),那么必须考虑控制线路对目标线路所有可能的影响。当控制线路1 在当前状态是|0〉时,CZ 门对目标线路2 不产生影响(见图3(b));当控制线路处于|1〉状态时,目标线路则要经过一个Z 门操作(见图3(c))。这样,为了剥离一个CZ 门的纠缠,系统状态在此处便产生了分支,而且使得子线路的个数翻倍。

图3 纠缠量子线路分割示例Fig.3 Example of entangled quantum circuit segmentation

假如一个系统在分割前有N条线路,则全概率幅模拟需要的存储空间为2N。应用分割法后产生了2 个各有N/2 条线路的系统,这个系统的存储空间约等同于2×2N/2个量子比特。如果在分割时分割了n个CZ 门,则最终的空间需求为2×2N/2×2n=2(N/2+n+1)。对于有大量线路的系统,层数较少的模拟的确可以大幅减少内存的需求,但随着层数的增加,所切割的CZ 门数量也会相应增加,降低了使用该方法的优势。最终当n>N/2-1 时,该方法对内存的需求比不分割还要大,从而失去了应用价值。

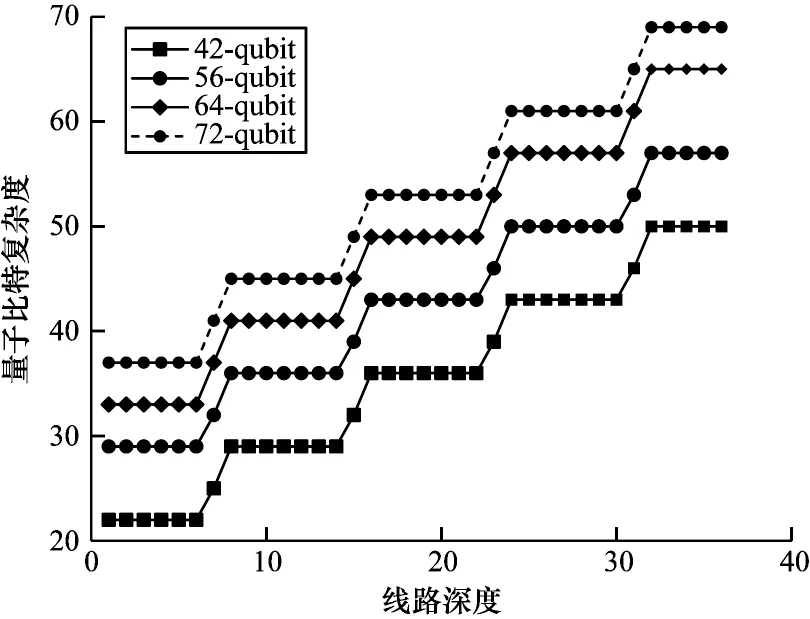

基于上述方法,文献[35]把6×7、7×8、8×8 的量子线路分割成尺寸大致相等的2、3 和4 个部分,并对这些线路进行了多达36 层的模拟。为了衡量线路模拟的困难程度,其定义了一个称为Complexity in qubit的物理量。该物理量实际上等同于需要同样内存大小的未拆分线路的量子比特数,如图4 所示。可以看出,每分割一个CZ 门,系统的子线路个数便翻倍。

图4 线路复杂度随线路深度的变化Fig.4 Variation of circuit complexity with circuit depth

通过理论分析可发现,随着深度的增加,线路复杂度呈单调增长,因为线路会遇到越来越多的CZ门。当所有深度的CZ 门总量接近线路大小的一半时(见上段),该方法就达到了一个临界深度。使用该方法进行超过临界深度的模拟会比不使用更加困难。当线路大小增加时,临界深度也相应增加,因此,该方法适合用于大尺寸少深度的线路。

文献[57]对分割法进行改进,提出了implicit decomposition 分割算法。该算法把线路分成不固定但有类似大小的三部分,分割线会随着线路深度逐渐变化。implicit decomposition 算法对有4 个量子比特的线路的分割情况如图5 所示。其中:A 部分有两条线路,同时也分割了两个CZ 门(门的状态由线路2 上的b1 和b2 决定),因此,A 部分完整的状态需要22×22=16 个概率幅来表示;B 部分本来也同样需要16 个概率幅来表示,但由于线路2 在经过位置b2 后结束,因此该文作者认为b2 的状态必须和线路2 的最终状态一致,所以,B 部分的状态向量可以减少一半的概率幅数。利用以上算法在“太湖之光”上能够模拟7×7 个量子比特的39 层随机线路,此规模已超过了在Blue Gene/Q 机器上同等量子比特数下的27 层模拟,达到了国际领先水平。

图5 implicit decomposition 分割算法示意图Fig.5 Schematic diagram of implicit decomposition segmentation algorithm

线路拆分方式侧重点在于模拟更大的、拥有更多相互纠缠量子比特的线路,其可以达到的深度受多量子门总数的影响。如果一个线路含有较低密度的多量子门,那么该系统中各线路的纠缠程度就会较低,因此,也可以模拟更大深度的量子线路。

4.2 通信优化

在超算集群上进行量子计算模拟时,节点间和存储间存在数据依赖,跨节点和设备的通信无法避免,因此,需要研究计算过程中的数据分布和数据传输方法以降低模拟过程的通信开销。文献[30]研究了量子算法中节点间的数据关联性,针对量子计算每个量子门仿真过程中访问的概率幅数据进行分析,提出一种MPI 进程间每个量子执行前进行的数据交互策略,从而降低节点间数据的关联性,实现数据本地化,使通信频率降低到多项式级。文献[46]研究了异构众核集群环境下的大规模量子计算模拟,提出通过最大化本地执行的量子门数量来降低通信频率的方法,在异构众核架构超级计算机Cori II 上实现了45 量子比特的量子计算机模拟实验。文献[59]为了解决不同GPU 之间的高数据依赖性,利用GPU Direct 技术设计并实现了使用GPU直接P2P 传输的方案,其使用4 块GPU 进行多GPU的量子计算模拟,相较于libquantum 获得了358 倍的加速比,并行效率达到0.92。

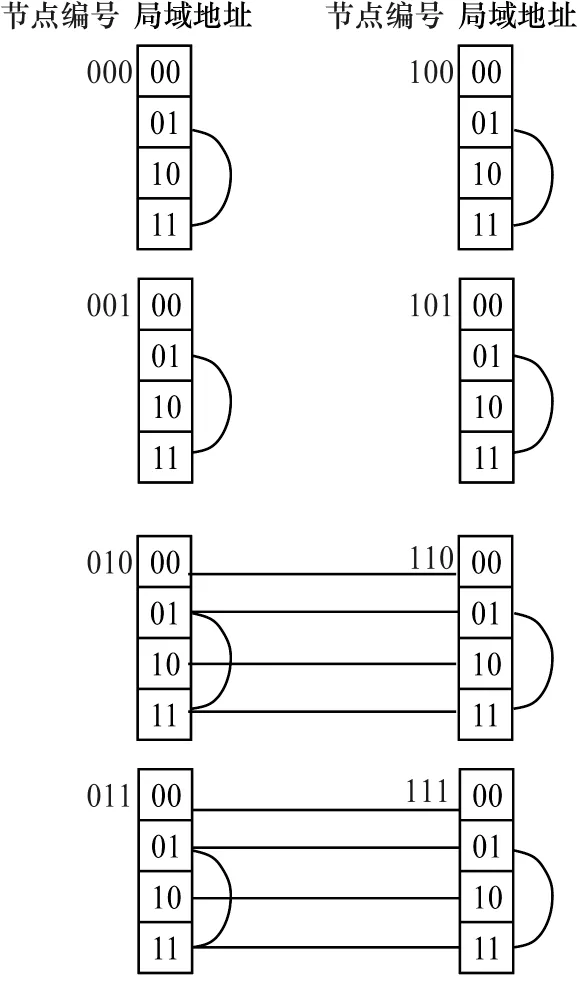

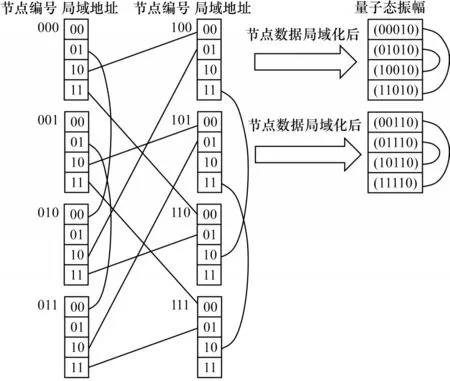

量子比特可以分为本地量子比特、节点内非本地量子比特和节点外非本地量子比特3 类。当量子门作用在非本地量子比特上时,会产生指数级的通信频率问题。假设每个节点的内存空间可容纳L位量子比特的所有概率幅,则模拟N位的量子比特需要2N-L个节点。如果对这些节点进行二进制编码,那么量子态(aN-1…a2a1a0) 的概率幅将存储在(aN-1aN-2…aL+1aL)号节点上的第(aL-1…a2a1a0)号位置,其中,ai∈{0,1}为第i位的量子态。例如,当N=5,L=2 时,系统使用了8 个节点来存储所有概率幅,节点编号为(000)~(111),每个节点存储4 个概率幅,编号为(00)~(11),则量子态(11010)的概率幅就存储在第(110)号节点中的第3 个地址上。

由于所有概率幅分布储存在各个节点上,因此一些门操作可能需要进行节点间通信。以单门H 为例,对第i条线路的单门操作需要更改量子态概率幅(…ai…),此操作需要读取和更新量子态系数(…0i…)和(…1i…)。当i

假如要对第0 和1 位量子做一个CZ 门操作CZ0,1,即把所有A=(***01)的量子态与B=(***11)的量子态相交换(其中,一个*号代表一位量子态,为表达简洁,把a4a3a2化简为***)。由于第0 和1 位是本地量子比特,因此这个CZ0,1操作可以在各节点内快速交换(***01)和(***11)的数据来完成,如图6 所示。另一方面,假如要对第3 和4 位的全局量子比特进行CZ3,4操作,那么概率幅C=(01***)和D=(11***)互换的操作就需要跨节点进行(此处***为a2a1a0),并要利用MPI 实行8次数据交换,运算时间要比CZ0,1长得多。如图7所示:当进行CZ0,1操作时,节点内进行1 次信息交换,交换位置由曲线标出;当进行CZ3,4操作时,节点间进行8 次信息交换,交换位置由直线标出。

图6 一个使用8 个节点储存5 个量子比特的系统示意图Fig.6 Schematic diagram of a system using eight nodes storing five qubits

图7 数据本地化示意图Fig.7 Schematic diagram of data localization

CZi,j是一种比较简单的操作,因为其数学表达矩阵只有4 个非零系数。对于一些比较复杂的门操作,例如XX Ising 门,所有存储(00***)量子态概率幅的节点需要和存储(11***)的节点通信,存储(01***)和(10***)的节点也互相通信,共16 次。如果不对算法进行优化,全局量子位的计算将会变得很缓慢。

利用数据本地化的原理,可以把需要模拟的量子位从全局位置移至本地位置,移动后在节点内的内存中进行运算,从而大幅节省时间开销[59]。

假设节点内存可容纳的量子位数L不小于需要模拟的位数,以3、4 位的XX Ising 门为例,把第3、4 位量子比特的数据与第0、1 位互换,即:(00*01)与(01*00)互换;(00*10)与(10*00)互换;(00*11)与(11*00)互换;(01*10)与(10*01)互换;(01*11)与(11*01)互换;(10*11)与(11*10)互换。这6 组互换中的每一组实际包含了2 次互换,共12 次,少于优化前所需的16 次数据通信量。交换后,所有(**a2a1a0)数据都存储在编号为(**a1a0a2)的节点内,各节点可以同时并行地执行门操作。

由图7可以看出,经过12次数据交换后,第3、4位量子比特的概率幅(**a2a1a0)将会存储在同一节点(a1a0a2)内,图中右边部分给出了经交换后节点(100)和(101)所存数据对应的量子态概率幅。操作完毕后,再根据下一个门所模拟的线路编号进行下一次的数据本地化,以此类推。

以此系统(N=5,L=2)为例,数据本地化方法能够把任意复杂的双量子门操作降低至12 次数据互换,而对于一些非常简单的门操作,直接操作可能不需要12 次数据互换,这需要算法在模拟中作具体判断。数据本地化还可类推用来优化多量子门操作,详情不在此文展开。

5 结束语

量子计算模拟为量子计算机及量子算法的研究和验证提供了有效的途径。本文介绍量子计算模拟方法的研究进展,对不同方法的设计思路和优缺点进行对比分析,列举目前常见的量子计算模拟器,并对利用超级计算机实现量子计算模拟的优化方法进行讨论。大规模量子计算模拟全部量子态概率幅的方式所需内存资源随被模拟的量子位数指数增加,可模拟的量子位数受到物理内存容量的制约,而部分概率幅模拟方法通过有效降低时间复杂度和空间复杂度,计算效率比全概率幅模拟方法更高,且在模拟过程中考虑线路的分割和数据的本地化,能够在节点内用更少的时间并行完成门操作计算。此外,为实现量子计算的大规模实用化,纠错、容错技术也同样需要发展。

目前,量子计算模拟在算法和工程上仍有很大的优化空间。在算法方面,张量网络缩并的顺序极大地影响计算效率,未来可探索更优缩并顺序算法;在工程方面,需要应用张量运算来充分发挥硬件性能,进一步减少线路模拟所需的时间。同时,可扩展性和容错也将是未来量子计算研究中的关键问题。