舰载膛内多参数微型弹载记录仪的设计

王 帅,李 杰,张德彪,江 杰

(中北大学 仪器科学与动态测试教育部重点实验室,太原 030051)

0 引言

近年来,我国国防事业日益强大,走进国防现代化改革的关键时期,其中舰艇是海军的核心力量,在以驱逐舰为代表的各类大型舰艇中,主炮承担主要毁伤与护卫的任务。在实战演习或执行特殊任务的场景中,连续高频发射制导导弹的过程中,主炮膛承受巨大压力,高频短时的高温高压的发射瞬间对于弹体与炮膛都存在一定程度的影响。其膛内瞬时多参数测量是整体舰载火炮系统技术迭代的关键与前提,其中数据采集存储系统超高速、高精度、大容量地获取目标数据在动态测试系统就得到了非常广泛的应用。

目前的数据采集存储系统主要分为两种方式:遥测采编和记录仪存储。但是由于弹载高冲击高旋的恶劣环境,遥测采编模块需要通过发射天线以一定的波段的频率进行数据传输,地面遥测接受站通过接收天线对数据进行实时接收存储,这种方案收到环境因素的影响较大,这种方案在大量弹药智能化改造的进程中设计成本高昂。测试过程基本集中在毫秒级测量,无线传输方案在速率方面也存在一定的局限性[1]。所以本文采用更加切合实际使用场景的弹载记录仪方案,这种方案具有可以最大限度地满足小型化、低功耗、电路结构适应性强的要求,实现对多通道模拟信号的前端滤波、信号调理、中端完整采集、编码、存储,以及后端对数据的验证解算,从而实现高速高精度的数据采集[2]。

1 弹载记录仪总体设计原理

弹载记录仪系统主要分为传感器矩阵、信号调理电路、高速模数转换电路、FPGA (field programmable gate array)控制电路,eMMC(embedded multi media card)存储电路、SRAM(static random-access memory)缓存模块、422数字量通信接口电路、USB上位机通讯模块以及内部供电网络模块。

系统级设计如图1所示。

图1 系统级设计框图

其中系统供电网络采用7.4 V-500 mAh的锂电池通过级联降压的方式进行电压转换,以便于为各电路子模块和前端传感器矩阵供电[4-5]。分布在弹体各部位传感器产生的激励信号经过高频50 R阻抗的SMA(sub miniature version-A)接口将LVDS(low voltage differential signaling)低压差分信号传输网络传输进弹载记录仪,通过信号调理电路进入高速数模转换器。提供数字信号的传感器通过422接口电路以115 200的波特率发送进FPGA,FPGA采用80 MHz的时钟控制数据流经过1个深度为2 K的异步FIFO(first in first out)缓存后再通过100 MHz的时钟控制SRAM进行缓存,再经过1个深度为4 K的异步FIFO完成跨时钟域的采编写入eMMC存储模块[6]。待试验结束后,通过数据读取设备通过USB模块和上位机软件通讯[7-8],将弹载记录仪中的数据读取至上位机。最后通过数据处理软件进行相关传感器的数据处理分析获得相应的试验参数。

为满足舰炮连续射击时膛压以及出膛最高转速对炮口以及弹体飞行姿态的影响。传感器矩阵在系统中布局如图2所示。

图2 传感器矩阵布局图

2 硬件电路设计

2.1 传感器与信号调理模块

ICP(integrated circuits piezoelectric)传感器即为集成电路传感器。其中自身集成了压电传感器,运算放大器以及偏置电路,但是不能直接输出模拟信号给模数转换芯片进行采集,必须建立在恒流源稳定供电环境的基础上,才可以将其信号调理成稳定模拟信号[9-11]。由于该类型传感器集成度高,显著提高测试精度,具有极强的抗干扰能力,信噪比高,同时可以有效缩减外部电路所占面积,缩小整体系统体积,获得更好的抗冲击过载能力[12]。ICP加速度传感器需要相关的外围调理电路如图3所示。

图3 ICP传感器信号调理框图

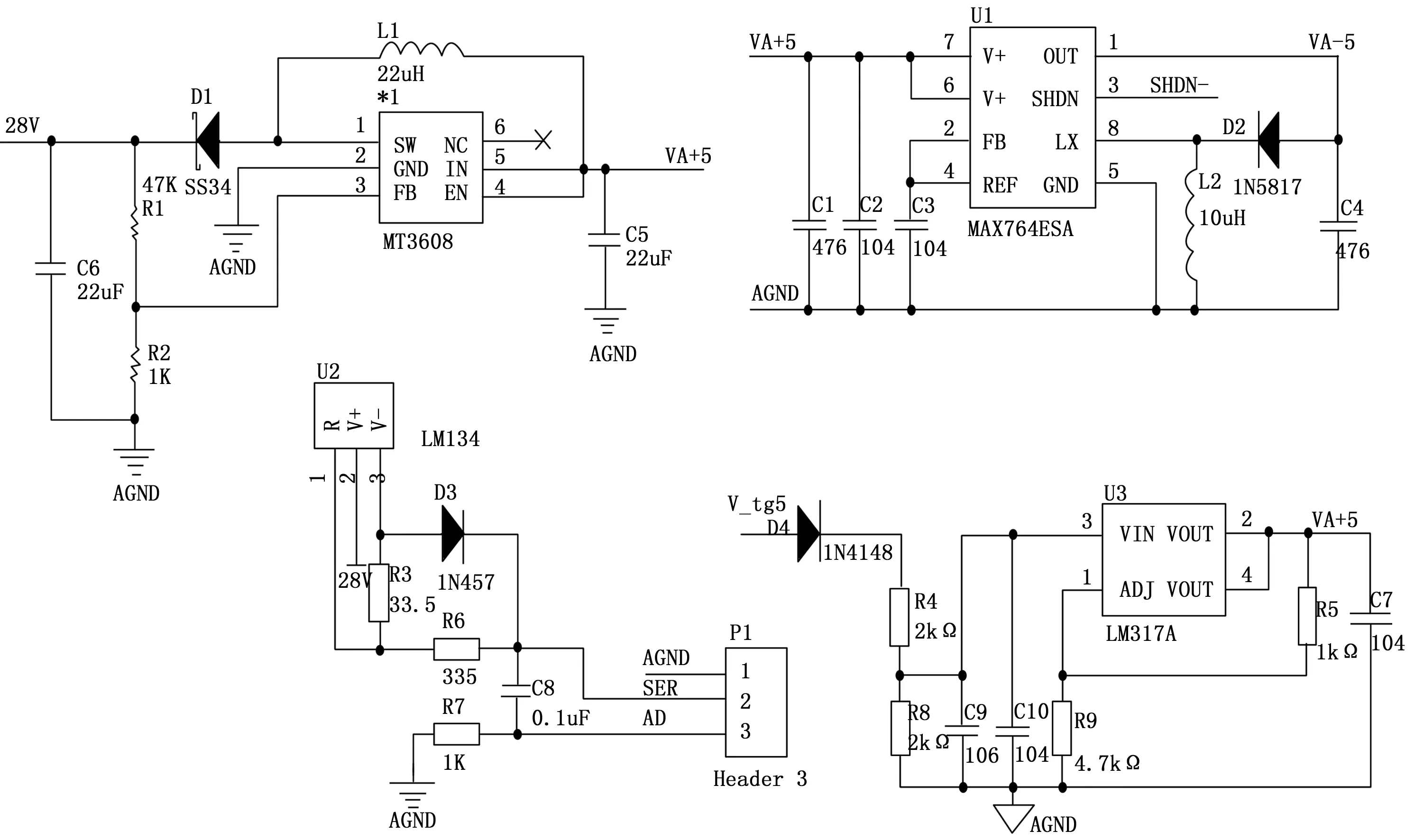

通过DC-DC芯片对基本电源网络进行级联升压处理,给恒流源输出28 V稳定电压为ICP传感器供电。并且通过LDO(low dropout regulator)低压差线性稳压器为其余配置电路进行有效输出。负电压转换电路为程控放大器和偏置电路提供有效工作负电压。最后通过电容与电阻搭建的一阶无源低通滤波电路[13-14]。对于ICP传感器模拟量信号的调理模块电路的原理如图4所示。

图4 信号调理模块电路原理图

2.2 模数转换模块设计

记录仪需要具备同时采集多路高频传感器信号的能力,对于数模转换芯片的要求极高。为了保证采样速率、采样精度、输入带宽,真实还原发射过程中的膛压波形,ADC(analog-to-digital converter)的采样速率应该大于采样信号频率的10倍以上[3]。本设计选用AD9230。该款芯片功耗低,在LVDS DDR mode模式中250 Msps的采样率,功耗只有400 mW。带宽为700 MHz,分辨率为12 bit,可以满足本设计的前端采样需求[15]。通过SMA接口将LVDS信号传输进模拟信号网络可以极大地提升信号完整性以及传输信号的稳定性,可以有效地克服适应舰炮中的恶劣环境带来的影响[16]。

模数转换芯片AD9230的具体工作电路原理如图5所示。

图5 AD9230工作原理图

2.3 eMMC存储模块设计

eMMC存储系统相较于传统的NAND Flash存储器,在其内部集成了一个Flash控制器,其中包括了数据传输协议,Flash读写擦操作,坏块管理,ECC(error correcting code)校验,电源及时钟管理等功能[17]。同时也具有更快的读写速度。eMMC存储系统基本工作原理如图6所示。

图6 eMMC存储系统基本工作原理图

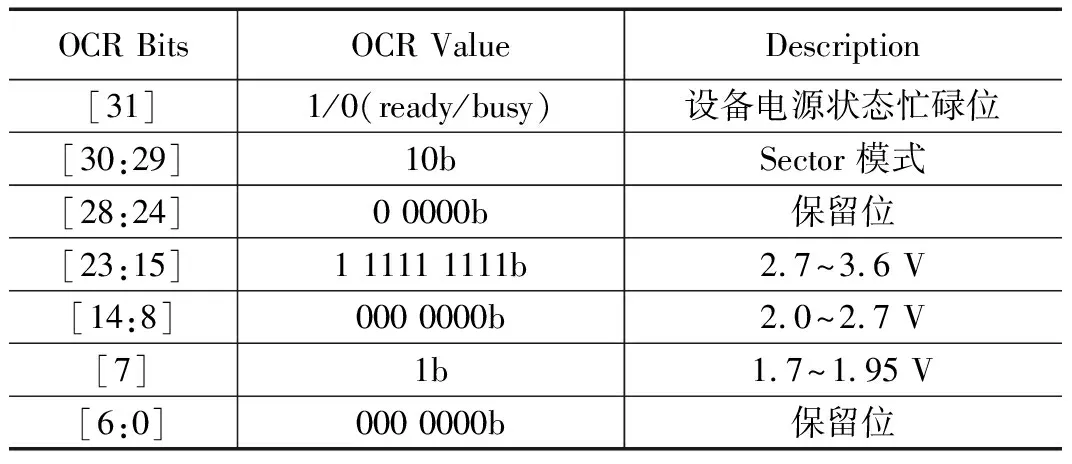

由于系统整体采样率很高,所以在eMMC存储系统中我们选定的HS400模式,在HS400的模式下,通过IP核生成eMMC工作时钟200 MHz,理论上最大可达到400 MB/s的传输速率,但是由于系统内部存在发送接收的不可避免时钟延迟,所以对于Flash的数据写入速率达不到预定的400 MB/s,此时需要在存储系统内部集成一个SRAM缓存单元。SRAM不需要刷新电路就可以保持内部数据,而且只要不掉电,就可以一直保持[18]。

eMMC的工作原理如图7所示。

图7 eMMC存储系统原理图

3 软件程序设计

3.1 模数信号采集

AD9230输出端的采用的是全差分输出,但是FPGA内部无法直接处理全差分信号,所以需要调用FPGA内部提供的原码将全差分信号转换为单端信号。IBUFGDS模块即为内部的差分输入缓存器[19],实现的输入输出关系如表1所示。

表1 IBUFGDS模块输入输出关系

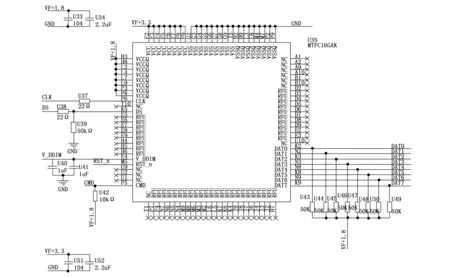

验证ADC模数采集模块程序时序的正确性,用程序仿真软件对该程序进行时序仿真,sys_clk为经由差分时钟转换后的单端时钟信号,ad_data为AD9230输出的数字信号,如图8所示。

图8 AD9230时序仿真图

3.2 eMMC存储

在整体系统上电后,eMMC也同样需要整体复位初始化,其中需要完成器件识别、器件模式判断与相关状态寄存器的配置等操作。在系统收到FPGA发送出的系统复位信号即CMD0(参数为0x00000000)或者硬件复位信号时,进入IDLE空闲状态,随后配置相关寄存器。

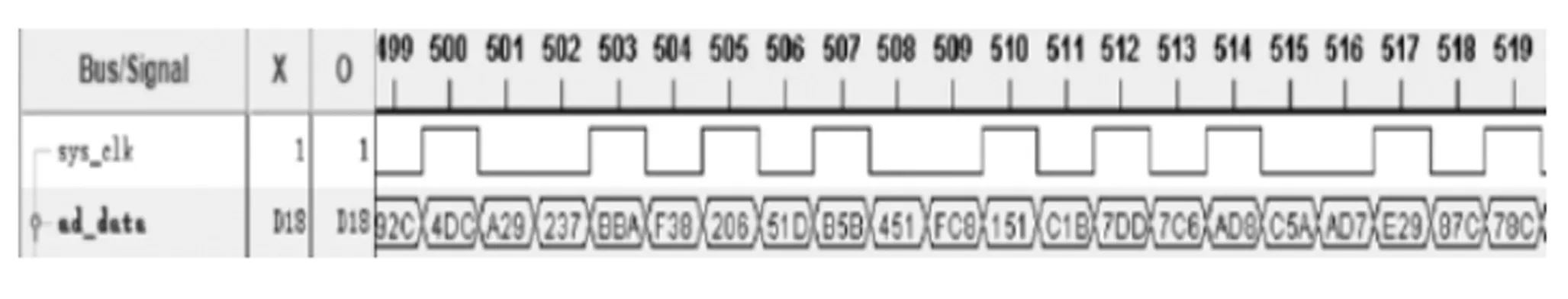

eMMC存储系统ORC寄存器中包含电压配置文件、访问模式指示和状态信息位。

表2 OCR寄存器参数配置

初始化完成后,设备会先进入兼容速率模式(back compatible mode),需要通过控制器发送指定的命令才能进行高速模式的选择与切换,并且需要先进入HS200后,再将eMMC存储系统设置为高速的HS400模式,以实现对模数转换模块采集到的数据进行高速传输与存储[20]。命令指令流程如图9所示。

图9 HS400模式选择流程图

进入HS400模式后,此时eMMC进入Transfer模式,这个模式下已经可以开始对器件进行读取、写入、擦除操作。eMMC存储设备与控制器建立新的数据传输与时钟逻辑关系。如图10所示。

图10 HS400模式下控制器与eMMC设备原理框图

软件复位或硬件复位后,设备均为SDR传输模式,当eMMC控制器判断到设备已经达到HS200或者更高速模式,并支持DDR模式后,可以在设备中启用DDR传输模式。通过设置寄存器EXT_CSD[177]将设备切换到DDR模式,控制器使用SWITCH命令将0x06(8-bits)写入寄存器EXT_CSD的Modes段中的BUS_WIDTH[183]。当设备切换到HS400模式时,HS_TIMING[3:0]也应设置为0x3(4-bits)。

这里我们提到的寄存器EXT_CSD是扩展设备特定数据寄存器(extended device-specific data register)包含设备功能和所选模式的信息,一共有512bits宽度,低位的192bits可以通过SWITCH命令改变寄存器里的配置信息,高位的320bits是设备固有属性无法更改[21]。

数据均以512 bytes的数据包的形式在每个时钟上升沿进行传输的。在系统进入HS400&8bits-DDR模式,接收到写入命令后,需要在EEPROM内读取上次写入eMMC的数据地址,实现续写操作,然后在输入新的地址位,发送CMD25确认当前地址位然后发送512 bytes的数据包,通过CRC16校验后才能通过数据总线。写入操作流程如图11所示。

图11 eMMC存储系统写入操作

同时为了避免数据在传输中出现错帧漏帧的现象,FPGA将对命令响应和数据包进行校验,需要在每个48 bits命令前面附上起始位0,方向位1(指从控制器FPGA到eMMC存储器方向),中间38位是具体命令内容,后面要附上CRC7校验码和结束位1[22-23]。

对应的48 bits响应的格式正好相反,第0位是结束位为1,第1~7位为CRC7的校验,中间38位是响应内容,第46位是方向为0(指从eMMC存储器到控制器FPGA方向),第47位为起始位0。但是其中访问CSD寄存器和CID寄存器的返回响应是136 bits的,响应结构相同。CRC7的计算方法如下式所示:

G(x)=x7+x3+1

M(x)=(firstbit)×xn+(secondbit)×xn-1…+

(lastbit)×x0

(2)

CRC[6:0]=Remainded[(M(x)×x7/G(x)]

(3)

每个数据包前附上起始位00,中间是数据包,后面附上CRC16校验码与结束位1。起始位在时钟的上升沿和下降沿都可以判断,但是结束位只能在时钟上升沿判断。

CRC16校验码的计算方法如下式:

G(x)=x16+x12+x5+1

M(x)=(firstbit)×xn+(secondbit)×xn-1…

(5)

CRC[15:0]=Remainded[(M(x)×x16/G(x)]

(6)

4 试验解算分析

为确保数据采集存储的正常功能实现,以及数据采集的精度,用信号发生器为8个数据采集通道提供3 Vpp,100 Hz的标准正弦波信号。系统正常工作结束后,使用USB3.0接口将数据导出至上位机,在通过数据处理软件将各个通道的数据按照前期的编帧进行分离,画出每个通道的波形图像,如图12所示。系统采集的波形与信号发生器的输出波形基本一致,波形平滑,没有丢帧错帧现象,检测点电压为2.999 V,误差仅为1‰,此误差主要来源于信号调理电路中的运算放大器与模数转换芯片的精度,此误差在设计合理范围之内。

图12 采集信号发生器波形

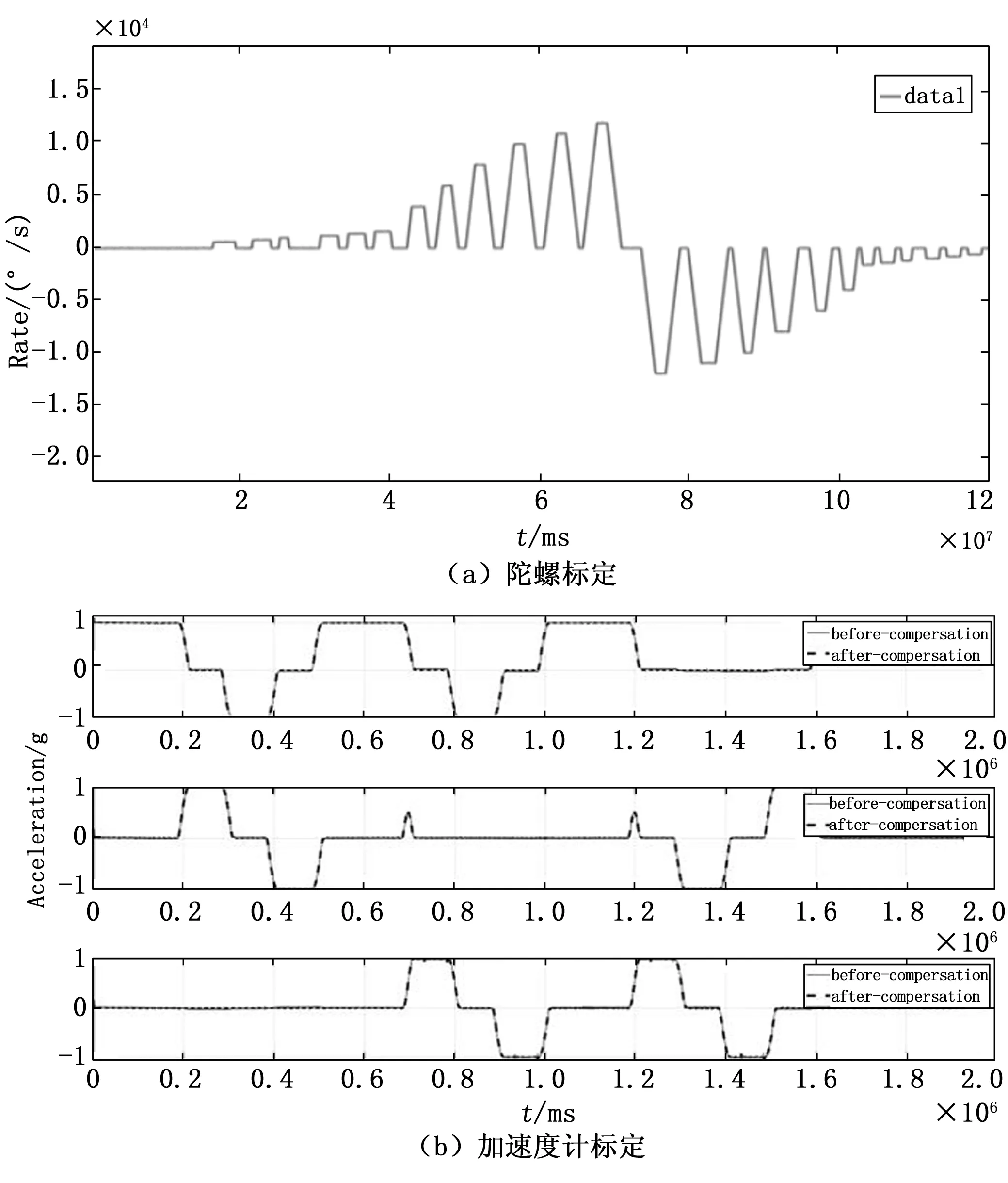

在采集存储功能论证通过后,接入ICP压电传感器与高精度陀螺仪,进行系统集成灌封防护工作,如图13所示。前期功能性验证都以实验室理想信号环境进行,在进行系统集成的过程中必定会引入一些不可避免的误差,比如传感器输出轴与载体坐标系同轴度误差,三轴传感器输出轴不正交误差。这些系统误差占比总误差的90%以上,可以通过系统标定有效提高系统整机精度与数据真实性。

图13 系统集成与整机标定

标定试验后数据的处理,如图14所示。系统经过传感器器件级标定以及整机标定试验后,通过数据处理软件完成对试验数据的解算,得到相关的标定因数、零偏系数与拟合曲线。对系统整体的零偏稳定性、零偏重复性、传感器线性度与交叉耦合误差有了一个准确的误差模型[11]。消除在系统集成过程中引入的系统误差,提高系统整体的传感器数据的采集精度,满足系统整体的精度需求。

图14 系统级误差补偿

在整体方案论证通过后,本设计实际运用在实弹环境下的常规弹药击发出膛过程膛压过载连续动态特性的测量试验中,并且表现良好。得到实弹数据如图15所示。

图15 试验数据

将实验数据导出后,可见记录仪中原始数据在用EB F4帧头对齐后,数据整齐,无乱码错码现象,用数据处理软件对数据进行处理画图。以时间为横坐标 (ms),过载冲击为纵坐标(g),得到膛压过载曲线,如图16所示。

图16 膛压过载曲线

可见在图16中的9.14×105ms时炮射弹药击发,测得一段不到40 ms的膛压曲线,正向峰值约为28 000 g,与高速相机的实时高速摄像的结果进行验证,出膛时间与记录仪完全符合。此测量值已经通过信号调理模块前端低通滤波,去掉ICP传感器频率响应之外的高频机械谐振噪声。符合理论参数计算结果范围,证实此段冲击曲线为有效数据。满足试验任务需求。

以时间为横坐标(ms),角速率为纵坐标(°/s),得到弹体角速率曲线,如图17所示。

图17 弹体角速率曲线

可见在图17中的9.14×105ms时刻炮射弹药击发,膛内极端时间加速至极快转速约为9 000°/s,炮口出膛后10 ms,弹体展开尾翼,迅速稳定飞行姿态降低弹体转速,开启相关制导系统。

5 结束语

本文设计了一款基于FPGA、高速A/D芯片与eMMC存储系统的高速高精度弹载数据记录仪。实现在舰载舰炮膛内狭小恶劣环境下8路40 MS/s采样率的模拟信号,2路数字信号采集,以及250 MB/s的数据存储。经过实践检验,在28 000 g的强冲击下有效记录数据,隔离MEMS陀螺仪的冲击短时失效现象,可靠性强,整体静态功耗低,数据误差小,满足测量膛内恶劣环境短时间多参数多通道的设计要求。